# The CBM Silicon Tracking System front-end electronics

from bare ASIC to detector characterization, commissioning and performance

Dissertation zur Erlangung des Doktorgrades der Naturwissenschaften

vorgelegt beim Fachbereich Physik der Johann Wolfgang Goethe-Universität in Frankfurt am Main

> von Adrian Rodríguez Rodríguez aus Pinar del Río, Kuba

Frankfurt am Main (2019) (D 30)

| vom Fachbereich Physik der<br>Johann Wolfgang Goethe-U |                                                                                       |

|--------------------------------------------------------|---------------------------------------------------------------------------------------|

|                                                        |                                                                                       |

|                                                        | niversität als Dissertation angenommen                                                |

|                                                        |                                                                                       |

|                                                        |                                                                                       |

| Johann Wolfgang Goethe-U                               | niversität als Dissertation angenommen                                                |

| Johann Wolfgang Goethe-Un                              | niversität als Dissertation angenommen Prof. Dr. Michael Lang Prof. Dr. Alberica Toia |

# Contents

| $\mathbf{A}$ | bstra | $\operatorname{\mathbf{ct}}$                                            | 1              |

|--------------|-------|-------------------------------------------------------------------------|----------------|

| K            | urzfa | ssung                                                                   | 4              |

| 1            | Intr  | roduction                                                               | 7              |

|              | 1.1   | The Standard Model                                                      | 7              |

|              | 1.2   | Quark Gluon Plasma (QGP)                                                | 9              |

|              | 1.3   | The study of the QCD phase diagram                                      | 9              |

|              | 1.4   | High baryon density at low temperatures in the cosmos                   | 11             |

|              | 1.5   | Probing QCD matter with heavy ion collisions                            | 12             |

|              | 1.6   | Motivation and scope of this work and thesis outline                    | 13             |

| 2            | The   | CBM experiment and the Silicon Tracking System                          | 15             |

|              | 2.1   | The future FAIR facility                                                | 15             |

|              | 2.2   | The physics program of the CBM experiment                               | 16             |

|              | 2.3   | The CBM experimental setup                                              | 20             |

|              | 2.4   | The Silicon Tracking System: challenges and design                      | $\frac{1}{24}$ |

|              | 2.5   | The STS module as a functional unit                                     | 26             |

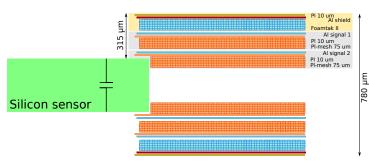

|              |       | 2.5.1 Silicon sensors and microcables                                   | 26             |

|              | 2.6   | The STS readout chain                                                   | 28             |

|              |       | 2.6.1 Front-end electronics (FEE)                                       | 29             |

|              |       | 2.6.2 Readout board (ROB)                                               | 30             |

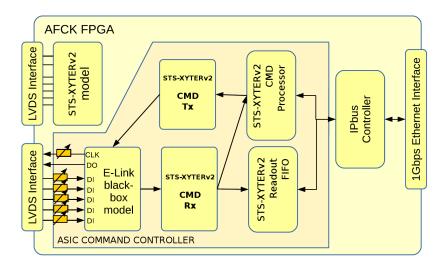

|              |       | 2.6.3 Common readout interface (CRI)                                    | 31             |

|              |       | 2.6.4 First Level Event Selector (FLES)                                 | 32             |

|              | 2.7   | Challenging physics observables                                         | 32             |

|              | 2.8   | Performance simulations of the STS detector                             | 34             |

|              |       | 2.8.1 Tracking reconstruction efficiency and momentum resolution        | 34             |

|              |       | 2.8.2 Potentialities for particle identification using the STS detector | 35             |

|              |       |                                                                         |                |

| 3            |       | aracterization of the front-end electronics for the STS                 | <b>37</b> 37   |

|              | 3.1   | Requirements for the front-end electronics of the STS                   |                |

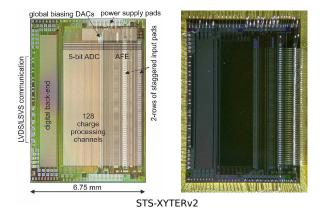

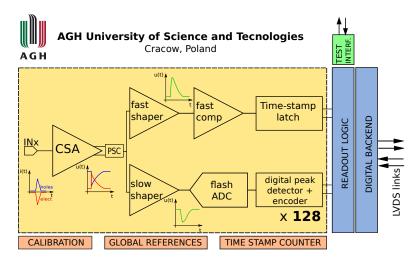

|              | 3.2   | General description of the STS-XYTERv2 ASIC                             | 38             |

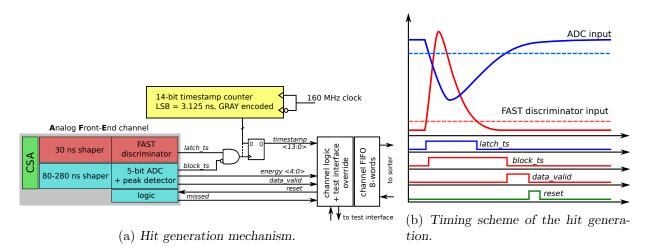

|              | 3.3   | Hit generation mechanism                                                | 40             |

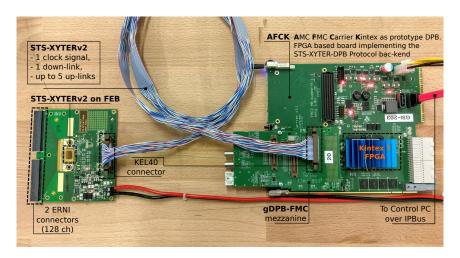

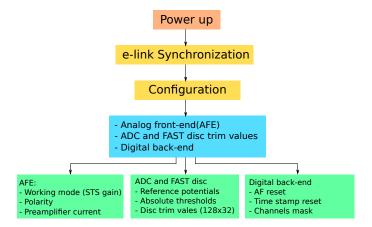

|              | 3.4   | Operation of the STS-XYTERv2 in a prototype readout chain               | 41             |

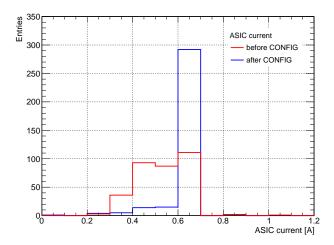

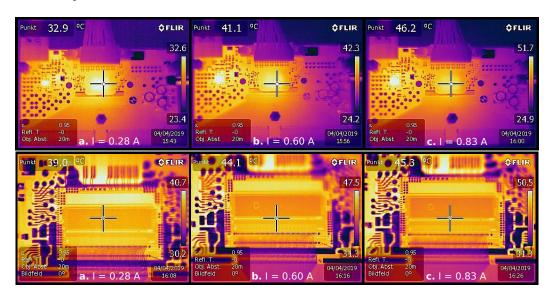

|              | 3.5   | ASIC operation and power consumption                                    | 42             |

|              | 0.0   | 3.5.1 Thermal behavior and monitoring tools                             | 43             |

|              | 3.6   | Characterization of the analog front-end (AFE)                          | 45             |

|              |       | 1 &                                                                     | 46             |

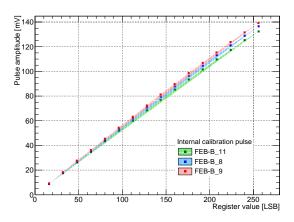

|              |       | 3.6.2 Linearity check for the internal pulse generator                  | 46             |

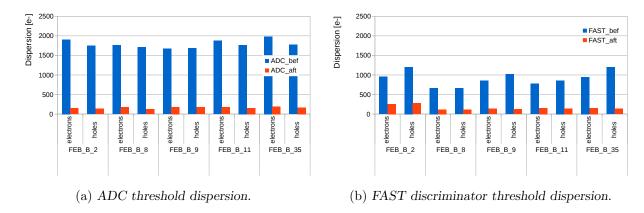

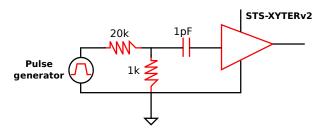

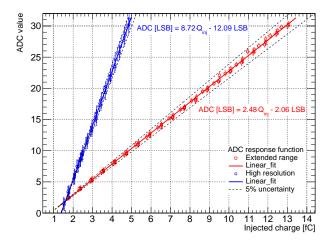

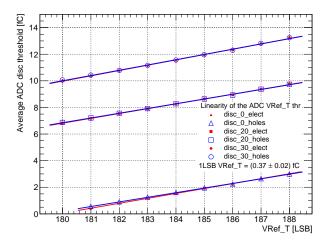

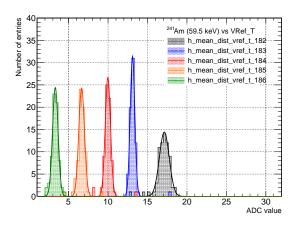

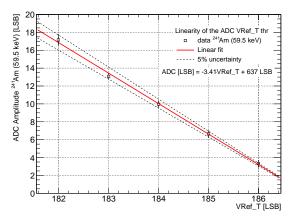

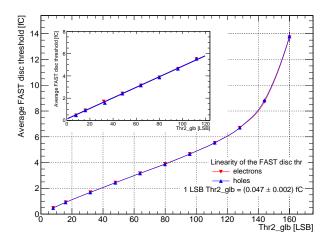

|   | 3.7  | Develop   | pment of a procedure for amplitude and time calibration                   | 18 |

|---|------|-----------|---------------------------------------------------------------------------|----|

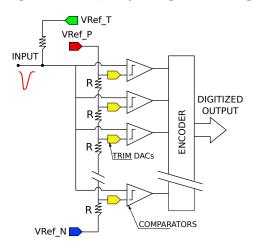

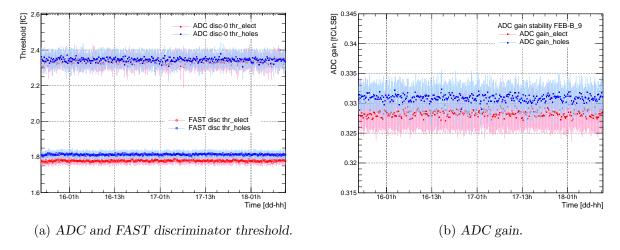

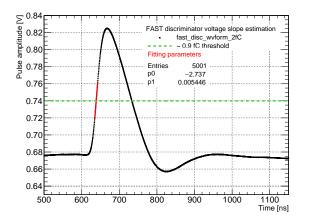

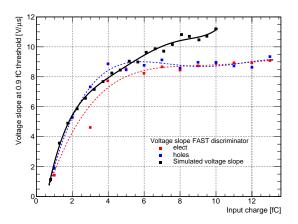

|   |      | 3.7.1     | The flash ADC and FAST discriminator in the STS-XYTERv2 ASIC 4            | 18 |

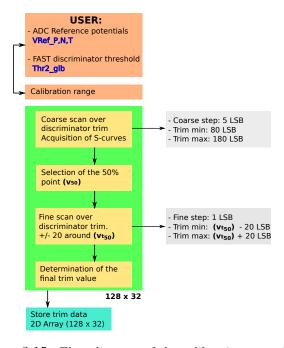

|   |      | 3.7.2     | Description of the calibration procedure                                  | 50 |

|   |      |           |                                                                           | 50 |

|   |      |           |                                                                           | 52 |

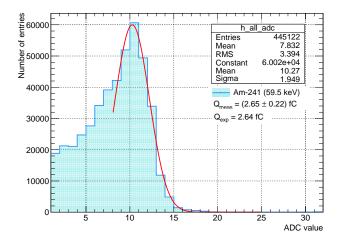

|   |      |           | Validation of the ADC calibration using an external pulse generator and a |    |

|   |      |           | gamma source                                                              | 55 |

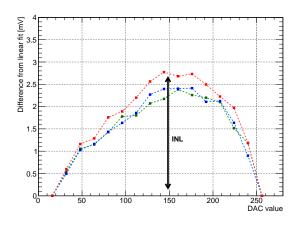

|   |      | 3.7.6     | ADC and FAST discriminator threshold linearity                            | 56 |

|   |      |           |                                                                           | 59 |

|   | 3.8  |           | · ·                                                                       | 30 |

|   | 3.9  | _         | ,                                                                         | 32 |

|   |      |           | ·                                                                         | 33 |

|   |      |           |                                                                           | 36 |

|   |      |           |                                                                           | 38 |

|   |      |           | 9 . 9                                                                     | 70 |

|   |      |           |                                                                           | 72 |

|   |      |           |                                                                           | 73 |

|   |      |           |                                                                           | 73 |

|   |      |           |                                                                           | 75 |

|   | 3.10 |           | ary                                                                       |    |

|   | 0.10 | Samme     | ~~,                                                                       |    |

| 4 | Rac  | liation 1 | hardness studies of the STS-XYTERv2 ASIC                                  | 7  |

|   | 4.1  | Phenon    | nenological description of radiation damage in integrated circuits        | 77 |

|   |      | 4.1.1     | Total irradiation dose                                                    | 78 |

|   |      | 4.1.2     | Single Event Effects                                                      | 30 |

|   | 4.2  | Radiati   | ion hard design of the STS-XYTERv2 ASIC                                   | 31 |

|   | 4.3  | Evaluat   | tion of the SEU tolerance in a proton beam                                | 32 |

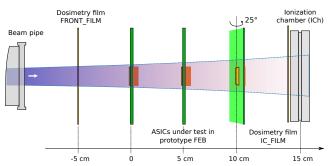

|   |      | 4.3.1     | Experimental setup                                                        | 33 |

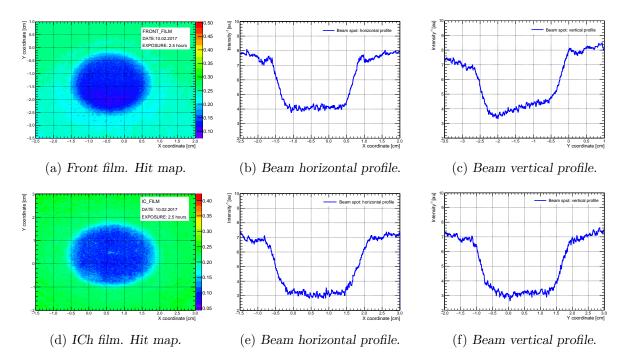

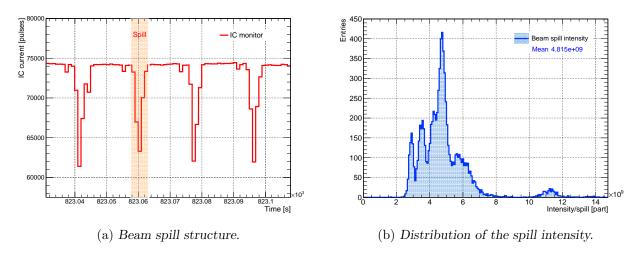

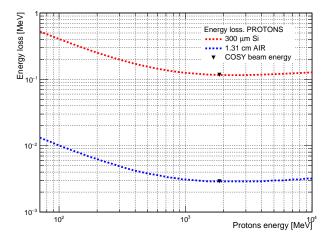

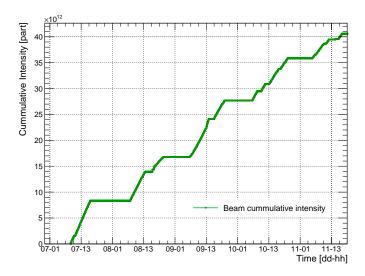

|   |      | 4.3.2     | Beam monitoring system                                                    | 34 |

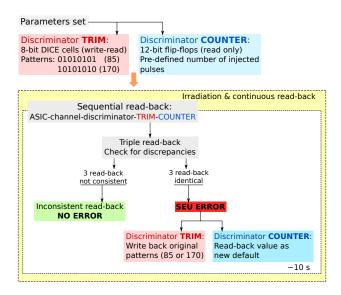

|   |      | 4.3.3     | SEU read-back procedure                                                   | 36 |

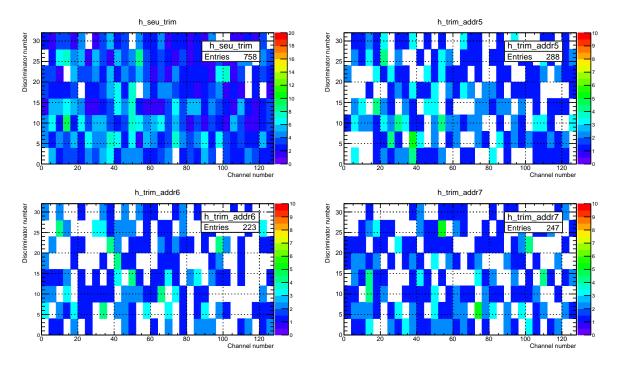

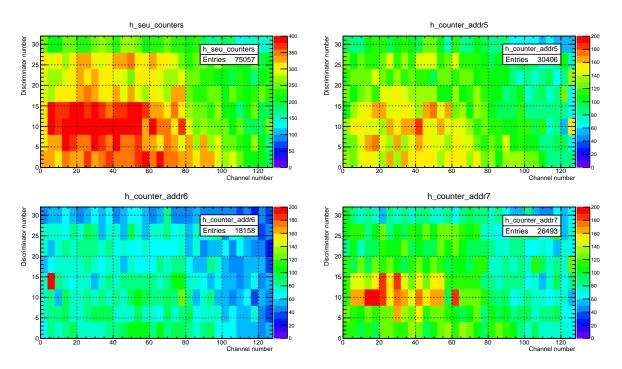

|   | 4.4  | Results   | s of SEU error measurements in the STS-XYTERv2                            | 37 |

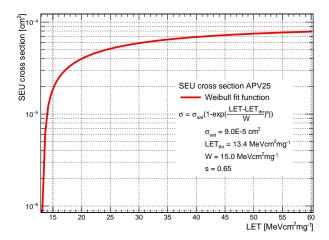

|   |      | 4.4.1     | SEU cross section and uncertainty estimation                              | )1 |

|   |      | 4.4.2     | Radiation environment of the CBM experiment                               | )2 |

|   |      | 4.4.3     | SEU rate in the CBM experiment                                            | )3 |

|   | 4.5  |           |                                                                           | 95 |

|   |      | 4.5.1     | Results from a TID delivered by a gamma irradiation                       | 95 |

|   |      | 4.5.2     | Effect of annealing process on the ASIC response                          | 96 |

|   | 4.6  | Summa     | ary                                                                       | )7 |

|   |      |           |                                                                           |    |

| 5 |      |           |                                                                           | 9  |

|   | 5.1  | _         | mental setup                                                              |    |

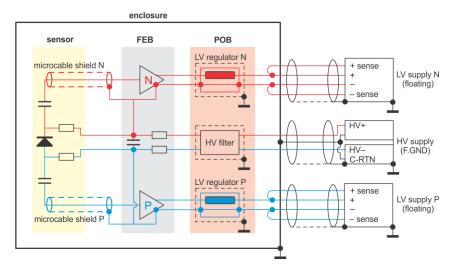

|   |      |           | Filtering and ground scheme                                               |    |

|   |      |           | Readout chain for the STS test modules                                    |    |

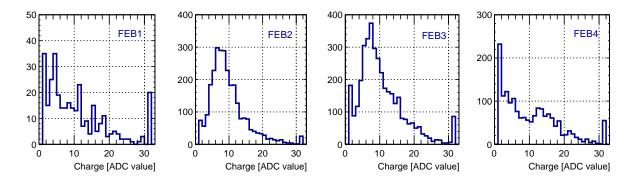

|   |      |           | Results from module calibration                                           |    |

|   | 5.2  |           | cation of a logic error in the STS-XYTERv2                                |    |

|   | 5.3  |           | orrelations with the hodoscope reference signal                           |    |

|   | 5.4  | ·         | noise estimation                                                          |    |

|   | 5.5  |           | ps                                                                        |    |

|   | 5.6  | 0         | readout                                                                   |    |

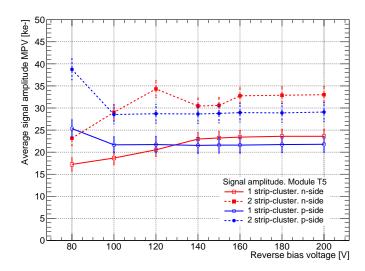

|   |      | 5.6.1     | Signal amplitude dependence with the detector bias voltage                | 4  |

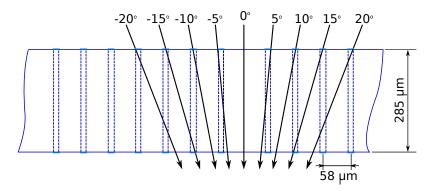

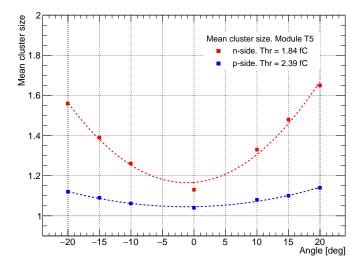

|              | 5.7   | 5.6.2 Angular scan                                      | 116          |

|--------------|-------|---------------------------------------------------------|--------------|

| 6            | Asse  |                                                         | 18           |

|              | 6.1   | The mCBM experiment                                     |              |

|              |       | 6.1.1 mSTS in the context of CBM Phase 0 activities     |              |

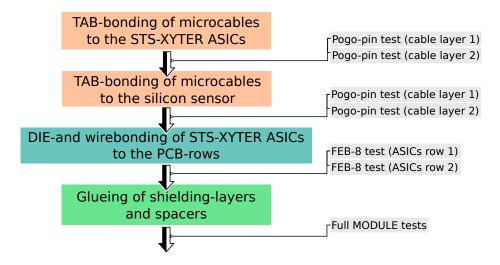

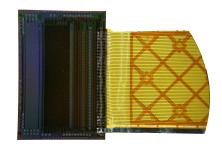

|              | 6.2   | Assembly of the first STS detector modules              |              |

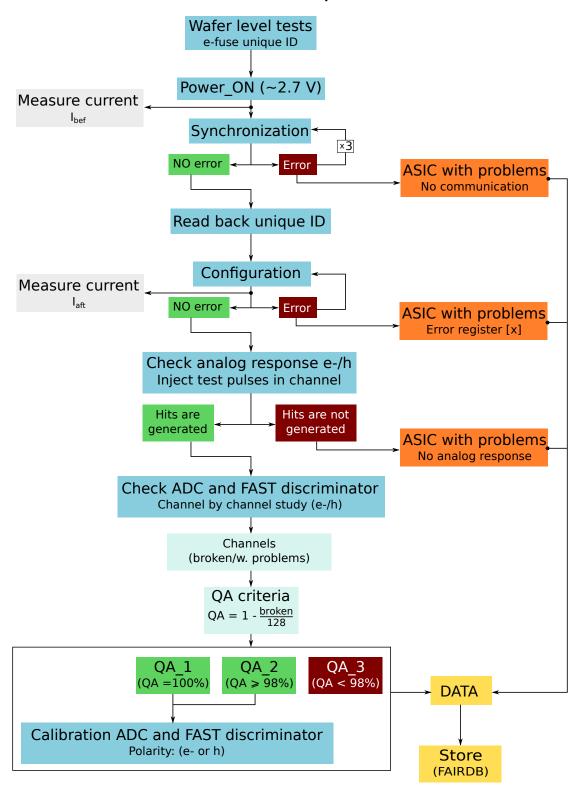

|              | 6.3   | Quality assurance procedures for ASIC testing           |              |

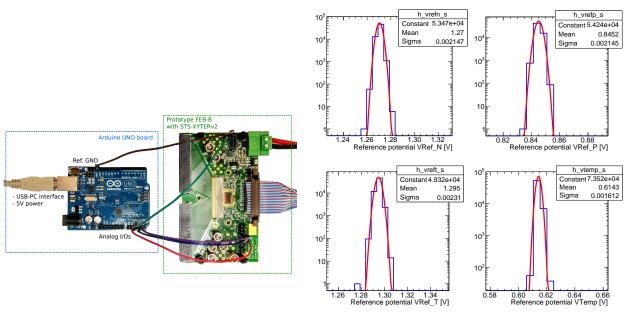

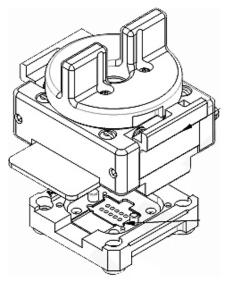

|              |       | 6.3.1 Experimental setup                                |              |

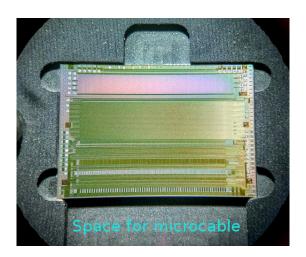

|              |       | 6.3.3 Measurement of microcables                        |              |

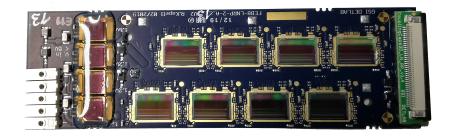

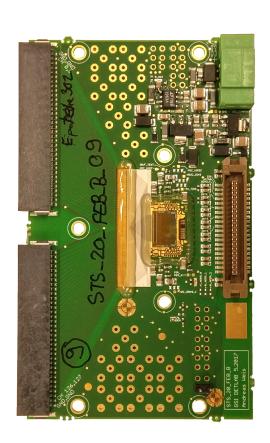

|              | 6.4   | The front-end board FEB-8                               |              |

|              | 6.5   | Test of STS fully assembled modules                     |              |

|              | 0.0   | 6.5.1 Test setup and readout chain                      |              |

|              |       | 6.5.2 Test results                                      |              |

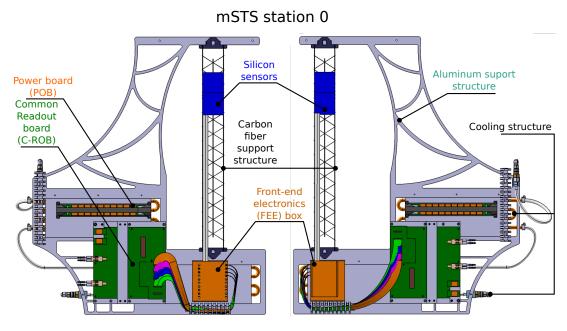

|              | 6.6   | Installation of mSTS                                    | 133          |

|              |       | 6.6.1 mSTS power and grounding scheme                   | 134          |

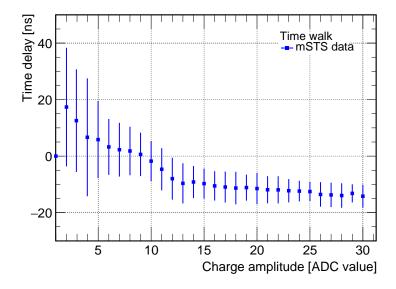

|              |       | 6.6.2 Preliminary results and main findings             |              |

|              | 6.7   | Summary                                                 | 137          |

| Co           | onclu | sions & Outlook                                         | 138          |

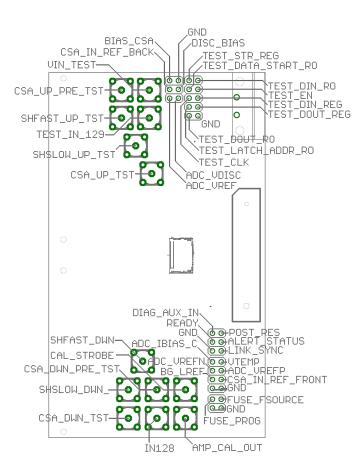

| $\mathbf{A}$ | The   | prototype FEB-B                                         | L <b>4</b> 0 |

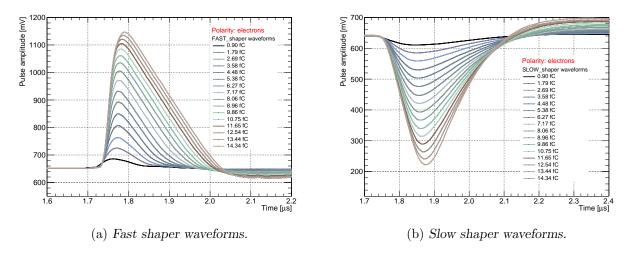

| В            | Wav   | veforms of the STS-XYTERv2 shapers in electron polarity | 41           |

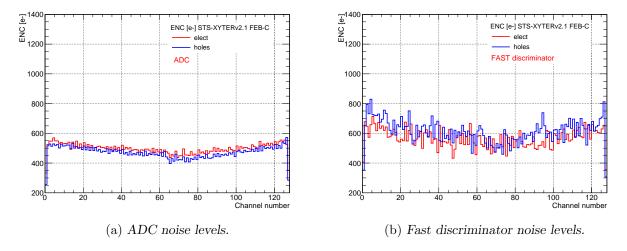

| $\mathbf{C}$ | Mea   | asurements of noise levels for the STS-XYTERv2.1        | 42           |

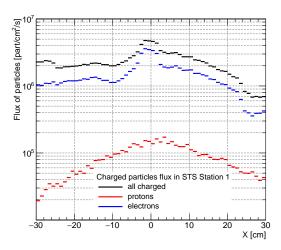

| D            | Cha   | rged particles flux at STS Station 1                    | 43           |

| ${f E}$      | Peri  | formance of prototype module T5                         | 44           |

| Lis          | st of | Acronyms                                                | <b>47</b>    |

| Zu           | ısamı | menfassung                                              | 51           |

| Re           | efere | nces 1                                                  | <b>.</b> 57  |

# Abstract

The last decades have brought tremendous progress in understanding the phase structure of the strongly interacting matter. This has been driven by studying heavy-ion collisions on the experimental side and Lattice QCD, functional approaches to QCD, perturbation theory and effective theories on the theoretical side. Of particular interest is the transition from hadrons to partonic degrees of freedom which is expected to occur at high temperatures or high baryon densities. These phases play an important role in the early universe and the core of neutron stars. Nowadays, the existence of a deconfined phase, i.e. Quark Gluon Plasma (QGP) and its phase transition at vanishing and small net-baryon densities, are well established. However, the situation at larger densities is less clear.

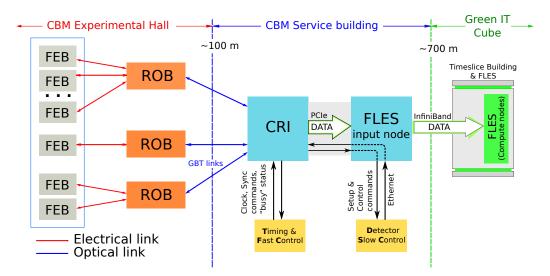

Complementary to the studies of matter at high temperatures and low net-baryon densities performed at RHIC and LHC, the proposed Compressed Baryonic Matter (CBM) experiment at the future FAIR facility, aims to explore the QCD phase diagram at very high baryon-net densities and moderate temperatures. The CBM research program includes the search for the deconfinement phase transition, the study of chiral symmetry restoration in super dense baryonic matter, the search for the critical endpoint, and the study of the nuclear equation of state at high densities. While other experiments (STAR-BES at BNL, BM@N at NICA) are suited to measure bulk observables, CBM is explicitly designed to access rare observables, such as multi-strange hadrons, dileptons, hypernuclei and charmonium. Therefore, a key feature of CBM is the very high interaction rate, exceeding those of contemporary and proposed nuclear collision experiments by several orders of magnitude. However, some of the rare probes have a complex signature, hidden in a background of several hundreds of charged tracks. This forbids a conventional, hardware-triggered readout; instead, the experiment combines self-triggered front-end electronics, fast and free-streaming data transport, online event reconstruction and online event selection.

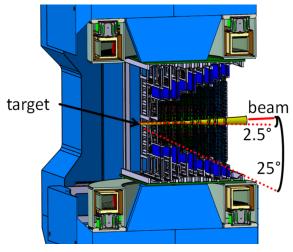

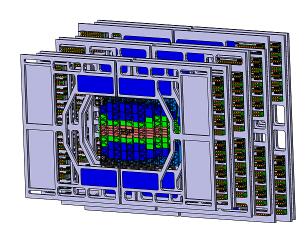

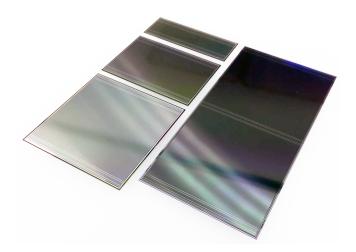

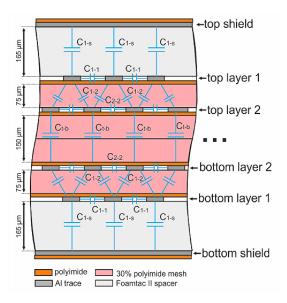

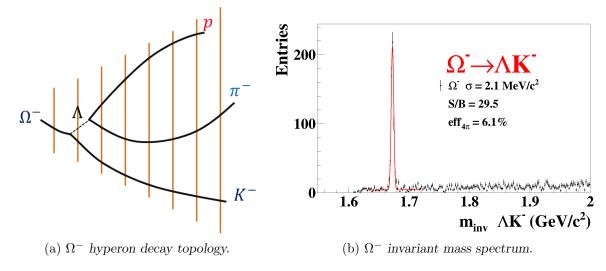

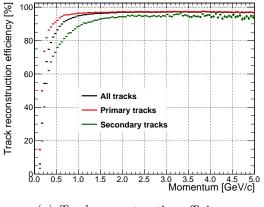

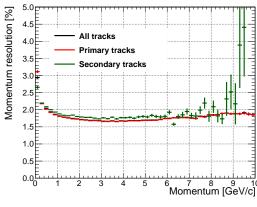

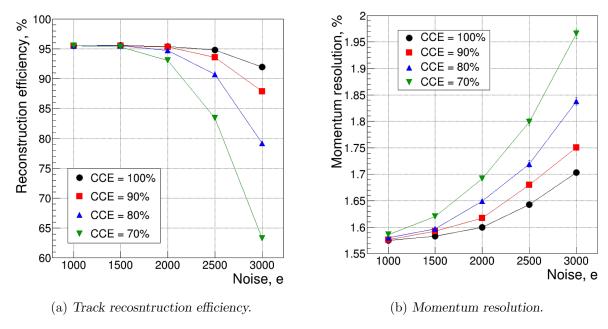

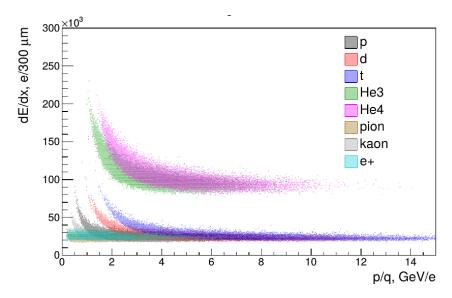

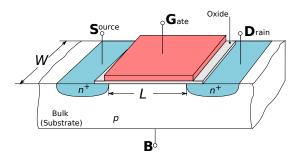

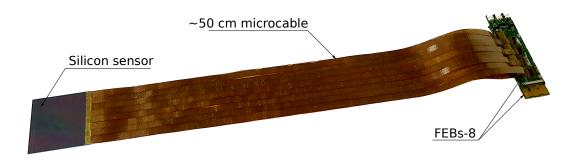

The central detector for tracking and momentum determination of charged particles in the CBM experiment is the Silicon Tracking System (STS). It is designed to measure up to 700 charged particles in nucleus-nucleus collisions between 0.1 and 10 MHz interaction rate, to achieve a momentum resolution in 1 Tm dipole magnetic field better than 2%, and to be capable of identifying complex particle decays topologies, e.g., such with strangeness content. The STS comprises 8 tracking stations equipped with double-sided silicon microstrip sensors. Two million channels are read out with self-triggering electronics, matching the data streaming and on-line event analysis concept applied throughout the experiment. The detector's functional building block consists of a silicon sensor, aluminum-kapton microcables and two front-end electronics boards integrated in a module. The custom-designed ASIC (STS-XYTER) implements the analog front-end, the digitizer and the generation of individual hit data for each signal.

Design of the front-end chip requires finding an optimal solution for time and input charge measurements with tight constraints: small area (58  $\mu$ m channel pitch), low noise levels (below 1500 ENC(e<sup>-</sup>)), low power consumption ( $\leq$ 10 mW/channel), radiation hard architecture and speed requirements. Being a part of the first processing stage in the full readout and data acquisition chain, the characterization of the chip and its integration with the detector components is a crucial

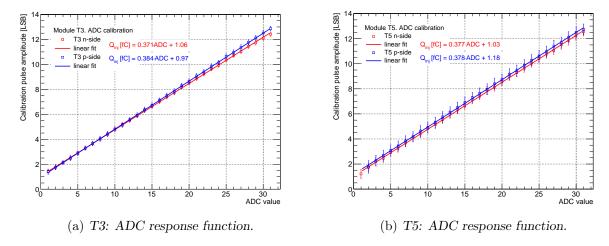

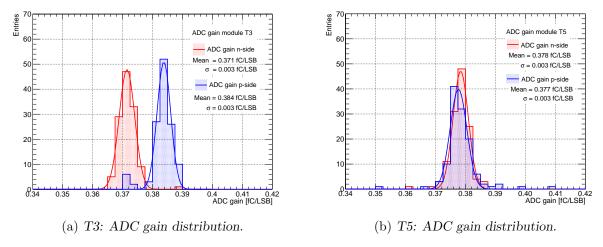

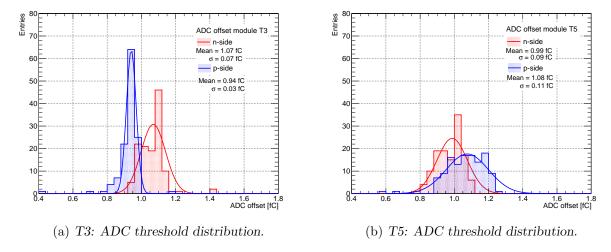

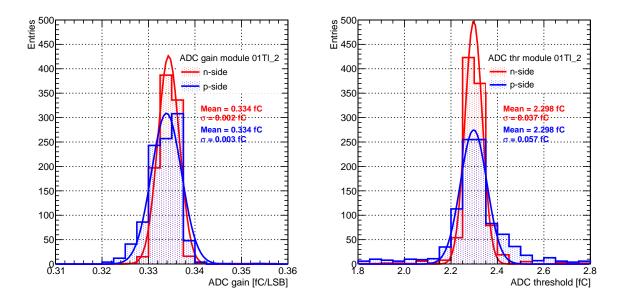

task. In this work, various methods and tools are established for testing and qualifying the ASIC analog front-end. A procedure for amplitude and timing calibration is developed using different functionalities of the chip. The procedure is optimized for our prototype system in order to achieve the best accuracy in the shortest amount of time. Results were verified using a gamma source and an external pulse generator, showing discrepancies below 5%.

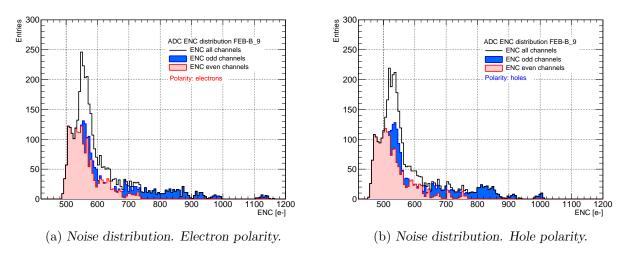

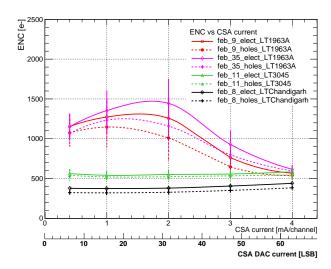

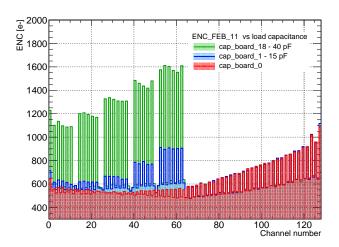

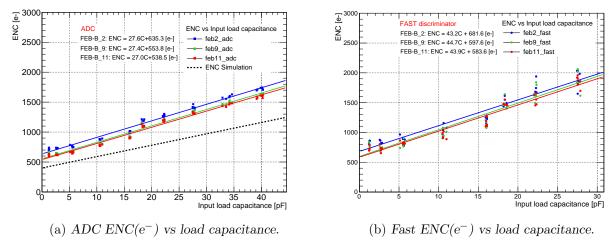

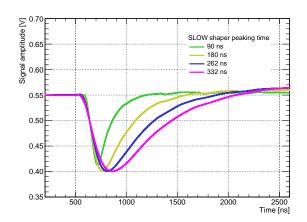

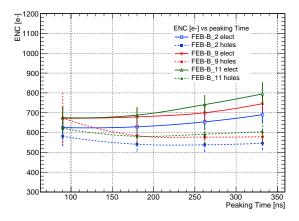

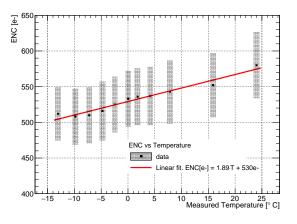

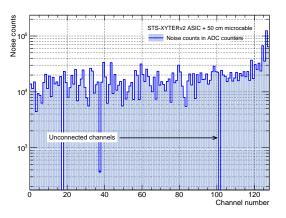

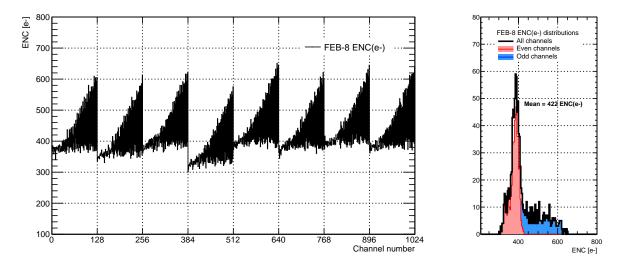

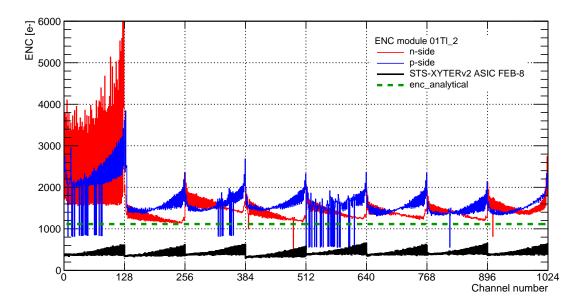

Among the multiple operation requirements of the ASIC, the noise performance is of essential importance. The characterization of the chip noise is carried out as a function of a large number of parameters such as: low-voltage power regulators, input capacitance, shaping time, temperature and bond's protective glue (glob-top). These studies allowed to optimize the ASIC configuration settings, to identify possible malfunctions in the low voltage powering scheme and to select possible glob-top materials to be used in the module assembly. Moreover, important differences are found among odd and even channels, which main cause was related to the bias scheme of the amplifiers of the two groups of channels. This effect has been corrected in the new version (v2.1) of the ASIC.

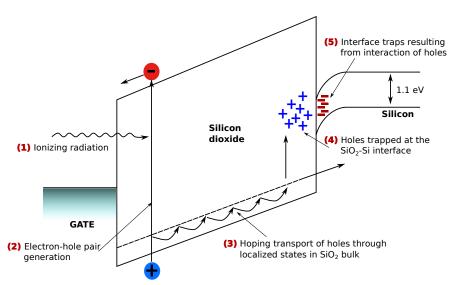

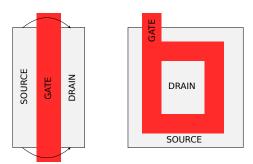

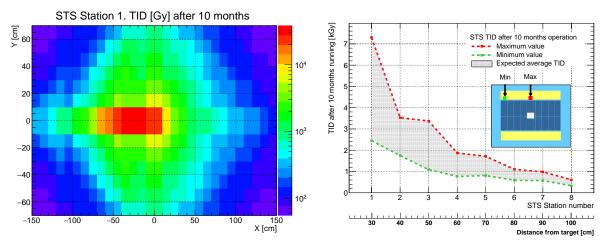

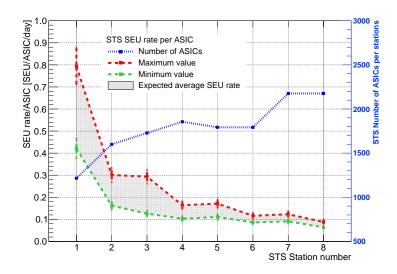

Despite the STS front-end electronics being located outside of the physics acceptance, they will be exposed to high fluxes of charged particles. Considering the SIS100 possible running scenario, the lifetime dose at the location of the electronics is expected not to exceed 800 krad. Consequently, the STS-XYTERv2 ASIC implements a radiation hard design based on dual-interlocked cells (DICE), and triple modular redundancy (TMR).

Multiple dedicated beam campaigns were carried out to evaluate the ASIC's design in terms of immunity to single event upsets (SEU) errors and overall performance after a lifetime doses. The DICE cell SEU cross section was measured in a high-intensity proton beam. Result show a significant improvement of the SEU immunity in the STS-XYTERv2 compared to its predecessor, and allows to estimate the upset rate in the CBM running scenario, resulting in less than one SEU/ASIC/day.

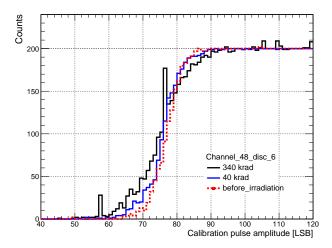

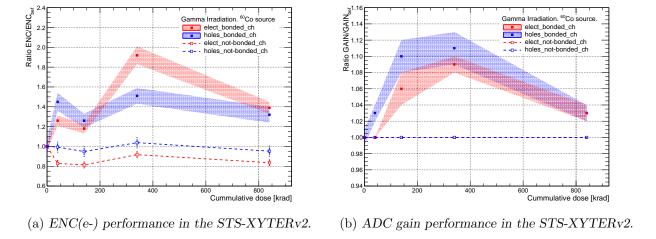

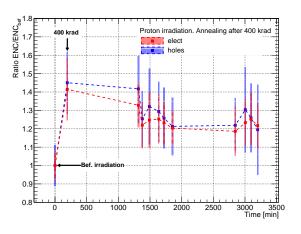

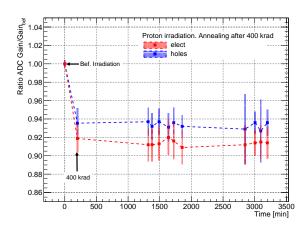

The studies on the total ionizing dose (TID) show that the overall noise levels for the ASIC, at the end of the experiment lifetime, are expected to increase by approximately 40 - 60%. Moreover, they demonstrated that short periods of annealing at room temperature can favorably influence the noise performance of the chip.

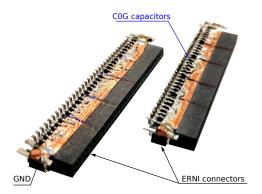

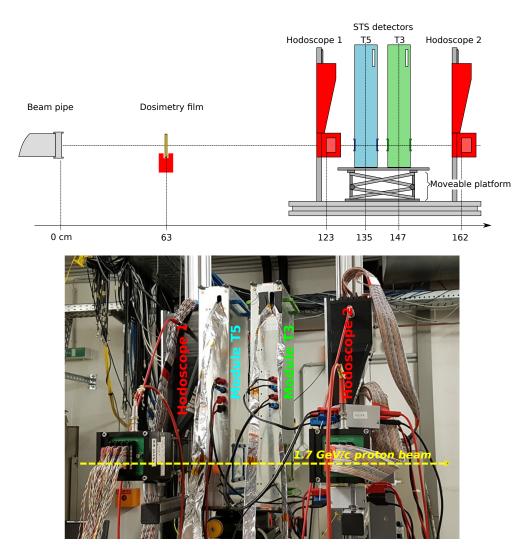

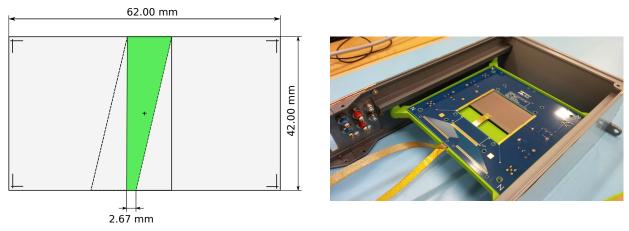

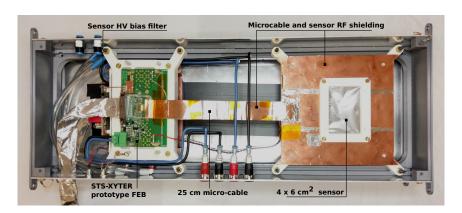

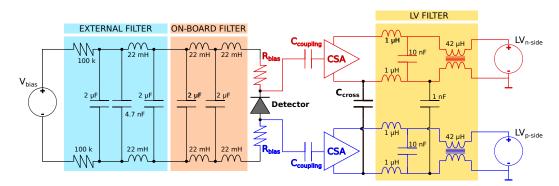

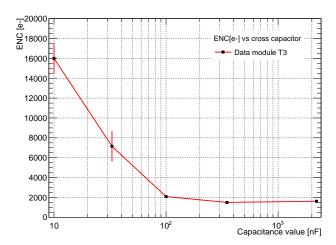

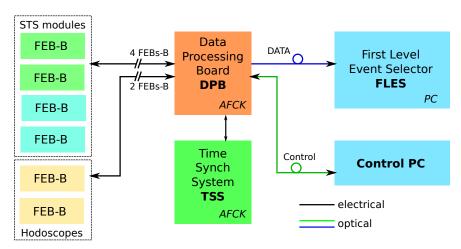

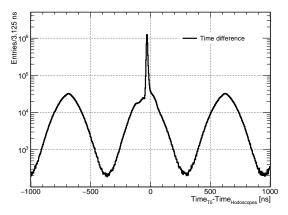

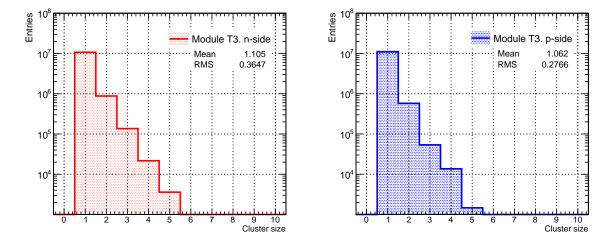

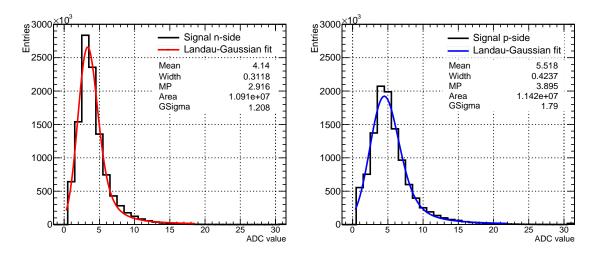

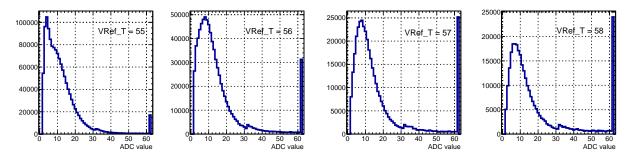

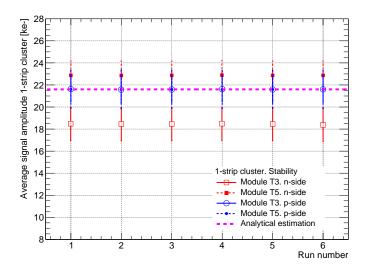

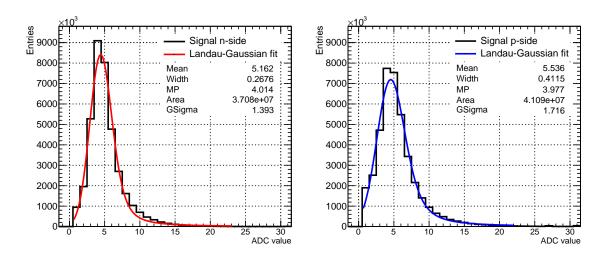

The assembly and test of the STS modules, a complex process with multiple stages and a long learning curve, is illustrated in different parts of this work. The first prototype modules were built with the front-end board type B (FEBs-B), capable of reading out 128 channels for p and n side respectively. The studies were conducted with a relativistic proton beam of 1.7 GeV/c momentum at the COSY accelerator facility, Research Center Jülich, in March 2018. The campaign brought valuable insights to the development of an effective grounding and powering scheme for reading out the detectors. The signal-to-noise was measured for one of the prototype modules, resulting in values larger than 15 for both polarities. A deeper analysis into the collected data allowed the identification of a logic error in the ASIC that affected the readout rate and the quality of the data. This issue was corrected in the new version of the chip.

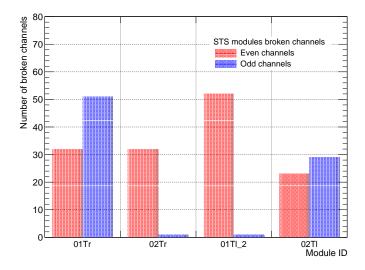

A precursor of the STS detector, named mini-STS (mSTS), has been built within the mCBM project carried out in FAIR Phase0. mSTS was built from 4 fully assembled detector modules. To ensure the proper operation of the ASICs that were used in the module assembly, it was required to develop a rigorous quality assurance procedure. A dedicated setup was built based on a custom designed pogo-pin station and a total of 339 chips were tested. More than 90% of good-quality and operational ASICs were obtained. In the mCBM beam campaign of March 2019, four detector modules were successfully operated in a close-to-final readout chain and valuable data were collected. The mSTS detector was exposed to the products of Ag+Au collisions at energies above 1.58 AGeV and overall interaction rates up to 10<sup>6</sup>, which resembles the real conditions of the CBM experiment.

Along this work, significant progress for the development of the STS detector modules was achieved. Techniques for characterization of the front-end electronics and the complete detector system were developed and worked out. They will be applied for QA of the components during the series production.

# Kurzfassung

Die vergangenen Jahrzehnte haben große Fortschritte im Verständnis der Phasenstruktur stark wechselwirkender Materie gebracht. Von experimenteller Seite wurde dies ermöglicht durch die Untersuchung von Schwerionenkollisionen, von theoretischer durch Lattice-QCD, funktionale QCD-Ansätze, Störungstheorie und effektive Theorien. Von besonderem Interesse ist der Übergang von hadronischen zu partonischen Freiheitsgraden, der bei hohen Temperaturen oder bei hohen Baryonendichten erwartet wird. Diese Phasen spielen eine wichtige Rolle im Verständnis des frühen Universums und der Kerne von Neutronensternen. Die Existenx einer "deconfined" Phase, des Quark-GLuon-Plasmas (QGP) und des zugehörigen Phasenübergangs bei verschwindenden oder kleinen Baryonendichten sind zwischenzeitlich wohl etabliert. Die Situation bei hohen Dichten ist jedoch weniger gesichert. Die Erforschung des Phasendiagramms stark wechselwirkender Materie ist ein bedeutendes Feld der modernen Schwerionen- und Hochenergiephysik.

Komplementär zu den Studien von Materie bei hoher Temperatur und kleinen Netto-Baryonendichten am RHIC und LHC zielt das geplante "Compressed Baryonic Matter" (CBM) Experiment an der zukünftigen FAIR Beschleunigeranlage darauf ab, das QCD-Phasendiagramm bei sehr hohen Baryonendichten und moderaten Temperaturen zu untersuchen. Das CBM-Forschungsprogramm beinhaltet die Suche nach dem "Deconfinement"-Phasenübergang, Untersuchungen zur Wiederherstellung der chiralen Symmetrie in superdichter baryonischer Materie, die Suche nach dem kritischen Endpunkt und die Untersuchung der nuklearen Zustandsgleichung bei hohen Dichten. Während andere Experimente (STAR-BES bei RHIC/BNL, BM@N bei NICA/JINR) vor allem häufig produzierte ("bulk") Observable messen, ist CBM explizit zur Messung seltener Observablen konzipiert, wie z.B. "mehrfach seltsame" Hadronen, Dileptonen, Hyperkerne und Charmonium. Eine Schlüsselfähigkeit von CBM ist daher die sehr hohe Wechselwirkungsrate, die um mehrere Größenordnungen über den Raten existierender und anderer vorgeschlagener Experimente der Kernphysik liegt. Die gesuchten seltenen Proben haben jedoch komplexe Ereignissignaturen innerhalb eines Untergrundes von mehreren Hundert Spuren geladener Teilchen. Dies verbietet eine konventionelle, hardware-getriggerte Auslese. CBM kombiniert daher selbsttriggernde Frontend-Elektronik, einen schnellen "free-streaming" Datentransport sowie eine in Echtzeit durchgeführte Ereignisrekonstruktion und -selektion.

Der zentrale Detektor für Spurerkennung und Impulsmessung geladener Teilchen im CBM-Experiment ist das sogenannte "Silicon Tracking System" (STS). Es ist in der Lage, bis zu 700 geladene Teilchen in Kern-Kern-Kollisionen bei Wechselwirkungsraten von 0.1 bis zu 10 MHz zu messen, eine Impulsauflösung besser als 2% in einem 1 Tm Dipol-Magnetfeld zu erzielen, und komplexe Zerfallstopologien, z.B. mit Strangeness-Content, zu identifizieren. Der STS besteht aus 8 Detektorlagen zur Spurkennung mittels doppelseitig segmentierter Silizium-Streifensensoren. Etwa zwei Millionen Kanäle werden mittels selbstgetriggerter Elektronik ausgelesen, in Einklang mit dem Data-Streaming und Echtzeit-Ereignisanalyse-Konzept, das im gesamten Experiment angewandt wird. Die funktionelle Einheit des STS-Detektors ist das sogenannte "Modul", bestehend aus einem Silizium-Sensor, geringmassigen Aluminium-Kapton-Auslesekabeln und zwei Frontend-Elektronik-Boards. Der dediziert für CBM-STS entwickelte ASIC (STS-XYTER) implementiert die analoge

Elektronik, die Digitalisierung sowie die Erzeugung individueller Datenworte für jedes Signal.

Die Entwicklung des Frontend-Chips erfordert das Finden einer optimalen Lösung für Zeit- und Ladungsmessung unter engen Randbedingungen: Geringe zur Verfügung stehende Fläche (58  $\mu$ m Kanal-Abstand), niedriges Rausch-Niveau (<1500 ENC(e<sup>-</sup>)), geringe Leistung ( $\leq$ 10 mW/Kanal), strahlenharte Architektur und hohe Geschwindigkeit.

Die Charakterisierung des ASIC sowie seine Integration mit den Detektorkomponenten sind wichtige Aufgaben als Teil der ersten Verarbeitungsstufe in der kompletten Auslese- und Datenaufnahmekette. In dieser Arbeit werden diverse Methoden und Werkzeuge für das Testen und die Characterisierung des ASIC-Analogteils etabliert. Prozeduren für die Kalibration von Zeitstempel and Signalamplitude wurden entwickelt unter Verwendung unterschiedlicher Funktionalität des Chips. Die Prozeduren sind für das momentan benutzte Prototypsystem optimiert, um bestmögliche Präzision in kürzestmöglicher Zeit zu erreichen. Die Kalibrations-Ergebnisse wurden mit einer Gamma-Quelle sowie einem externen Signalgenerator überprüft, wobei eine Abweichung von unter 5% zwischen gemessenen und kalibrierten Werten festgestellt wurde. Unter den vielfältigen Anforderungen an den ASIC ist das Rauschverhalten von essentieller Bedeutung. Die Charakterisierung des ASIC-Rauschens wurde als Funktion einer großen Anzahl von Systemparametern durchgeführt: Spannungsregler der Niederspannungsversorgung, Eingangskapazität, ASIC shaping-time, Temperatur und Typ des Schutzklebers der ASIC-Drahtbonds (glob-top). Mit Hilfe dieser Studien wurde die ASIC-Konfiguration optimiert, potentielle Fehlfunktionen im System der Niederspannungsversorgung identifiziert sowie geeignete Glob-Top-Materialien für den Modulbau ausgewählt. Daneben wurden signifikante Unterschiede im Verhalten gerad- bzw. ungeradzahliger Kanalnummern gefunden, die auf Unterschiede im Bias-Schema der Verstärkerschaltungen dieser beiden Kanalgruppen zurückgeführt werden konnten. Dies wurde in der neuesten ASIC-Version v2.1 korrigiert und ein einheitliches Verhalten aller Kanäle erreicht.

Die STS-Frontend-Elektronik ist ausserhalb der geometrischen STS-Detektorakzeptanz platziert, jedoch auch dort hohen Flüssen geladener Teilchen ausgesetzt. Für ein Einsatzszenario am SIS100-Beschleuniger liegt die erwartete Dosis über die gesamte Lebensdauer des Experiments am Ort der Elektronik bei bis zu 800 krad. Der STS-XYTERv2 ASIC implementiert daher ein strahlenhartes Design unter Verwendung von Dual-Interlocked Cells (DICE) sowie Triple Modular Redundancy (TMR). Mehrere dedizierte Strahlzeiten wurden durchgeführt, um das ASIC-Design hinsichtlich Immunität gegenüber Single Event Upsets (SEU) sowie das Verhalten nach einer Lebenszeit-Dosis zu evaluieren. Der SEU-Wirkungsquerschnitt wurde mit einem Protonenstrahl hoher Intensität gemessen. Die Ergebnisse zeigen eine signifikante Verbesserung der SEU-Immunität des STS-XYTERv2 im Vergleich zu seinem Vorgänger und erlauben eine Abschätzung der erwarteten SEU-Rate im Regelbetrieb des kompletten STS mit weniger als einem SEU/ASIC/Tag. Die Untersuchungen zur Gesamtdosis (total ionizing dose, TID) zeigen einen Anstieg des ASIC-Gesamtrauschens am Ende der Lebensdauer um ca. 40-60%. Darüber hinaus konnte gezeigt werden, dass kurze Ausheilungsabschnitte (annealing) bei Zimmertemperatur einen positiven Einfluss auf das Rauschverhalten des Chips haben.

Der Zusammenbau und Test der STS-Module, ein komplexer Prozeß mit mehreren Bauabfolgestufen und einer langen Lernkurve, ist in mehreren Abschnitten dieser Arbeit dargestellt. Einer diskutiert die Tests der ersten Prototypmodule mit Frontend-Boards vom Typ B (FEBs-B), die in der Lagen sind, jeweils 128 Kanäle auf der p- bzw. n-Seite des Sensors auszulesen. Diese Untersuchungen wurden mit einem relativistischen Protonenstrahl von 1.7 GeV/c Impuls am COSY-Beschleuniger, Forschungszentrum Jülich, im März 2018 durchgeführt. Diese Strahlzeit brachte wertvolle Erkenntnisse für ein effektives Erdungs- und Spannungsversorgungsschema der Detektorauslese. Das Signal-zu-Rauschen-Verhältnis wurde für eines der Prototyp-Module gemessen, mit Werten grösser 15 für beide Signalpolaritäten.

Ein Vorläufer des STS-Detektors, genannt Mini-STS (mSTS), wurde innerhalb des mCBM-Projekts im Rahmes des "FAIR Phase 0"-Programms gebaut. Die erste Ausbaustufe des mSTS besteht aus 4 vollständigen Dektormodulen. Um die Funktionalität der beim Modulbau verwendeten ASICs sicherzustellen, war es nötig, eine rigorose Prozedur zur Qualitätskontrolle zu entwickeln. Ein dedizierter Aufbau unter Verwendung einer speziell entworfenen "Pogo-Pin"-Station wurde gebaut und insgesamt 339 ASICs getestet. Der Anteil funktionierender ASICs guter Qualität betrug mehr als 90%. In der mCBM-Strahlzeit im März 2019 wurden 4 STS-Module mit einer nahezu finalen Auslesekette erfolgreich betrieben und wertvolle Daten genommen. Der mSTS-Detektor war den Reaktionsprodukten von Ag+Au Kollisionen bei 1.58 AGeV und Wechselwirkungsraten in der Größen ordnung von 10<sup>6</sup> ausgesetzt, was den Bedingungen im realen CBM-Experiment entspricht.

Im Verlauf dieser Arbeit wurde entscheidender Fortschritt bei der Entwicklung der STS-Detektormodule erzielt. Techniken zur Charkterisierung der Front-end Elektronik und des ganzen Detektorsystems wurden entwickelt und erarbeitet. Sie werden bei der Qualitätskontrolle in der bevorstehenden Modul-Serienproduktion für das STS Detektorsystem angewendet werden.

# Chapter 1

# Introduction

The understanding of the evolution of the universe has always been a fundamental question in the center of all scientific research. With the progress in technology during the last century, sophisticated devices were developed capable of accelerating particles at higher and higher energies, others to look further in the stars. Nowadays, modern physics can quantitatively describe phenomena ranging from the scale of leptons and quarks  $(10^{-15} \text{ m})$  to the scale of astronomical objects  $(10^{26} \text{ m})$  based on our understanding of the four fundamental forces of nature: electromagnetism, gravity, strong and weak interactions. Probing the laws of nature at incessantly finer scales has revealed the existence of a surprisingly large number of elementary particles and provided the means to study their interactions and thus to understand their relationships.

The efforts and contributions from thousands of physicists since the 1930s have resulted in a remarkable insight into the fundamental structure of matter: everything in the universe is found to be made from a few basic building blocks called fundamental particles, governed by four fundamental forces. Whereas gravity is described by Einstein's general relativity theory, the other three forces can be described to an excellent degree by the quantum field theory of quarks and leptons based on a framework consistent with the Einstein's special theory of relativity and quantum mechanics, the Standard Model.

#### 1.1 The Standard Model

The Standard Model, developed in the early 1970s, is currently the most successful theory of elementary particles and their interactions. It has explained almost all experimental results and precisely predicted a wide variety of phenomena. Over time and through many experiments it has become established as a well tested physics theory.

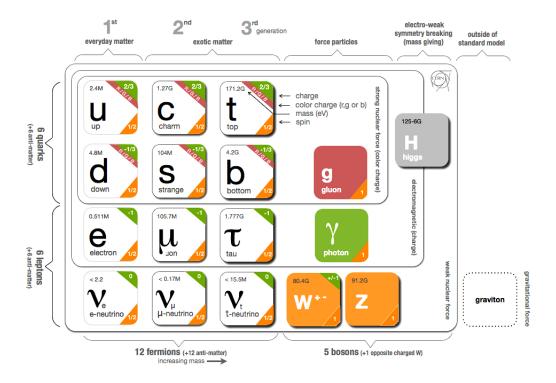

There are seventeen named particles in the Standard Model, organized into the chart shown in Fig. 1.1. Fundamental particles are either the building blocks of matter, called fermions, or the mediators of interactions, called bosons. Fermions follow Fermi-Dirac statistics, and obey the Pauli exclusion principle. These particles occur in two basic types called quarks and leptons. Each group consists of six particles, which are related in pairs, or "generations". The lightest and most stable particles make up the first generation, whereas the heavier and less-stable particles belong to the second and third generations. All stable matter in the universe is made from particles that belong to the first generation; any heavier particle quickly decays to more stable ones.

Three of the fundamental forces at work in the universe result from the exchange of force-carrier particles, which belong to a broader group called "bosons" and follow Bose-Einstein statistics. Particles of matter transfer discrete amounts of energy by exchanging bosons with each other. Each fundamental force has its own corresponding boson: the electromagnetic force is carried by the photon, and the W and Z bosons are responsible for the weak force and the strong force is

carried by the gluon. The physical quantity which is responsible for the strong interaction is color, which comes in three instances: red, blue and green, and the corresponding "negative" units ("antired", "anti-blue" and "anti-green"). Quarks (antiquarks) carry only a single positive (negative) unit of color, while gluons are bi-colored, i.e. they carry one positive and one negative unit of color. The strong interaction between quarks is transmitted via gluons, which carry only a discrete number of colors (gluons do not have mass, charge or flavor which are another set of fundamental properties distinguishing elementary particles); therefore the strong interaction can only modify the color of the interacting quarks by a discrete amount. The underlying fundamental theory of strong nuclear interaction is called after these facts as Quantum Chromodynamics (QCD).

Figure 1.1: Schematic depiction of elementary particles in the Standard Model [1].

There are two fundamental phenomena associated with QCD. The first one is *confinement*, which refers to the experimental observation that quarks and antiquarks can not be found isolated in nature. Namely, quarks and antiquarks are found only confined in hadrons, the composite objects they form. This is a consequence of the constant force between the color charges, as they are separated, resulting from the self interaction of gluons, as they also carry charge. The second fundamental property of QCD is the *asymptotic freedom*, which states that quarks interact weakly at large energies (or equivalently at short distances). As the distance between quarks in hadrons increases, their interaction energy increases as well, which prevents the quarks from hadrons to be separated. Analytically, confinement is unproven, however, Lattice QCD calculations predicted that under certain conditions the confinement of quarks in hadrons vanishes, forming a new state of matter, the quark-gluon plasma (QGP). The quarks and gluons can move freely in the region where a QGP exists, on the scales larger than the size of hadrons (approximately  $10^{-15}$  m). The nuclear matter under such extreme conditions may exist also nowadays in the interior of compact

stellar objects like neutron stars.

As every field theory of particle physics, QCD is based on certain symmetries of nature, deduced by observation. Chiral symmetry exists as an exact symmetry only in the limit of vanishing quark masses [2]. However, the actual quark masses and the strong interaction of quarks and gluons cause the explicit and spontaneous breaking of chiral symmetry, responsible for the generation of hadron masses. Chiral symmetry is approximately restored when quark masses are reduced from their large effective values in hadronic matter to their small bare ones at sufficiently high temperatures and energy densities.

## 1.2 Quark Gluon Plasma (QGP)

Based on the phenomenon of asymptotic freedom, it was expected that a new state of nuclear matter containing deconfined quarks and gluons, if ever managed to be produced in the laboratory at high temperatures and energy densities, should exhibit properties similar to a weakly interacting gas and its dynamics would have been described by kinetic theory. On the other hand, what was discovered at RHIC<sup>1</sup> and LHC<sup>2</sup> [8] exhibits totally opposite behavior: it turned out that hydrodynamic description of the QGP works reasonably well, which indicates discovery of a nearly perfect fluidity of the QGP and, in turn, strong coupling nature of quarks and gluons.

At near-zero net-baryon density, calculations on non-perturbative Lattice QCD predict the phase transition to occur at about an energy density of  $1~GeV/fm^3$  and a critical temperature of  $T_{crit} \approx 170~MeV$ . This deconfined state of matter is believed to have existed approximately 10  $\mu$ s after the Big Bang.

The QGP exists only for a short period of time ( $\sim 10 \text{ fm/c} \approx 10^{-23} \text{ s}$ ) as an intermediate state in the heavy-ion collision and therefore can not be studied directly. Once the fireball expands and the density decreases, individual hadrons will form again. Nevertheless, the existence of the QGP has consequences for the dynamics of the medium and will influence the final particle spectra. Possible QGP signatures are anomalies in the flow [3, 4],  $J/\psi$  suppression [5], jet quenching [6] and variations in the strangeness production [7]. All these are indirect signals that get affected by the interactions in the hadronic medium. Further important signals are electromagnetic probes like photon and dilepton radiation, because they do not interact with the surrounding medium and leave the collision undisturbed [2, 8].

# 1.3 The study of the QCD phase diagram

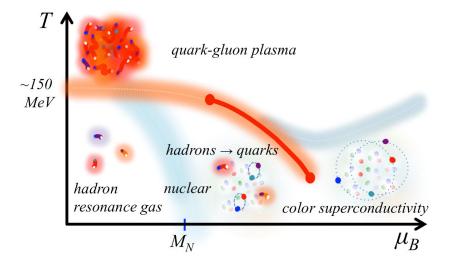

The different phases of matter and their phase diagrams are among the most interesting and challenging fields of modern physics. Phase transitions are important for many different phenomena from ultra-cold atoms and solid-states to nuclear matter and cosmology. Especially the early universe features several phase transitions that are connected to the most fundamental aspects of physics like the separation of the four fundamental forces of nature or the decoupling of photons. The phases of nuclear matter, described in terms of thermodynamical parameters temperature (T) and baryochemical potential ( $\mu_B$ ), are illustrated in Fig. 1.2. At low temperatures and chemical potentials, or equivalent baryon-net densities<sup>3</sup>, the degrees of freedom are hadronic, i.e., neutrons, protons, mesons, etc. At high temperatures, hadrons melt and their constituents, quarks and gluons, form a new phase (QGP), in which the fundamental degrees of freedom are quarks and gluons. This is a very good approximation for the matter produced at mid-rapidity in the highest

<sup>&</sup>lt;sup>1</sup>Relativistic Heavy Ion Collider

<sup>&</sup>lt;sup>2</sup>Large Hadron Collider

$<sup>^3 \</sup>text{Baryon-net density } \rho_B \, \propto \, e^{\frac{\mu_B - m}{T}} - e^{\frac{-\mu_B - m}{T}}$

energy heavy ion collisions at RHIC and LHC, and an exceedingly good approximation in the early universe [9]. In these cases, ordinary hadronic matter forms via a continuous crossover as the liquid QGP expands and cools. This process happened in the universe during the first few microseconds after the Big Bang. In this region of the phase diagram the transition is expected to be a smooth crossover from partonic to hadronic matter [10, 11].

Figure 1.2: Schematic phase diagram of dense nuclear matter, in the baryon chemical potential  $\mu_B$  -temperature T plane [14].

At moderate temperatures and relatively large baryon-net densities, a first order phase transition is predicted from hadronic to partonic matter, with a phase coexistence region in between. A new phase of so called quarkyonic matter [13] has been proposed to exist beyond the first order phase transition, which has properties of both high density baryonic matter and deconfined and chirally symmetric quark matter. Change of the transition nature between these two regimes of the phase transition is denoted by a critical point where strong fluctuations of the physical parameters occur. The nature of the transitions from hadronic to a QGP phase can be summarized as:

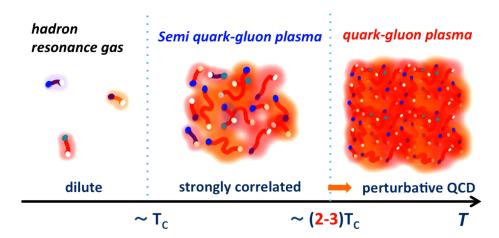

- crossover transition from the hadronic to quark-gluon plasma phase with increasing temperature, see Fig. 1.3;

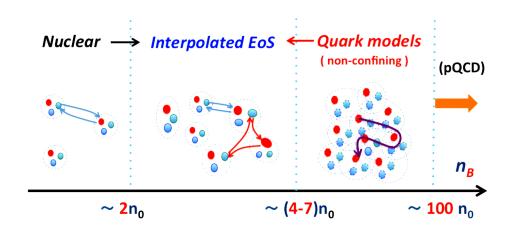

- transition from nuclear to deconfined quark matter with increasing density, see Fig. 1.4.

Pushing to very high baryon-net densities while staying at low temperatures (squeezing nuclei without heating them) takes us into another interesting region of the QCD phase diagram. Matter that is sufficiently dense cannot be made of well-separated nucleons, even at low temperatures: the nucleons are crushed into one another. Because quarks attract each other, cold, dense matter in which quarks fill momentum space up to some high Fermi momentum is a color superconductor in which a condensate of correlated Cooper pairs of quarks creates a superfluid. This state of matter is called colour superconducting condensate, possibly existing in the interior of the neutron stars [15].

Figure 1.3: 1) For  $T \lesssim T_{crit}$ , the system is a dilute gas of hadrons; 2) For  $T_{crit} \lesssim T \lesssim (2-3)T_{crit}$ , thermally excited hadrons overlap and begin to form a semi quark-gluon plasma; and 3) for  $T \gtrsim (2-3)T_{crit}$ , the matter is percolated and a quasiparticle description of quarks and gluons, including effects of thermal media, becomes valid [14].

Figure 1.4: 1) For net-baryon densities  $n_B \lesssim 2n_0$ , the dominant interactions occur via a few ( $\sim 1\text{-}2$ ) meson or quark exchanges, and description of the matter in terms of interacting nucleons is valid; 2) for  $2n_0 \lesssim n_B \lesssim (4-7)n_0$ , many quark exchanges dominate and the system gradually changes from hadronic to quark matter; 3) for  $n_B \gtrsim (4-7)n_0$ , the matter is percolated and quarks no longer belong to specific baryons. A perturbative QCD description is valid only for  $n_B \gtrsim 10-100n_0$  [14].

# 1.4 High baryon density at low temperatures in the cosmos

Neutron stars provide a cosmic laboratory in which the phases of cold dense strongly interacting nuclear matter are realized. The exception is at neutron star births in supernovae where temperatures can be tens of MeV, and in final gravitational mergers where hot and dense matter might be produced and temperatures could reach approximately 10<sup>2</sup> MeV [14]. While heavy ion collision experiments and Lattice QCD simulations provide insights into the properties of hot and dense QCD, neutron stars are the only known window into the rich structure of cold dense QCD [11, 15].

Compact stars are macroscopic objects ruled by the interplay of all fundamental forces in nature. Thereby the structure of the stars' interior is dominated by the strong force, which ultimately has

to counter balance the gravitational attraction. Typical compact-star masses are about 1.4 solar masses, while the radii are in the range of 10 to 14 km [16]. The central density can reach more than five times nuclear saturation density. Thus, the properties of such stars (e.g., mass, radius, moment of inertia, mass-shed frequency, tidal deformability, etc.) are largely determined by the equation of state (EoS) of highly compressed baryonic matter [14]. The temperatures in neutron stars are much smaller than 1 MeV (or 10<sup>10</sup> K); matter in neutron stars lives essentially along the chemical potential axis in the QCD phase diagram, see Fig. 1.2. Therefore superfluid and/or superconductive states of matter are expected to appear inside such stars [11, 15].

In August 2017, the LIGO-Virgo Scientific Collaboration reported the milestone detection of gravitational waves (GWs) from a binary neutron star (BNS) coalescence, dubbed GW170817 [17]. This landmark discovery has opened a new era in astrophysics. Along with the GW detection, several telescopes also reported the observation of electromagnetic coincidence signals in various bands, inaugurating the birth of the GW multimessenger astronomy. The GW170807 event had a duration of approximately 100 seconds and was the result of two neutron stars colliding in a galaxy 130 million light-years from Earth. The localization of the sources of detected gravitational waves was significantly improved when LIGO information was supplied by VIRGO. The collision gave rise to two other major detectable phenomena: a short burst of X-rays and a transient optical near infrared source powered by the synthesis of large amounts of very heavy elements via rapid neutron capture (the r-process) [18]. One of the most relevant implications of this discovery is arguably the possibility of constraining the EoS of the neutron star core through the measurement of the tidal deformability of the binary components [19].

### 1.5 Probing QCD matter with heavy ion collisions

Heavy ion collision experiments at relativistic energies create extreme states of strongly interacting matter and enable their investigation in the laboratory. The main physics goals is to explore the QCD phase diagram, to discover the deconfined nuclear matter under equilibrium (QGP), and to understand its properties such as the EoS, temperature and order of the phase transition, transport coefficients, etc [20, 21]. The system produced in such collisions dynamically evolves within a time duration of the order of 10 - 100 fm/c.

Nowadays, several experimental programs are devoted to the exploration of the QCD phase diagram in different regions. Heavy ion programs at LHC in CERN and at RHIC in Brookhaven National Laboratory, have been running to explore the QGP at small baryon chemical potentials, where matter is produced with almost equal numbers of particles and antiparticles [22]. These studies, extensively developed at the LHC experiment, ALICE<sup>4</sup> [23] and STAR<sup>5</sup> at RHIC [24], have resulted in claiming that partonic degrees of freedom prevail in the early phase of the fireball evolution [11].

In order to search for features like the critical endpoint, the predicted first-order phase transition and the chiral phase transition, moderate temperatures and high baryochemical potentials must be achieved and experimentally accessed. High-energy heavy ion collision experiments worldwide are devoted to the investigation of strongly interacting matter under extreme conditions. The STAR Collaboration at RHIC has performed a beam energy scan (BES) from top energies down to  $\sqrt{S_{NN}} = 7.7$  GeV [25]. In 2019, STAR has initiated the BES-II program, a dedicated low beam energy run for high precision measurements of observables that are expected to be sensitive to the phase structure of the QCD matter [26]. The collaboration will also extend the center-of-mass energy range ( $\sqrt{S_{NN}} = 3 - 7.7$  GeV) by means of a fixed-target program. At the CERN-SPS<sup>6</sup>,

<sup>&</sup>lt;sup>4</sup>A Large Ion Collider Experiment

<sup>&</sup>lt;sup>5</sup>Solenoidal Tracker at RHIC

<sup>&</sup>lt;sup>6</sup>Super Proton Synchrotron

the NA61/SHINE<sup>7</sup> experiment continues to search for the first-order phase transition by measuring hadrons using light and medium heavy ion beams [27]. At the Joint Institute for Nuclear Research (JINR) in Dubna, a heavy ion collider project (NICA) is planned with the goal to search for the coexistence phase of nuclear matter [28] at energies up to  $(\sqrt{S_{NN}} = 11~GeV)$ . Due to luminosity and detector limitations, these experiments are constrained to the investigation of bulk observables which are predominantly sensitive to the late and dilute phase of the collision when most of the particles freeze out. In contrast, the research program of the future Compressed Baryonic Matter (CBM) experiment [29] at the Facility for Antiproton and Ion Research (FAIR) in Darmstadt [30] focuses on the measurement of diagnostic probes of the early and dense phase of the fireball evolution.

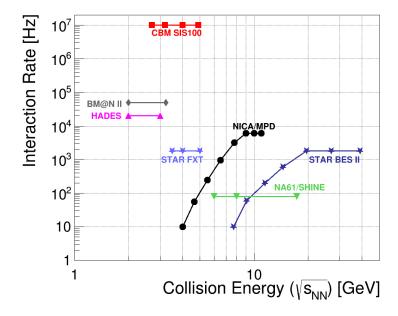

Figure 1.5: Comparison of the interaction rates of existing and planned heavy-ion experiments as a function of the center-of-mass energy [31].

The experimental discovery of landmarks like a first-order phase transition or a critical point in the QCD phase diagram would be a major breakthrough in our understanding of the strong interaction in the non-perturbative regime, with fundamental consequences for our knowledge on the structure of neutron star cores, chiral symmetry restoration, and the origin of hadron masses.

## 1.6 Motivation and scope of this work and thesis outline

The CBM experimental strategy is to perform systematic differential measurements of almost all particles produced in nuclear collisions, with unprecedented precision and statistics. The experiment will implement a novel readout scheme without hierarchical trigger. This novel concept requires fast, self-triggered and radiation hard readout electronics and a high-speed data preprocessing and acquisition system. The aim of this thesis work is the development and test of the front-end electronics of the main tracking and core detector of the experiment: the Silicon Tracking System (STS). The project focuses on the first component of the STS readout chain and its integration with the strip detector, with all required services and elements of the common CBM DAQ infrastructure used for data readout and detector control.

<sup>&</sup>lt;sup>7</sup>North Area 61

The thesis is structured in six chapters, the current one has an introductory character, in which some fundamental concepts of the heavy ion collisions are briefly summarized. The second chapter introduces the physics program and main observables of the CBM experiment. In addition, it highlights the experimental challenges and the novel concept of a free-streaming readout chain. The final sections of the second chapter bring a detailed description of the STS detector, requirements, components design, physics performance and potentialities of the detector for particle identification based on the capabilities of its front-end electronics. The remaining chapters are organized as follow:

- Chapter 3 introduces the STS front-end electronics and its operation within a prototype readout chain. It summarizes the tests and results of the full chip characterization.

- Chapter 4 focuses on evaluating the radiation hard design of the STS front-end electronics in dedicated beam campaigns. The study allows to check the response of the chip after high irradiation doses and to evaluate how this could affect the operation of the final detector.

- Chapter 5 summarizes the results of a proton beam campaign dedicated to test the first STS prototype modules with the custom-designed front-end electronics. Several system aspects such as: overall noise, signal to noise ratio, powering scheme and system integration are presented and discussed.

- Chapter 6 covers the realization of a small-scale prototype of the STS detector for the activities of the FAIR phase 0. In the first sections of the chapter, the development and test of procedures for the quality assurance of the STS front-end electronics are illustrated. An important achievement was the built of the first fully assembled STS modules and their operation in realistic high-rate Ag+Au collisions at 1.58 AGeV.

The final chapter summarizes the fundamental results that have been presented and discussed across this work. The outlook section highlights the impact and contributions of this research in the next steps of the detector development and construction.

# Chapter 2

# The CBM experiment and the Silicon Tracking System

The CBM experiment is a next-generation experiment to be operated at FAIR, currently under construction in Darmstadt, Germany [30]. The CBM experiment proposes one of the richest and leading research programs in the field of heavy-ion physics. Its goal is to investigate the phase diagram of strongly interacting matter in the region of high baryon-net densities and moderate temperatures, employing high energy nucleus-nucleus collisions. A key feature of CBM is its very high interaction rate, exceeding those of contemporary nuclear collision experiments by several orders of magnitude [31]. The setup consists of a fixed-target forward spectrometer without a conventional, hardware-triggered readout; instead a novel free-streaming and online reconstruction concept will be implemented. The experiment is currently being developed by an international collaboration between institutes from Germany, Russia, India, Romania, Poland and other countries [29].

# 2.1 The future FAIR facility

The international FAIR facility in Darmstadt will provide unique research opportunities in the fields of nuclear, hadron, atomic and plasma physics [30, 32]. The heavy ion synchrotron SIS100<sup>1</sup> is the central part of the FAIR accelerator facilities. The accelerator tunnel has a circumference of 1084 meters and is being built with the possibility to accommodate, in the future, an additional synchrotron SIS300. The difference between the two synchrotrons relies in their magnetic rigidity of 100 Tm and 300 Tm, respectively.

FAIR will be one of the largest and most complex accelerator facilities in the world. It will have the unique ability to provide particle beams of all the chemical elements (or their ions), as well as antiprotons. These beams will support a broad field of research grouped mainly in four collaborations: APPA (Atomic, Plasma and Applications), CBM, NuSTAR (Nuclear STructure, Astrophysics and Reactions) and PANDA (anti-Proton ANihilation at DArmstadt).

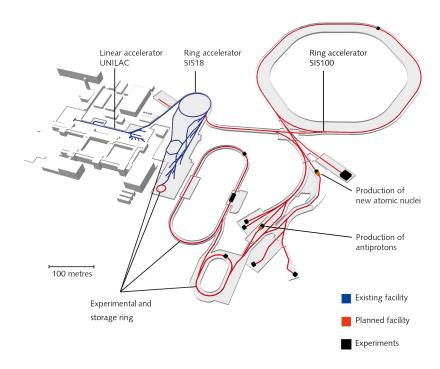

Figure 2.1 illustrates the existing (blue) and the future (red) installations of the FAIR facility. The existing  $GSI^2$  accelerators will serve as the first acceleration stage for the SIS100/300 synchrotrons.

The research program devoted to the exploration of compressed baryonic matter will start with primary beams from the heavy ion synchrotron SIS100 [29]. The top energies of the SIS100 will be up to 29 GeV for protons and up to 11 AGeV for Au ions. Due to the slow extraction from the

<sup>&</sup>lt;sup>1</sup>Schwerionensynchrotron (DE), Heavy ion synchrotron (EN)

<sup>&</sup>lt;sup>2</sup>Gesellschaft für Schwerionenforschung GmbH

Figure 2.1: Layout of the FAIR facility. Blue lines represent existing GSI facilities, the new accelerator complex is shown with red. The superconducting synchrotrons SIS100 or SIS300 will provide ion beams for the CBM experiment [30].

synchrotrons, the beam at the CBM cave will have a continuous structure. This allows to increase the collision rate, since the beam particles will be uniformly distributed in time. The beam intensity is expected to be up to  $10^9$  ions per second resulting in  $10^7$  interactions per second using a 1% interaction probability in target.

## 2.2 The physics program of the CBM experiment

The rich physics program of the CBM experiment is devoted to explore the phase diagram of strongly interacting matter in the region of high-net baryon densities and moderate temperatures, employing high energy nucleus-nucleus collisions [11]. These studies, complementary to the experiments at SPS, BM@N<sup>3</sup> [28], HADES<sup>4</sup> [33], NICA/MPD<sup>5</sup> and STAR at RHIC [25], aim to investigate the EoS of QCD matter at densities similar to the densities in the core of neutron stars, and search for a possible phase transition from hadronic to quark-gluon matter, a critical point of the QCD phase diagram, existence of quarkyonic matter [13], and signatures of chiral symmetry restoration [9, 31]. However, due to luminosity or detector limitations these experiments can not measure rare observables with very low production cross sections and are constrained to the investigation of abundantly produced particles.

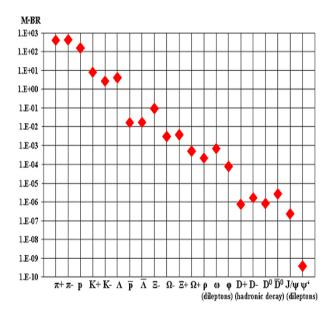

The high interaction rate of the CBM experiment opens the possibility to measure the rare probes and their properties with unprecedented statistics. The multiplicity of some probes is expected to be one in a million collisions or even less, as shown in Fig. 2.2. Figure 1.5 shows a

<sup>&</sup>lt;sup>3</sup>Baryonic Matter at Nuclotron

<sup>&</sup>lt;sup>4</sup>High Acceptance Di-electron Spectrometer

<sup>&</sup>lt;sup>5</sup>Multi-Purpose Detector

Figure 2.2: Model predictions for yields (multiplicity  $\times$  branching ratio) of probes intended to be measured by the CBM experiment.

comparison of interaction rates and center-of-mass energies for different high energy experiments. Resting upon the fixed target approach and the large beam intensities, CBM aims to achieve unprecedented sensitivity in particle reconstruction [31].

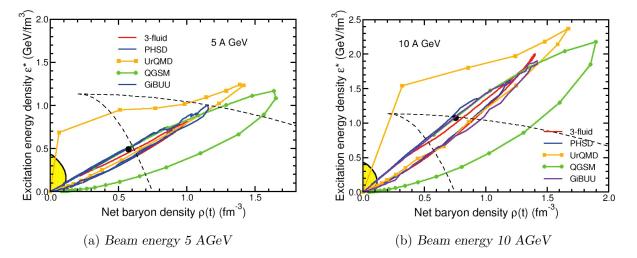

To address these questions CBM will investigate collisions of heavy ion and proton beams, with fixed, heavy element targets, at beam energies from 2 to 11 AGeV (up to 14 AGeV for light nuclei and 29 AGeV for protons) [29]. Heavy ion collisions in this range of energies are ideally suited to explore the properties of dense baryonic matter. This is illustrated in Fig 2.3, where the excitation energy density in the center of the fireball, is shown as a function of the netbaryon density for central Au+Au collisions at beam energies of 5 A and 10 AGeV [11, 34]. This behavior is predicted by different transport models and a hydrodynamic calculation. According to the simulations, densities of up to 8 times saturation density can be produced already at beam energies of 10 AGeV. Under these conditions the nucleons overlap, and theory predicts a transition to a mixed phase of baryons and quarks. In addition, simulations show that the fireball spends a relatively long time in the phase coexistence (marked with dashed lines) at 5 AGeV and it emerges from it at higher energies. Time scale is extracted from UrQMD [35] and QGSM simulation, where every point in the evolution lines is equivalent to t=1 fm/c [34].

Nowadays, the understanding of the properties of strongly interacting matter is mainly driven by new experimental results. Due to the complexity of the final state of heavy ion reactions, the extraction of significant information requires systematic measurements such as excitation functions, system size dependences, and multi-differential phase-space distributions of identified particles, including flow, event-by-event fluctuations, and other types of correlations. The most promising observables for a comprehensive study of the QCD phase diagram are here summarized.

Figure 2.3: Evolution of the excitation energy in the center of the fireball as a function of the baryon-net density calculated by different transport models and a 3-fluid hydrodynamics code. The Au+Au collision system is simulated for two different running scenarios, at 5 A and 10 AGeV.

#### Collective phenomena

The collective motion of the final-state hadrons, resulting from heavy ion reactions, contains important information on the collision dynamics. The isotropic radial flow allows to characterize the collision system at kinetic freeze-out, i.e. when elastic collisions of the produced particles cease. Anisotropic flow results from the conversion of anisotropies in the density distribution into pressure gradients, and thus gives access to the equation of state of dense nuclear matter [36]. It can be described using a decomposition of the azimuthal distribution of the emitted particles in the plane transverse to the beam axis:

$$\frac{dN}{d\varphi} \propto 1 + 2\sum_{n=1}^{\infty} v_n cos[n(\varphi - \Psi_n)]$$

(2.1)

where N is the number of produced particles,  $\varphi$  is the azimuthal angle of each particle and  $\Psi_n$  is the  $n^{th}$  order symmetry plane. The coefficients  $v_n$  gives the magnitude of the flow-vector [3].

In order to conclusively address the degree of thermalization, the EoS and the in-medium properties of strange particles, multi-differential flow measurements for a large variety of hadron species, in particular strange hadrons and anti-baryons, are mandatory for a variety of collision systems and beam energies in the SIS100 energy range. The direct flow  $(v_1)$  is sensitive to the details of the phase transition, the softening of the QCD matter EoS, and it is also an important observable for clarifying the role of partonic degrees of freedom [4]. The strength of the elliptic flow  $(v_2)$  and its dependence on the particle transverse momentum can shed light on the degrees of freedom which prevail in the early stage of the collision. Moreover, the flow of strange particles and anti-baryons is determined by their in-medium potential and hence allows to address the restoration of chiral symmetry in the dense medium. The CBM experiment will significantly contribute to our understanding of the QCD matter EoS by measuring the flow of identified particles at FAIR energies, including multi-strange hyperons and di-leptons [31].

#### **Event-by-event fluctuations**

In the vicinity of the deconfinement phase transition, critical density fluctuations have been predicted to cause non-statistical event-by-event fluctuations of conserved quantities such as baryon number, strangeness and electrical charge. They are related to thermodynamical susceptibilities and therefore provide insights into the properties of matter created in high energy collisions [37]. Lattice QCD calculations suggest that higher moments of these distributions (skewness, kurtosis...) are expected to be particularly sensitive to the phase structure created in such collisions. The presence of a critical point is expected to lead to a non-monotonic behavior of these moments [37, 38].

Measurements of these fluctuations have been performed by other collaborations in order to search for the critical point. However, up to date no higher-order event-by-event fluctuations have been measured at SIS100 energies. The CBM experiment will carry out precise measurements of high-order fluctuations at various beam energies in the high net-baryon density range  $\sqrt{S_{NN}} = 2.7$ -4.9 GeV, corresponding to  $\mu_B \simeq 800$  - 500 MeV [31].

#### Strangeness and hypernuclei production

High precision measurements of yields, momentum and angular distributions of multi-strange hyperons in nucleus-nucleus collisions at SIS100 energies, will allow to study the degree of equilibrium of the fireball. Strangeness production is an essential observable with possible connection to a phase transition. Systematic measurements of these observables as a function of collision energy appear a very promising strategy for the detailed investigation of the deconfinement phase transition [39, 40]. According to hadronic transport models, which do not feature a partonic phase, multi-strange hyperons are produced in sequential collisions involving kaons and lambdas; therefore they are sensitive to the density of the fireball. In addition, excited hyperon states can be identified.

Replacing an up or a down quark with a strange quark in a nucleon, which is bound in a nucleus, leads to the formation of a hypernucleus. A new quantum number, strangeness, is introduced into the nucleus, adding a third axis to the nuclear chart. The measurement of single and double hypernuclei opens the possibility to study the third dimension, and provides insights into the hyperon-nucleon and hyperon-hyperon interaction, which play an important role in the understanding of the structure of neutron stars [16]. Thermal model calculations show that the maximum of the hypernuclei excitation function is at FAIR energies. This is due to the superposition of two main effects: the increase of light nuclei production with decreasing beam energy, and the increase of hyperons production with increasing beam energy [41]. In contrast to the methods used before for the production of hypernuclei using  $K^-$  beams and light nuclei as target, CBM experiment intends to produce double-hypernuclei in heavy ion collisions via coalescence of  $\Lambda$  hyperons with nucleons or light nuclei in the final stages of the reaction [31].

#### Open and hidden charm

The yields of charmed hadrons are sensitive probes to the state in the fireball on the initial state of the collision. Due to its large mass,  $c\bar{c}$  pairs can be produced only in hard processes, at the early stage of the nucleus-nucleus reaction. Depending on their interaction with the medium (hadronic or partonic), charm and anti-charm quarks hadronize into D mesons, charmed baryons, or charmonium [42].

At SIS100, hidden and open charm measurements can be performed in proton-induced reactions using proton beams with energies close to the production threshold (up to 29 GeV) and different targets. Open charm measurements address the understanding of charm production near threshold, the properties of charmed particles at saturation density and their propagation in cold nuclear matter. Moreover, they constitute an important baseline for measurements in nuclear collisions.

The formation of charmonium states is another observable sensitive to the conditions in the fireball. In a deconfined medium, charmonium states are expected to dissociate into c and  $\bar{c}$  quarks due to color screening effects. This has been the first predicted signature for the QGP formation [42]. A particular and challenging experiment is to study the  $J/\psi$  production in collisions of symmetric nuclei up to 15 AGeV, and below threshold in Au+Au collisions at 10 AGeV. For this specific observable, the CBM experiment will use very high interaction rates and a dedicated experimental configuration, optimized for the identification of  $J/\psi$  [31].

#### Dileptons spectroscopy

The search for signatures of chiral symmetry restoration, which is expected to occur at very high baryon-net densities and/or temperatures, is one of the most important goals of heavy ion collision experiments. An observable consequence would be the modification of hadron properties inside nuclei, or in hot and dense matter. The degeneration of the spectral functions of chiral partners, such as the  $\rho$ -meson and the  $a_1$ -meson is a consequence of the restoration of the chiral symmetry. While the  $a_1$ -meson is very difficult to measure in the nuclear medium, the in-medium spectral function of the  $\rho$ -meson is accessible via the measurement of its decay into lepton pairs [2]. Moreover, the excess yield of lepton pairs in the energy range (M $\leq$ 1 GeV/c) is sensitive to the temperature of the created matter and its space-time extension. The slope of the dilepton invariant-mass spectrum between 1 and 2.5 GeV/c directly reflects the average temperature of the fireball [8]. The precise measurement of the energy dependence of the spectral slope opens the possibility to measure the caloric curve, which would be the first direct experimental signature for phase coexistence in high-density nuclear matter [31].

Short lived vector mesons can decay into di-lepton pairs  $(\rho, \phi, \omega \to e^+e^-, \mu^+\mu^-)$  which interact with particles in the collision region only via electromagnetic interaction. Dileptons are emitted from the fireball during all stages of the collision. Since they do not further interact with the surrounding medium, they offer the unique opportunity to look into the thermodynamical state of the medium at the moment of their production.

The CBM experiment will perform pioneering multi-differential measurements of lepton pairs over the whole range of invariant masses emitted from a hot and dense fireball. The experimental challenges are the very low signal cross sections, decay probabilities in the order of  $10^{-4}$  and high combinatorial background [31].

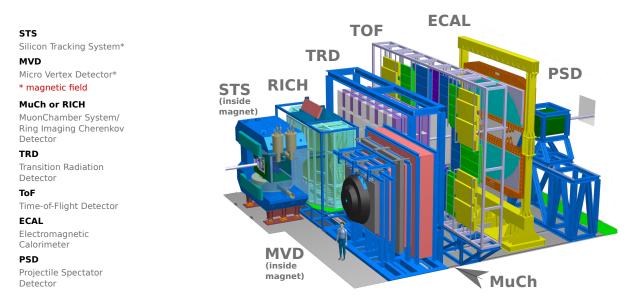

## 2.3 The CBM experimental setup

The CBM experiment possesses a wide and challenging physics program that includes the study of multiplicity, distribution in phase space and flows of all interesting particles. Many of the important observables are rare diagnostic probes carrying the information of the dense stage of the fireball evolution [11]. To collect sufficient statistics, the experiment is planned to operate at reaction rates up to 10 MHz with a continuous (non-bunched) beam. Since most of the observables have complex trigger topologies, the experiment will implement a novel free-streaming readout mode [31]. Timestamped data from all detectors will be sent to a computing farm, where track reconstruction, event formation, and analysis will be performed online. The estimated data rate for the whole experiment in Au+Au collisions is approximately 2 TB/s in such experimental scenario. This represents a prohibitively data rate, therefore, fast algorithms for reconstruction and event selection will be performed in real time in order to reduce by two order of magnitude the stored data.

The CBM experiment has been designed as a multipurpose apparatus capable to register hadrons, electrons and muons in p+p, p+A and A+A collisions over the full FAIR beam en-

ergy range. The experiment has an angular acceptance between 2.5° and 25° to cover mid and forward rapidity hemisphere for symmetric collision systems over the energy range. It comprises the following subsystems:

- a dipole magnet for momentum measurements [43];

- a Micro Vertex Detector (MVD) to measure short-lived decay vertices and low-momentum particles;

- a Silicon Tracking System (STS) to provide tracking of charged particles and to measure their momentum;

- a Ring Imaging Cherenkov detector (RICH) to provide electron/pion identification;

- a Muon Chamber (MUCH) for muon identification and track reconstruction;

- a Transition Radiation Detector (TRD) to suppress pions and to support track reconstruction;

- a Time-of-Flight (TOF) wall for hadrons identification;

- an Electromagnetic Calorimeter (ECAL) for photon energy measurement;

- a Projectile Spectator Detector (PSD) for the collision centrality and event plane determination.

The CBM detector system can be used in two operation modes: the first one is optimized for electron identification (electron configuration) and the second is specialized for muon identification (muon configuration). In the first one, all the subsystems apart from MUCH will be involved. In the muon configuration, the RICH detector is replaced by MUCH and the electromagnetic calorimeter is removed. A schematic view of the detector-setup concept is shown in Fig. 2.4.

Figure 2.4: The CBM experimental setup at FAIR.

Table 2.1 summarizes the CBM subsystems used for registering the different particle types [44]. Below, each detector subsystem is briefly explained. The STS is described separately in the next section.

| Table 2.1: CBM detectors used for registering the different particle types are marked with ✓ symbol. Those |

|------------------------------------------------------------------------------------------------------------|

| subsystem that can also contribute to reduce the background are marked with $(\checkmark)$ [44].           |

| Particle                       | MVD          | STS          | RICH           | MUCH         | TRD            | TOF            | ECAL         | PSD          |

|--------------------------------|--------------|--------------|----------------|--------------|----------------|----------------|--------------|--------------|

| $\pi, K, p$                    | ✓            | ✓            | (✓)            |              | <b>(√)</b>     | ✓              |              | <b>√</b>     |

| Hyperons                       |              | $\checkmark$ |                |              | $(\checkmark)$ | $(\checkmark)$ |              | $\checkmark$ |

| Open charm                     | $\checkmark$ | $\checkmark$ | $(\checkmark)$ |              | $(\checkmark)$ | $\checkmark$   |              | $\checkmark$ |

| Electrons                      | $\checkmark$ | $\checkmark$ | $\checkmark$   |              | $\checkmark$   | $\checkmark$   |              | $\checkmark$ |

| Muons                          |              | $\checkmark$ |                | $\checkmark$ |                | $(\checkmark)$ |              | $\checkmark$ |

| Gamma                          |              |              |                |              |                |                | $\checkmark$ | $\checkmark$ |

| Gamma via $e^{\pm}$ conversion | $\checkmark$ | $\checkmark$ | $\checkmark$   |              | $\checkmark$   | $\checkmark$   |              | $\checkmark$ |

#### Superconducting dipole magnet

The dipole magnet is one of the key devices used in the determination of the charged particle momenta in the CBM experiment. Its job is to bend the paths of particles emerging from the high-energy collisions. The more momentum a particle has the less its path is curved by the magnetic field, so tracing its path gives a measure of momentum. It magnet is designed to be superconducting in order to reduce the operation costs. It will provide a vertical magnetic field of 1 Tm from the interaction point to approximately 1 m downstream the target [43].

#### Micro Vertex Detector (MVD)

The main task of the MVD is to distinguish between primary and displaced vertices, for example, to reconstruct decays of charmed hadrons: D-mesons or  $\Lambda_c$  baryons. This task requires a high resolution along the position vector of approximately 70  $\mu$ m, which turns to 5  $\mu$ m spatial resolution and low material budget. The MVD is located directly behind the target (5 - 20 cm downstream) inside the dipole magnet. The MVD is placed in vacuum, thus it is able to reconstruct low-momentum tracks that helps to reject background for di-electrons [45]. The requirements of high spatial resolution, low material budget and high radiation tolerance are fulfilled with CMOS MAPS<sup>6</sup> with fine pixel size of several dozens of  $\mu$ m. Due to the limited readout speed, the MVD will participate only in data taking with interaction rates up to  $10^5$  Hz [45, 46].

#### Silicon Tracking System (STS)

The STS is a key detector of the CBM setup, responsible for tracking charged particle and provide momentum determination. The detailed description of STS design is presented in section 2.4.

#### Ring Imaging Cherenkov detector (RICH)

The RICH detector is designed to provide particle identification via Cherenkov radiation [47]. It allows separating electrons from pions up to 8 GeV/c with a pion suppression factor above 300 and electron identification efficiency above 85%. The RICH detector will be used in the electron-hadron configuration of the CBM setup. It will be located behind the dipole magnet, about 1.6 m downstream of the target. It will consist of a 1.7 m long CO<sub>2</sub> gas radiator and two arrays of mirrors and photo detector planes. The design of the photo detector planes is based on

<sup>&</sup>lt;sup>6</sup>Monolithic Active Pixel Sensors

MAPMTs<sup>7</sup> (Hamamatsu H12700) in order to provide high granularity, high geometrical acceptance, high detection efficiency of photons also in the near UV region and a reliable operation. Mirrors are constructed with a reflective  $Al + MgF_2$  coating to direct the light to the high granularity photon detectors [47, 48].

#### Muon Chambers System (MUCH)

The MUCH system allows to identify muon pairs produced in high energy heavy ion collisions [49]. It consists of 5 layers of hadron absorbers and tracking detector planes between the absorber layers. The absorber layers consist of a 60 cm thick carbon plate followed downstream by four iron plates of 20 cm, 20 cm, 30 cm and 100 cm thickness, respectively. The tracking planes are based on GEM<sup>8</sup> [50] and RPC<sup>9</sup> detectors. The MUCH will be operated in different setup configurations by varying the positions of the absorber-detector combinations. MUCH system in combination with STS are the main detectors in the CBM experimental setup to study di-muon decay channels of vector mesons like  $\rho, \omega, \phi$  and  $J/\psi$ . Reconstruction of such particles requires an accurate muon identification [49].

#### Transition Radiation Detector (TRD)

The main task of the TRD is to identify electrons above momenta of 1 GeV/c and thus to extend the electron identification capabilities of the RICH detector above momenta of  $p\sim5$  GeV/c. This identification has to be achieved with a pion suppression factor in the range 10-20, in order to allow for a measurement of dielectrons in the mass range from below the  $\rho$  and  $\omega$  masses to beyond the J/ $\psi$  mass with a good signal-to-background ratio. The particle identification is based on the effect that ultra-relativistic charged particles produce transition radiation when traversing a boundary between media with different dielectric constants. Currently, the TRD is envisaged to be a system composed of one station with four layers. The station will be located at a distance of approximately 5 m from the target. To detect the produced radiation MWPC<sup>10</sup> will be used, operated with a mixture of Xe/CO<sub>2</sub> gases [51].

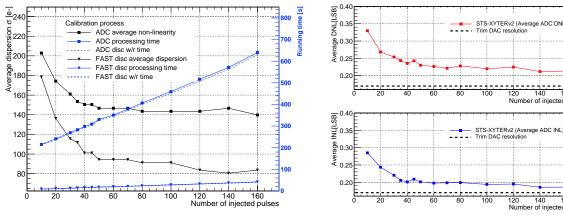

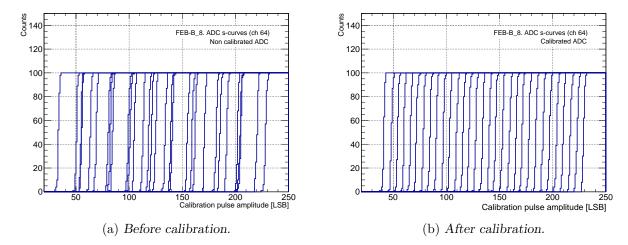

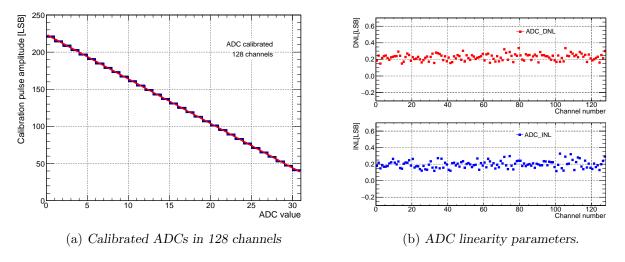

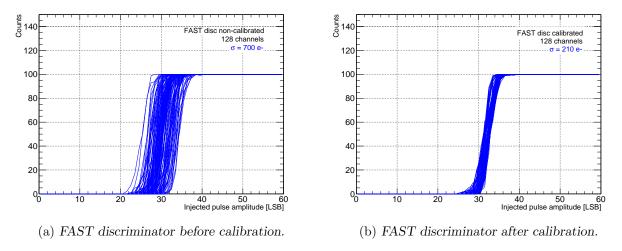

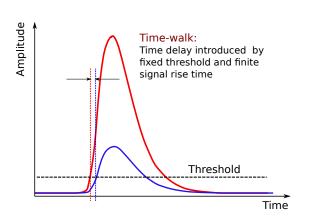

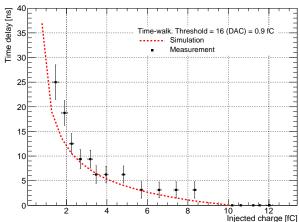

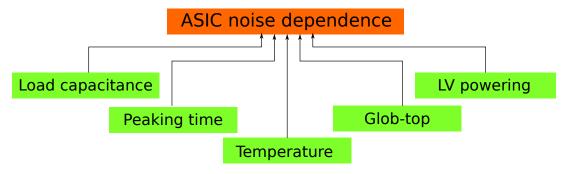

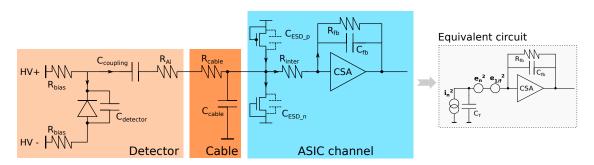

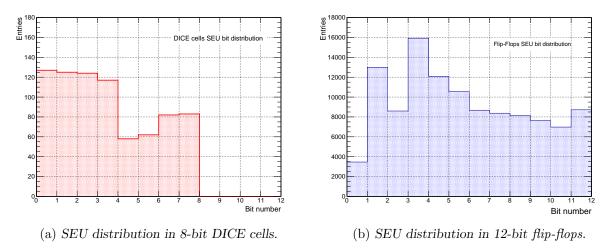

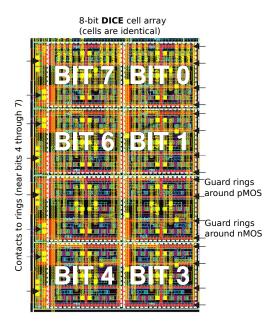

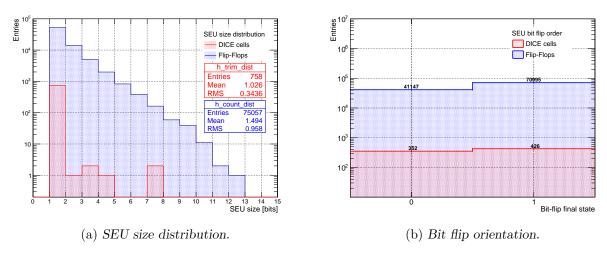

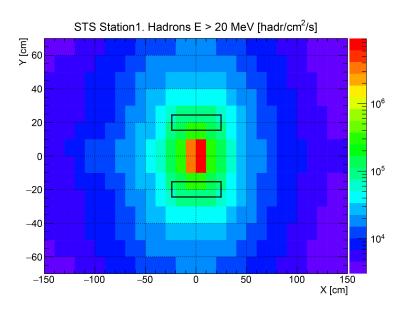

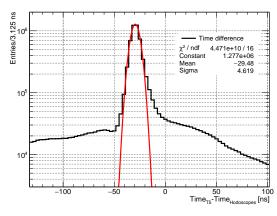

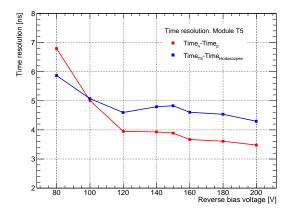

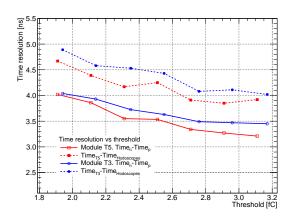

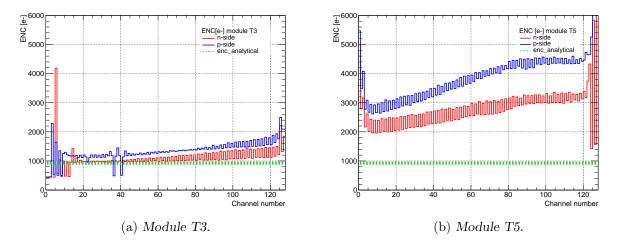

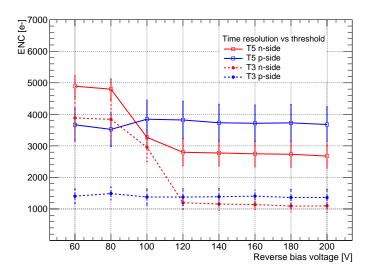

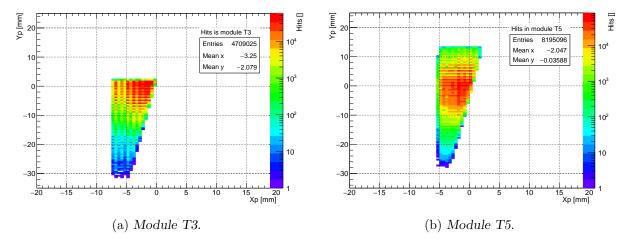

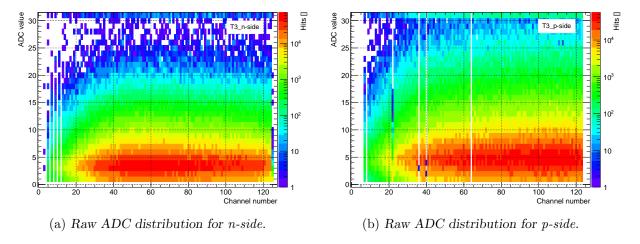

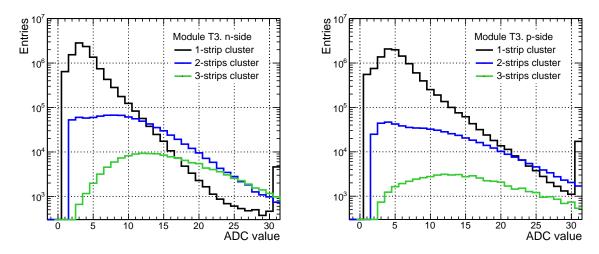

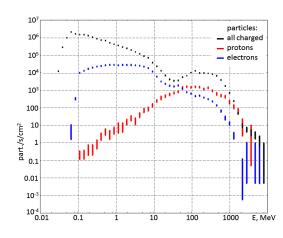

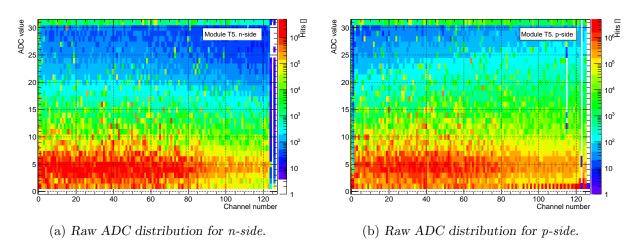

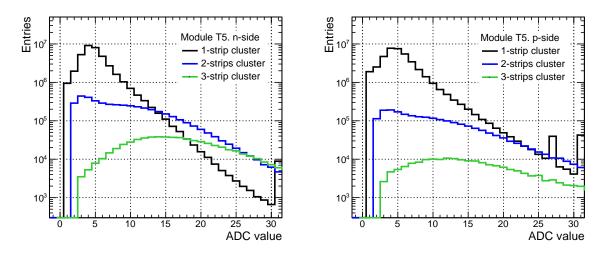

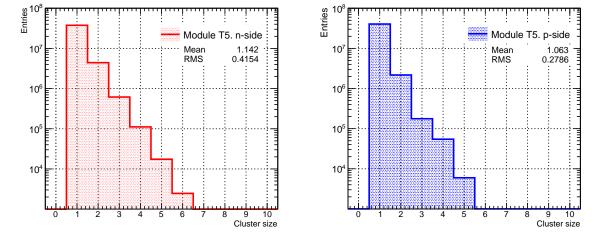

#### Time of Flight (TOF)