## An Erasure-Resilient and Compute-Efficient Coding Scheme for Storage Applications

Dissertation

zur Erlangung des Doktorgrades

der Naturwissenschaften

vorgelegt beim Fachbereich Informatik und Mathematik

der Johann Wolfgang Goethe-Universität

in Frankfurt am Main

von

Sebastian Kalcher

aus Lahn-Gießen

Frankfurt 2013

(D30)

vom Fachbereich Informatik und Mathematik der

Johann Wolfgang Goethe-Universität als Dissertation angenommen.

| Dekan:                 | Prof. Dr. Thorsten Theobald   |

|------------------------|-------------------------------|

|                        |                               |

| Gutachter:             | Prof. Dr. Volker Lindenstruth |

|                        | Prof. Dr. Udo Kebschull       |

|                        |                               |

| Datum der Disputation: | 31.10.2013                    |

## Abstract

Driven by rapid technological advancements, the amount of data that is created, captured, communicated, and stored worldwide has grown exponentially over the past decades. Along with this development it has become critical for many disciplines of science and business to being able to gather and analyze large amounts of data. The sheer volume of the data often exceeds the capabilities of classical storage systems, with the result that current large-scale storage systems are highly distributed and are comprised of a high number of individual storage components. As with any other electronic device, the reliability of storage hardware is governed by certain probability distributions, which in turn are influenced by the physical processes utilized to store the information. The traditional way to deal with the inherent unreliability of combined storage systems is to replicate the data several times. Another popular approach to achieve failure tolerance is to calculate the block-wise parity in one or more dimensions. With better understanding of the different failure modes of storage components, it has become evident that sophisticated high-level error detection and correction techniques are indispensable for the ever-growing distributed systems. The utilization of powerful cyclic error-correcting codes, however, comes with a high computational penalty, since the required operations over finite fields do not map very well onto current commodity processors. This thesis introduces a versatile coding scheme with fully adjustable fault-tolerance that is tailored specifically to modern processor architectures. To reduce stress on the memory subsystem the conventional table-based algorithm for multiplication over finite fields has been replaced with a polynomial version. This arithmetically intense algorithm is better suited to the wide SIMD units of the currently available general purpose processors, but also displays significant benefits when used with modern many-core accelerator devices (for instance the popular general purpose graphics processing units). A CPU implementation using SSE and a GPU version using CUDA are presented. The performance of the multiplication depends on the distribution of the polynomial coefficients in the finite field elements. This property has been used to create suitable matrices that generate a linear systematic erasure-correcting code which shows a significantly increased multiplication performance for the relevant matrix elements. Several approaches to obtain the optimized generator matrices are elaborated and their implications are discussed. A Monte-Carlo-based construction method allows it to influence the specific shape of the generator matrices and thus to adapt them to special storage and archiving workloads. Extensive benchmarks on CPU and GPU demonstrate the superior performance and the future application scenarios of this novel erasure-resilient coding scheme.

## Zusammenfassung

Die sogenannte digitale Revolution, beginnend am Ende des 20. Jahrhunderts, hat unseren Zugang zu Informationen umfassend verändert. Viele Bereiche des gesellschaftlichen Lebens, der Wirtschaft und der Wissenschaft sind mittlerweile stark auf Informationstechnologie angewiesen. Zusammen mit der rasanten Entwicklung der Mikroprozessoren war die Evolution der magnetischen Speichertechnologien einer der Schlüsselfaktoren für den Übergang in eine Informationsgesellschaft. Kostengünstige Datenspeicher mit hoher Kapazität bilden heute die Basis für die große Familie von allgegenwärtigen Geräten, die in die Klasse der *personal computing devices* eingeordnet werden, beispielsweise klassische Arbeitsplatzrechner, tragbare Laptops, Mobiltelefone, Tablet-Computer, sowie Foto- und Videokameras. Besonders der Durchbruch der Halbleiter-Speicher hat die Entwicklung immer kleinerer und robusterer Geräte aus dieser Klasse begünstigt. Aber auch die Entwicklung der professionellen Hochleistungscomputer und deren Speichersysteme wird durch diese Schlüsseltechnologien angetrieben. Besonders diese Art von Computern hat enorme Bedeutung für den wissenschaftlichen Erkenntnisgewinn, aber auch ein breites wirtschaftliches Anwendungsspektrum. Das gewaltige Wachstum der Menge an Informationen, die weltweit erzeugt (oder gewonnen), übertragen und gespeichert wird ist daher wenig überraschend. Schätzungen zu Folge stieg die Gesamtmenge aller gespeicherten Informationen (auf allen gängigen analogen und digitalen Medien) von 2,6 Exabytes<sup>1</sup> in 1986 auf 295 Exabytes in 2007 [1]. Bemerkenswerterweise trugen die digitalen Speichertechnologien erst ab dem Jahr 2000 signifikant zur gesamten Speicherkapazität bei. Nur drei Jahre später wurden geschätzte 90% aller neuen Daten auf magnetischen Medien gespeichert [2] und im Jahr 2007 überholten die digitalen Speicher die analogen endgültig: 52% aller existenten Informationen waren auf Festplatten, 28% auf optischen Medien und 11% auf magnetischen Bändern gespeichert. Neuere Studien aus dem Jahr 2011 quantifizierten die Gesamtmenge aller vom Menschen jemals erzeugten und gespeicherten Informationen auf gewaltige 1,8 Zettabytes [3][4]. Die datenintensiven Wissenschaften gelten neben dem Experiment, der Theorie und der Simulation mittlerweile als vierte essentielle wissenschaftliche Disziplin. Das prominenteste Beispiel kommt aus Gebiet der Teilchenphysik: Der Large Hadron Collider (LHC) der Europäische Organisation für Kernforschung (CERN) in Genf [5] beheimatet sechs unterschiedlich große Experimente die zusammen einige zehn Petabyte an zu speichernden Daten pro Jahr aufnehmen. Aber nicht nur derartige Großforschungsprojekte stellen hohe Anforderungen an die Datenverarbeitungs- und Speichersysteme: Die Entwicklung bildgebenden Sensoren mit Auflösungen Gigapixel-Bereich und immer höher auflösenden Teleskopen stellt die astronomische Forschung vor ähnliche Herausforderungen. Sogar die relativ kompakten DNA-Sequenzierungsgeräte aktueller Bauart produzieren bereits Rohdatenmengen im Bereich einiger Terabyte pro Tag. Mit den immer größer

<sup>&</sup>lt;sup>1</sup>Ein Exabyte steht für 10<sup>18</sup> Bytes.

werdenden Datenmengen müssen natürlich auch die Hochleistungsrechner mit immer größeren Speichersystemen ausgestattet werden, um die Analyse der gewonnen Informationen zu ermöglichen. Doch die Verarbeitung von großen Datenmengen hat nicht nur im wissenschaftlichen Umfeld enorm an Bedeutung gewonnen. Besonders das Geschäftsfeld der Internet Suchmaschinen wäre ohne die Fähigkeit enorme Datenmengen zu sammeln, zu analysieren und zu speichern heute undenkbar. Weiter Beispiele sind elektronische Handelsplattformen und weltumspannende soziale Netzwerke.

Der größte Teil all dieser Daten wird zum Online-Zugriff auf großen Sammlungen von Festplatten vorgehalten, deren Verwaltung und Pflege die Besitzer vor große Herausforderungen stellt: Obwohl die Zuverlässigkeit einer einzelnen Festplatte durchaus beachtlich ist, ergeben sich bei Systemen aus Zehntausenden Festplatten hohe Raten an Fehlerereignissen. Große wissenschaftliche Experimente können aus Kostengründen oft nicht beliebig wiederholt werden und schon eine kurze Unerreichbarkeit im Internethandel kann enorme Verluste erzeugen. Typischerweise werden daher Kopien der Daten erstellt und diese auf (geographisch) verschiedene Rechenzentren verteilt. Da diese Strategien der mehrfachen Replikation relativ kostenintensiv sind, wurden effizientere Verfahren entwickelt. In ihrem berühmten Artikel aus dem Jahre 1988 beschreiben Patterson, Gibson und Katz [6], wie man die Zuverlässigkeit von Sammlungen von Festplatten mit verschiedenen Techniken erhöhen kann. Die Berechnung redundanter horizontaler Paritätsinformationen zur Erzeugung einer einfachen Fehlertoleranz hat sich daraus zum Standard für die folgenden Jahrzehnte entwickelt (RAID). Später kamen diverse Erweiterungen hinzu, die sogar den Ausfall von zwei Festplatten tolerieren können. All diese Verfahren stellen jedoch nur die Spezialfälle der umfassenden mathematischen Theorie der linearen fehlerkorrigierenden Codes dar. Im Rahmen dieser Theorie nutzt man die Werkzeuge der linearen Algebra um das Kodieren und das Dekodieren zu formalisieren. Als besonders leistungsstark haben sich die zyklischen linearen Codes über endliche Körper erwiesen. Die weitverbreiteten Reed-Solomon-Codes [7] erlauben es, zu einer Menge an *n* Nachrichtensymbolen eine frei wählbare Menge an *k* Redundanzsymbolen zu berechnen. Die original Nachricht kann auch dann noch rekonstruiert werden, wenn bis zu k Symbole verloren gegangen sind. Eine Variante dieser Codes eignet sich besonders für den Einsatz in Speichersystemen [8]. Für die *n* Nachrichtensymbole  $d = d_0, d_1, \dots, d_{n-1}$ , müssen *k* Redundanzsymbole  $c = c_1, c_2, \dots, c_{k-1}$ berechnet werden. Mit Hilfe einer speziellen Generatormatrix  $G = (g_{i,j})$ , die von einer Vandermonde-Matrix abgeleitet wird, lässt sich die Kodierung durch eine Matrix-Vektor-Multiplikation darstellen:

$$G\begin{pmatrix} d_0\\ d_1\\ \vdots\\ d_{n-1} \end{pmatrix} = \begin{pmatrix} d_0\\ d_1\\ \vdots\\ d_{n-1}\\ c_0\\ c_1\\ \vdots\\ c_{k-1} \end{pmatrix} = \begin{pmatrix} d\\ c \end{pmatrix}.$$

Nachrichten- und Redundanzsymbole werden nun auf n + k unterschiedliche Speicherkomponenten (zum Beispiel Festplatten) verteilt. Im Falle des Defekts einer Komponente (und dem einhergehenden Verlusten des Nachrichtensymbols  $d_i$ ) wird nun die *i*-te Zeile der Generatormatrix G und des Ergebnisvektors  $(d,c)^T$  gestrichen. Nach k Streichungen erhält man  $G^*$  und  $(d^*,c)^T$ . Das verbleibende Gleichungssystem

$$G^* \begin{pmatrix} d_0 \\ d_1 \\ \vdots \\ d_{n-1} \end{pmatrix} = \begin{pmatrix} d^* \\ c \end{pmatrix}$$

(1)

kann nun gelöst werden. Die Dekodierung entspricht also einer Multiplikation der invertierten reduzierten Matrix mit dem Vektor der noch intakten Symbole:

$$(G^*)^{-1} \begin{pmatrix} d^* \\ c \end{pmatrix} = \begin{pmatrix} d_0 \\ d_1 \\ \vdots \\ d_{n-1} \end{pmatrix} = d$$

(2)

Diese elegante Kodierungsschema hat jedoch einen entscheidenden Nachteil. Bei allen arithmetischen Operationen handelt sich um Operationen auf endlichen Körpern (auch Galois-Körper genannt). Die Symbole sind Elemente des Körpers und repräsentieren Polynome. Alle arithmetischen Operationen sind daher Operationen auf Polynomen. Besonders die Multiplikation zweier Elemente ist deshalb sehr aufwendig und lässt sich schlecht auf die Ausführungseinheiten moderner Prozessoren abbilden. Üblicherweise werden daher die Ergebnisse (oder bestimmte Zwischenergebnisse) der arithmetischen Operationen im Voraus berechnet und in Lookup-Tabellen im RAM gespeichert. Diese spezielle Implementierung hat sich im Laufe der Zeit jedoch als immer problematischer erwiesen. Besonders der Hauptspeicher hat sich zu einem Flaschenhals in modernen Computern entwickelt, begründet durch die ungleiche Entwicklung der Prozessorleistung und der Zugriffs-Latenzen des Speichers. Der häufige Zugriff auf große Datenstrukturen im Hauptspeicher kann daher die Leistung eines Programms stark beeinträchtigen. Für effiziente Algorithmen kann es daher durchaus vorteilhaft sein, bestimmte Daten on-the-fly neu zu berechnen, anstatt diese aus dem RAM anzufordern. Immerhin können moderne Prozessor-Cache vorhanden ist), einige hundert Instruktionen ausführen [9].

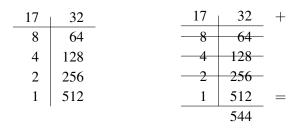

Kern dieser Arbeit ist ein Kodierungsverfahren, das speziell auf moderne Mehrkern-Prozessoren mit breiten Vektoreinheiten und auf aktuelle Beschleuniger-Architekturen mit Hunderten von Kernen angepasst ist. Die Basis ist ein fehlerkorrigierender Code über einem endlichen Körper (ähnlich den Reed-Solomon-Codes). Die Lookup-Tabellen für die Multiplikation sind durch einen polynomiellen Algorithmus (Abbildung 1) ersetzt. Sowohl eine auf den *Streaming SIMD Extensions (SSE)* basierte Vektor-Implementierung für Haupt-Prozessoren, als auch eine Implementierung, die moderne Grafikprozessoren als Co-Prozessoren verwendet, werden vorgestellt. Hierbei werden lediglich komponentenweise UND und Exklusiv-ODER, sowie Schiebeoperationen und Vergleiche benötigt. Die Elemente

```

1: procedure GFMULT POLY(a,b)

2:

p \leftarrow 0

while a \neq 0 AND \mathbf{b} \neq \mathbf{0} do

3:

4:

if LSB(b) = 1 then

5:

p \leftarrow p \oplus a

end if

6:

7:

msb\_set \leftarrow MSB(a)

a \leftarrow LeftShiftByOne(a)

8:

9:

if msb\_set = 1 then

10:

a \leftarrow a \oplus PP

11:

end if

12:

b \leftarrow RightShiftByOne(b)

13:

end while

return p

14:

15: end procedure

```

Abbildung 1.: Polynomielle Multiplikation über einem endlichen Körper. LSB(x) gibt das *least significant bit* von x zurück, MSB(x) liefert das *most significant bit* von x. PP bezeichnet das primitive Polynom mit dem der endliche Körper erzeugt wurde.

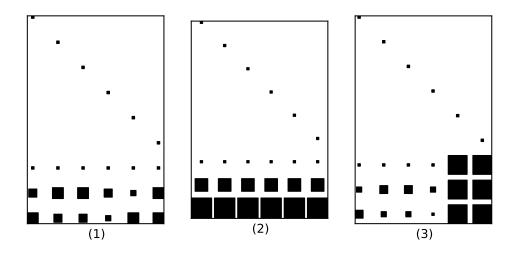

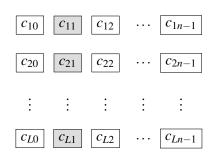

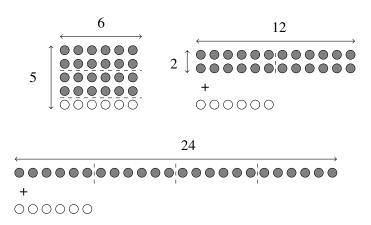

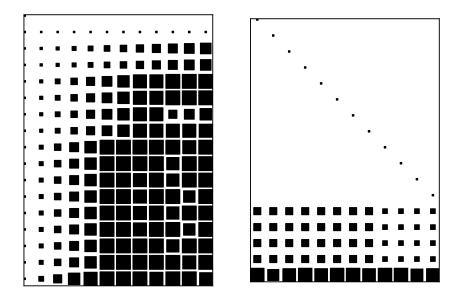

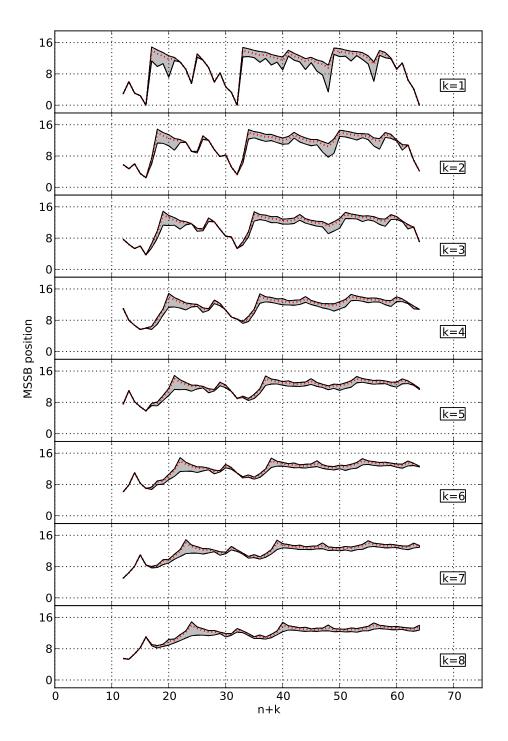

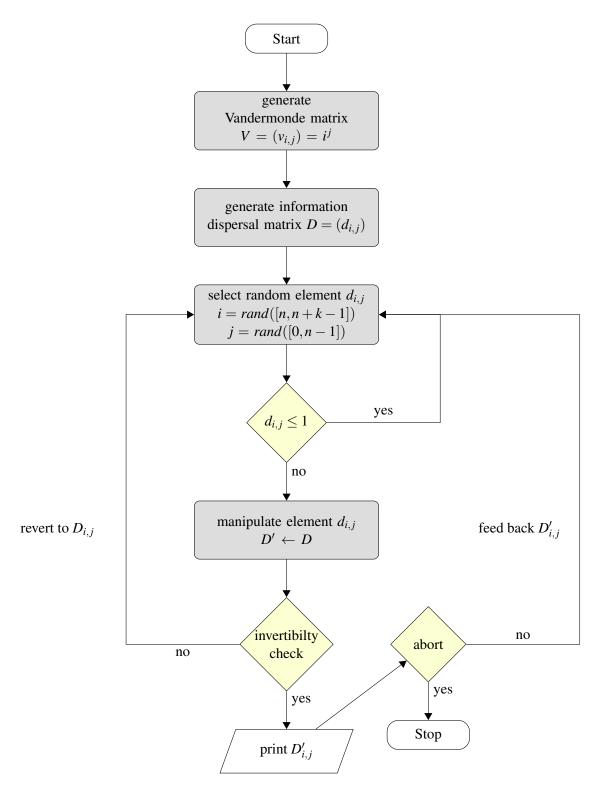

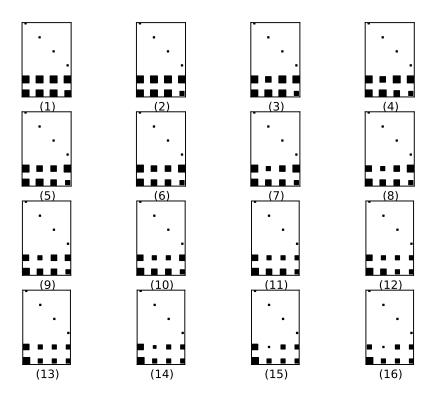

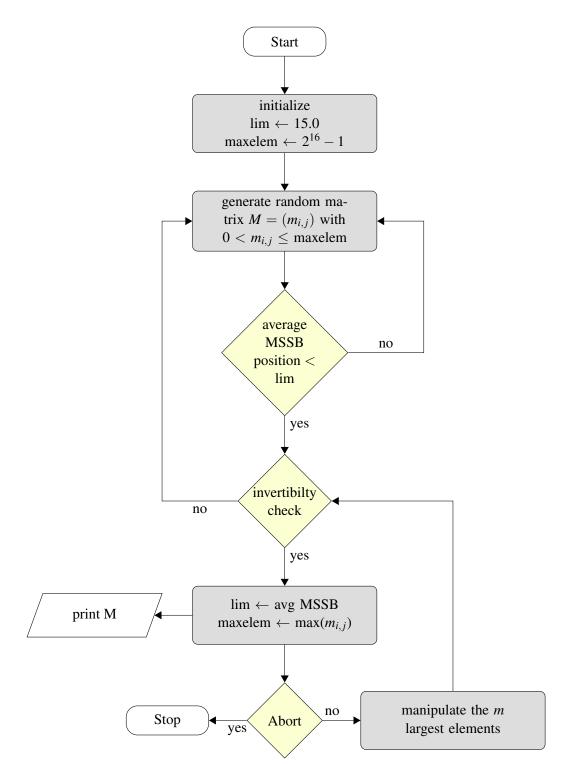

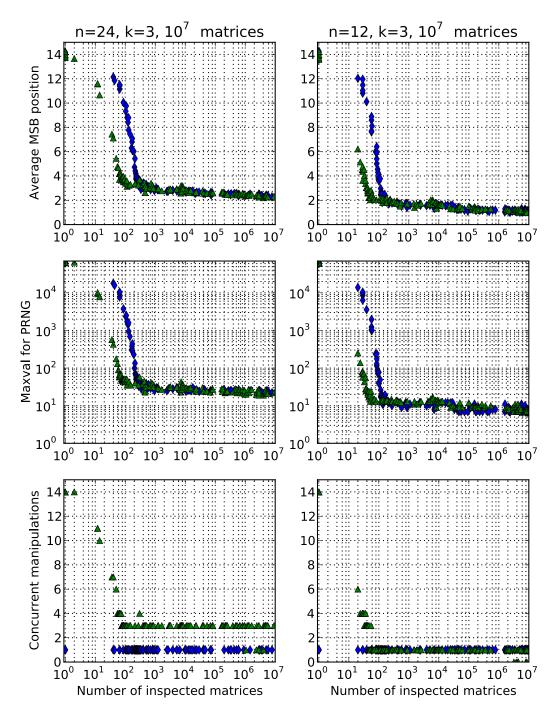

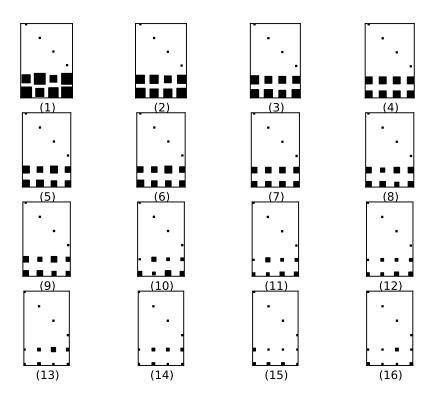

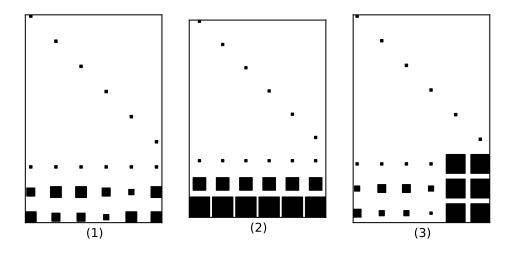

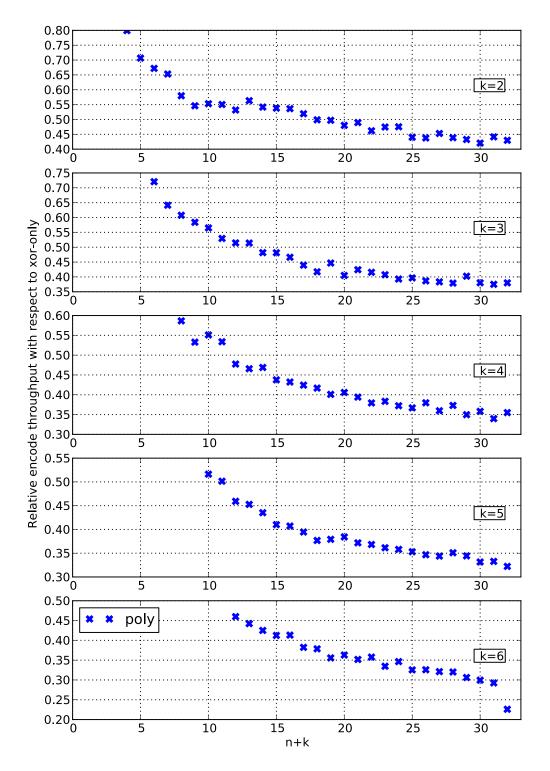

der Flusskontrolle lassen sich dabei gut auf die Gegebenheit der jeweiligen Architektur abbilden. Eine genauere Betrachtung des polynomiellen Algorithmus zeigt, dass die Multiplikation bei einer vorteilhaften Verteilung der polynomiellen Koeffizienten (in zumindest einem der Faktoren) stark beschleunigt werden kann. Da im Bezug auf die zu kodierenden Daten keine Einschränkungen gemacht werden sollten, bieten sich nur die Elemente der Generatormatrix an, um die beschleunigte Multiplikation nutzbar zu machen. Eine eigehende Untersuchung aller primitiven Polynome des gewählten Körpers zeigt, dass sich mit der ursprünglichen algebraischen Konstruktion der Generatormatrix allein kein zufriedenstellendes Ergebnis erzielen lässt. Daher werden verschiedene Heuristiken vorgestellt, mit denen sich Generatormatrizen von besonderer Güte erzeugen lassen. Besonders vielseitig zeigt sich hierbei ein Monte-Carlo Verfahren. Damit lassen sich nicht nur Matrizen erzeugen, bei denen der Rechenaufwand pro Element besonders gut balanciert ist, sondern auch solche, bei denen sich die Verteilung der polynomiellen Koeffizienten zwischen verschiedenen Zeilen oder Spalten stark unterscheidet. Es können also Generatormatrizen mit bestimmten Strukturen erzeugt werden. Ist zum Beispiel eine besonders schnelle Berechnung des ersten Redundanzsymbols gewünscht, so kann der Rechenaufwand für dieses auf Kosten des Rechenaufwands für die weiteren Symbole reduziert werden (tatsächlich kann die Berechnung sogar auf die einfache Parität zurückgeführt werden). Diese begünstigt eine verzögerten Berechnung der höhergradigen Fehlertoleranzsymbole, entweder in Zeiten geringerer Last oder erst nachdem entschieden wurde, dass eine höherer Grad an Ausfallsicherheit für die jeweiligen Daten gewünscht ist. Damit besitzt das Verfahren eine bisher unbekannte Flexibilität und erlaubt eine anwendungsspezifische Optimierung. Abbildung 2 zeigt verschiedene Beispiele. Da es sich um einen systematisch Code handelt, findet sich in den ersten n Zeilen die Identitätsmatrix.

Abbildung 2.: Illustration der anwendungsspezifischen Generatormatrizen. Die Größe der gefüllten Quadrate zeigt den Rechenaufwand für das jeweilige Matrixelement an.

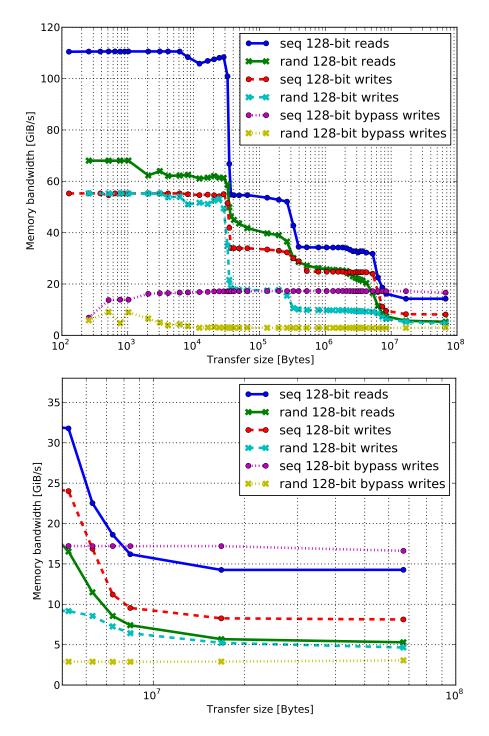

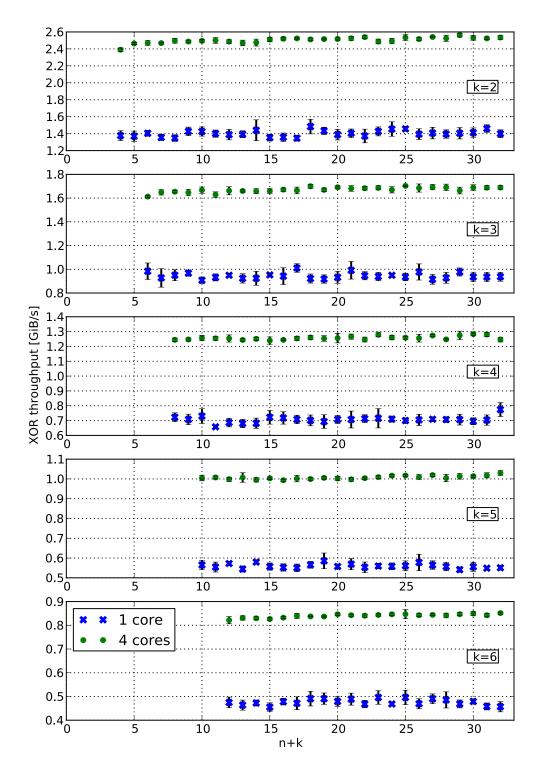

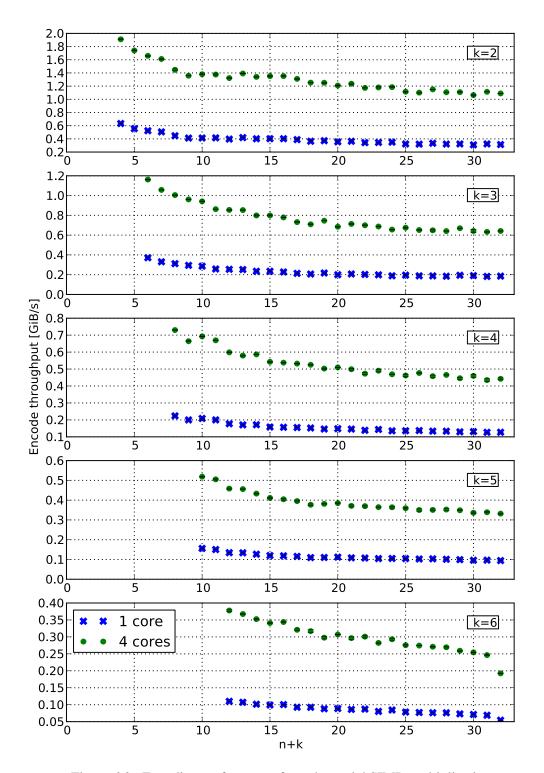

Umfangreiche Benchmark-Tests belegen die Leistungsfähigkeit dieses Kodierungsverfahrens. Mit Hilfe der vektorisierten Implementierung der Multiplikation ist es möglich die Kodierung und Dekodierung auf handelsüblichen Prozessoren mit ausreichender Leistung durchzuführen. Die erforderlichen Vektor-Instruktionen sind über eine weite Bandbreite von Prozessoren unterschiedlicher Hersteller und Preisklassen verfügbar. Zudem belegen die Leistungsmessungen der GPU-Implementierung, dass sich moderne Grafikkarten als leistungsstarke Co-Prozessoren für Kodierungsaufgaben anbieten. Für einige Konfigurationen ist deren Kodierungsleistung sogar nur durch die limitierte Bandbreite des PCI Express-Busses beschränkt. Damit lassen sich Durchsätze erreichen, die vergleichbar mit denen von modernen Hochgeschwindigkeitsnetzwerken wie zum Beispiel InfiniBand oder 10GbE/40GbE sind. Die Kombination aus einem arithmetisch intensiven Multiplikationsalgorithmus mit darauf optimierten Generatormatrizen zeigt sich demnach als besonders geeignet für die verschiedenen aktuellen Prozessorarchitekturen. Im Hinblick auf die zukünftige Entwicklungen in Richtung breiterer Vektoreinheiten und einer höheren Anzahl an einfachen Ausführungseinheiten zeigen erste Tests, dass das Verfahren davon stark profitieren kann. Untersuchungen zur tatsächlichen Integration des Kodierungsverfahrens in großskalige Massenspeichersysteme (zum Beispiel Lustre oder FraunhoferFS) haben bereits begonnen.

# Contents

| 1. | Intro | duction                                               | 1  |

|----|-------|-------------------------------------------------------|----|

|    | 1.1.  | Organization of the thesis                            | 4  |

| 2. | Stora | age Technologies                                      | 5  |

|    | 2.1.  | Storage hierarchy                                     | 5  |

|    | 2.2.  | Magnetic disk storage                                 | 8  |

|    | 2.3.  | Solid state storage                                   | 12 |

|    | 2.4.  | Disk micro-benchmark                                  | 14 |

|    | 2.5.  | Reliability modeling and failure modes                | 20 |

|    | 2.6.  | Real world data                                       | 33 |

|    | 2.7.  | Conclusions                                           | 35 |

| 3. | Fault | -Tolerance and Reliability in Current Storage Systems | 37 |

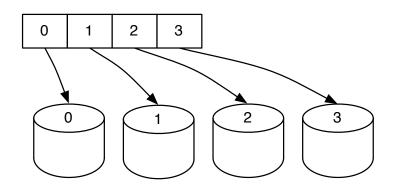

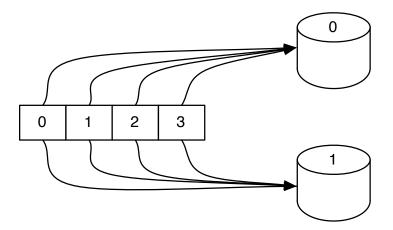

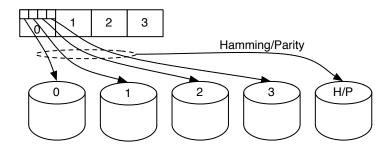

|    | 3.1.  | RAID (block storage)                                  | 37 |

|    | 3.2.  | ZFS                                                   | 42 |

|    | 3.3.  | Lustre                                                | 42 |

|    | 3.4.  | Ceph                                                  | 44 |

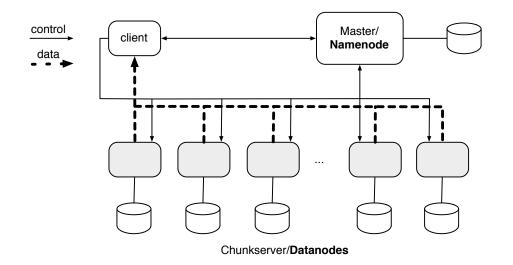

|    | 3.5.  | GoogleFS/HDFS                                         | 44 |

|    | 3.6.  | Summary                                               | 45 |

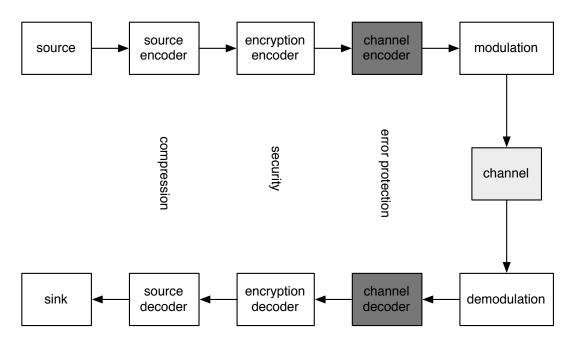

| 4. | Error | r-Correcting Codes                                    | 47 |

|    | 4.1.  | Introduction                                          | 48 |

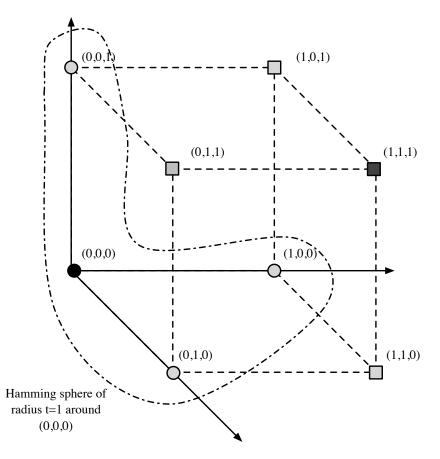

|    | 4.2.  | Basic definitions                                     | 49 |

|    | 4.3.  | Linear codes                                          | 52 |

|    | 4.4.  | Bounds for codes                                      | 54 |

|    | 4.5.  | Error detection and correction                        | 55 |

|    | 4.6.  | Erasure codes                                         | 56 |

|    | 4.7.  | Cyclic linear codes                                   | 57 |

|    | 4.8.  | Galois fields                                         | 59 |

|    |       | BCH codes                                             | 60 |

|    |       | Reed-Solomon codes                                    | 62 |

|    | 4.11. | Decoding of BCH and Reed-Solomon codes                | 63 |

|    |       | Vandermonde-based Reed-Solomon erasure codes          | 65 |

|     | 4.13. Cauchy Reed-Solomon codes              | 69  |

|-----|----------------------------------------------|-----|

|     | 4.14. Summary                                | 70  |

|     |                                              |     |

| 5.  | A SIMD-optimized Coding Scheme               | 71  |

|     | 5.1. Introduction                            | 71  |

|     | 5.2. Table-based multiplication              | 73  |

|     | 5.3. Polynomial implementation               | 74  |

|     | 5.4. Vectorization                           | 77  |

|     | 5.5. GPU as co-processor                     | 82  |

|     | 5.6. Low MSSB generator matrices             | 86  |

|     | 5.7. Generating low average MSSB matrices    | 92  |

|     | 5.8. Special-purpose generator matrices      | 99  |

|     | 5.9. Algebraic signatures                    | 100 |

|     | 5.10. Summary                                | 103 |

| ~   | Deculte and Developments                     | 105 |

| 6.  | Results and Benchmarks                       | 105 |

|     | 6.1. Testbeds                                | 105 |

|     | 6.2. Multiplication                          |     |

|     | 6.3. Matrices                                |     |

|     | 6.4. SIMD coding                             |     |

|     | 6.5. GPGPU coding                            |     |

|     | 6.6. Decoding                                |     |

|     | 6.7. Algebraic signatures                    |     |

|     | 6.8. Related work                            |     |

|     | 6.9. Outlook to upcoming vector instructions |     |

|     | 6.10. Summary                                | 129 |

| 7   | Summary and Conclusion                       | 131 |

| 1.  |                                              | 131 |

| 8.  | Bibliography                                 | 133 |

|     |                                              |     |

| Α.  | Appendix                                     | 143 |

|     | A.1. The Galois field $GF(2^{16})$           | 143 |

|     | A.2. Low MSSB generator matrices             | 147 |

|     | A.3. Vandermonde matrices                    | 156 |

|     | A.4. Testbeds                                | 157 |

| Lie | st of Tables                                 | 161 |

| LIS |                                              | 161 |

| Lis | at of Figures                                | 163 |

| Inc | lex                                          | 167 |

## 1. Introduction

The so-called *digital revolution* in the past few decades has profoundly changed the access to information. Rapid developments in digital computing and communication have marked the beginning of the information age and today many parts of modern economy and society rely deeply on information technology. The rise of electronic commerce, the global development of the communication and finance sectors, but also the influences on education, health, and even aspects of social life are consequences of this remarkable transition. Together with rapid advancements in microprocessor technologies, the innovation in magnetic disk storage has been among the key factors for this development. Inexpensive, high capacity data storage devices have been the technological basis for both, the ubiquitous personal computing devices, but also for large-scale professional computing and storage systems. More recently, mass production of solid state storage devices has further enabled portable computing and communication equipment, as well as high-capacity digital photo and video cameras, and various portable entertainment devices. Unsurprisingly, the amount of information that is created or captured, communicated, and stored worldwide has tremendously grown over the past decades. An overview of the different prefixes that are used subsequently to quantify information is shown in Table 1.1. It is

| Decimal prefix | Value           | Binary prefix | Value           |

|----------------|-----------------|---------------|-----------------|

| kilo           | 10 <sup>3</sup> | kibi          | 2 <sup>10</sup> |

| mega           | $10^{6}$        | mebi          | $2^{20}$        |

| giga           | $10^{9}$        | gibi          | $2^{30}$        |

| tera           | $10^{12}$       | tebi          | $2^{40}$        |

| peta           | $10^{15}$       | pebi          | $2^{50}$        |

| exa            | $10^{18}$       | exbi          | $2^{60}$        |

| zetta          | $10^{21}$       | zebi          | $2^{70}$        |

| yotta          | $10^{24}$       | yobi          | 2 <sup>80</sup> |

Table 1.1.: Decimal and binary prefixes for bits and bytes.

estimated that the total amount of (optimally compressed) data which is stored worldwide by the most widely used analog and digital storage technologies has increased from 2.6 exabytes in 1986 to 295 exabytes in 2007 [1]. Remarkably, the digital storage technologies have only contributed notably to the overall capacity from the year 2000 on. Only three years later it was estimated that more than 90% of all new information was stored on magnetic media [2] and by 2007 digital storage had become the dominant storage technology with 52% of all information stored on hard disks, 28% on optical media, and 11% on digital tape. More recent studies estimate that in 2011 the total amount of information

#### 1. Introduction

created and replicated surpassed the astonishing mark of 1.8 zettabytes [3][4]. Extrapolating with these growth rates, the amount of information will soon become comparable to the approximately  $10^{23}$  bits that are stored in the DNA of an adult human [1]. Clearly, both numbers are dwarfed by the estimated  $10^{90}$  bits of storage capacity of the entire observable universe [10].

The enormous growth of information is not only based on personal data. Data-intensive science is today seen as the fourth major scientific discipline, aiming to connect experimental science, theoretical science, and simulation [11]. In this context data-intensive science is an umbrella term covering many sub-disciplines including data capturing and curation, as well as data analysis and visualization. Prominent examples are found in various fields of science: The Large Hadron Collider at the European Organization for Nuclear Research CERN hosts six detector experiments of different sizes: ALICE, AT-LAS, CMS, TOTEM, LHCb, and LHCf [5]. The main task of the ALICE experiment, for example, is the study of lead ion collisions. The peak read-out rate into the front-end electronics of this experiment is about 6 terabytes/s, which is reduced through various selection steps (the so-called triggers [12]) to around 1 gigabyte/s. Similar amounts are produced by the other three large experiments, with the result that the combined amount of recorded data at CERN in 2010 was 13 petabytes [13]. While the data generation rates in high-energy physics are certainly remarkable, they are not exceptional. The development of multi-gigapixel imaging sensors and the increasing size of telescopes also requires the field of astronomy to manage large data collections in the order of tens of petabytes per year [14]. Modern high-throughput DNA sequencing systems enable genome analysis at unprecedented time scales, delivering terabytes of raw data per day from relatively compact machines. This has allowed for cataloging and processing the genome of several thousands of individuals, followed by widespread distribution for further scientific analysis [15]. Due to the ever-increasing resolution and complexity of sensors and detectors, many future projects are expected to fit the category of data intensive problems. The same is true for the increasing HPC computing capabilities: The transition to exascale science is anticipated for 2018, with estimated storage requirements between 500 and 1000 petabytes per supercomputer installation [16]. An added challenge after the immediate capturing and analysis of data is the long-term storage and preservation of the data. Many guidelines for good scientific practice demand the secure and durable storage of primary data sets for at at least ten years after publication.

The ability to gather and analyze large amounts of data is not only crucial for science, today various business models rely heavily on the ability to handle the so-called *big data*<sup>1</sup>. The most prominent example is internet search. The amount of data that is processed to maintain and update an index of the web is so large, that it cannot be handled by classical database and storage systems. Google claims that their indexing system stores several tens of petabytes per day, while handling billions of updates [17]. In 2011 it was estimated<sup>2</sup> that Google was using around 900,000 individual servers in their global network of data centers [18]. Many of these search-related problems have been the driving factor for

<sup>&</sup>lt;sup>1</sup>Big data is a loosely defined term, covering, generally speaking, all data sets, that are so huge that they require massively parallel software and hardware to be handled.

<sup>&</sup>lt;sup>2</sup>Unfortunately, many companies consider the size and the architecture of their IT infrastructure a trade secret. The numbers are usually estimated from secondary information (such as power consumption, number of customers, or number of public IP addresses), nonetheless they are useful to illustrate the size of the data sets that are handled by companies today.

novel techniques and paradigms for distributed processing of big data which have been quickly applied to other problems in in business and science. Another example is the electronic commerce company Amazon. Initially focussed on online retail, the company has become one of the biggest providers for computing services. They operate a global cloud computing platform using around 450,000 servers (estimation for 2012 [19]). An essential part of this platform is a fully redundant storage service which was estimated to store around 566 petabytes of data in 2011 [20]. Several secondary cloud storage vendors for consumers as well as for enterprises rely on the Amazon platform as underlying storage system. A last example for big data in the business context is the social network Facebook. They reported 955 million of monthly active users in June 2012, requiring more than 100 petabytes storage, mainly for the pictures<sup>3</sup> and videos of the users [22].

A large fraction of the data of all these applications is stored on huge collections of magnetic disks for on-line access. Data management at this scale has become a tremendous challenge. For many of the large scientific experiments a loss of primary data is a catastrophic event, since the repetition of the experiment is often simply to expensive. Even unavailability of data for short periods of time can have significant economic consequences (for example due to lost sales or advertisement). Typically these dangers are addressed by creating multiple copies, possibly distributed across different geographical locations. While simple replication is relatively inexpensive in terms of implementation and computational overhead, it clearly is very expensive regarding the additionally required storage capacity. With increasing size of storage systems, a sophisticated way to deal with failures (beyond replication) becomes crucial. In their famous paper from 1988 on redundant arrays of inexpensive disks (RAID), Patterson, Gibson, and Katz described several techniques to increase the reliability of collections of disks beyond replication [6]. Using the horizontal parity over all involved disk has become the standard for achieving single disk failure tolerance in the following decades. Several two failure resilient schemes have been proposed as extension to the horizontal parity. As it turns out, all these specialized approaches can be seen as the edge cases of the very refined theory of linear error-correcting codes. In this theory, the generation of codes, as well as the encoding of messages and the decoding of code words are formalized in the language of linear algebra. Hence many familiar techniques and tools can be applied (this is discussed in depth in Chapter 4). Within the framework of coding theory, sophisticated error and erasure correcting codes with the capability to tolerate an arbitrary, adjustable number of failures can be constructed. These codes can be designed such that they require only the theoretical minimum of additional storage space. The price for this flexibility is a higher computational overhead. Several codes (among them the ubiquitous Reed-Solomon codes [7]) operate on finite fields and their symbols are seen as coefficients of polynomials over those finite fields. Since polynomial arithmetic does not map very well onto modern processor architectures, the results of certain arithmetic operations have traditionally been pre-calculated and stored in lookup tables. The strategy to store results of arithmetic operations in memory to avoid recalculation has been successful for the last decades. However, the memory subsystem has become one of the main bottlenecks in commodity systems today. Frequently accessing large in-memory data structures from inner loop code can severely impact the overall performance. Due to the ever increasing disparity between the instruction throughput of processors

<sup>&</sup>lt;sup>3</sup>In December 2011 Facebook published that, on average, 250 million photos are uploaded per day [21].

#### 1. Introduction

and the access times of memories, it is worthwhile to examine whether it is faster to calculate a certain arithmetic result just-in-time, instead of fetching the pre-calculated result from memory. After all, modern processors are able to issue in the order of hundred instructions during the time it requires to load an uncached word from memory [9]. Decoupling the arithmetic code from cached data structures can also be beneficial for scalability in terms of utilization of vector units and utilization of multiple processor cores.

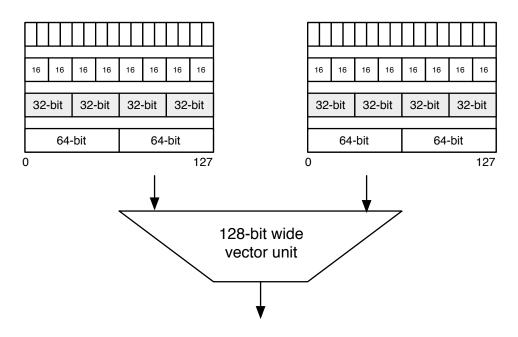

In this thesis a novel coding scheme is presented which is designed for modern multi-core commodity processors with wide vector units, as well as for modern many-core devices (such as GPUs) that are used in a co-processor fashion. The table-based multiplication algorithm (for finite fields) has been replaced by a (vectorized) polynomial multiplication with modular reduction. Depending on the distribution of the polynomial coefficients in the factors, the multiplication can be vastly accelerated. Since a favorable distribution of the polynomial coefficients cannot be assumed for arbitrary data<sup>4</sup>, the focus of this thesis has been the distribution of polynomial coefficients in the elements of the generator matrices of the erasure correcting code. Sine the classical algebraic construction methods of the generator matrices do not produce matrices with elements that are optimal in terms of the distribution of polynomial coefficients, several heuristics have been developed to find better generator matrices. The most versatile method follows a Monte-Carlo approach and, therefore, allows to influence the specific shape of the generator matrix. In this way it is possible to create special purpose generator matrices which have distinct advantages for special use cases (for example different computational costs for different levels of fault tolerance). The combination of polynomial multiplication and suitable generator matrices proves to be very beneficial for both execution on modern CPUs as well as on many-core accelerator devices. A helpful addition to the coding scheme is an algebraic signature that also operates on finite fields. These signatures can be used as checksums for larger data blocks and they retain their validity through the encoding step. In conclusion, the coding scheme presented in this thesis addresses the challenge of efficient execution of the coding operations on modern off-the-shelf components. Hence it provides a means to economically increase reliability, availability, and integrity of data in modern large-scale storage systems.

### 1.1. Organization of the thesis

The thesis is organized as follows. In Chapter 2 a short review of secondary storage technologies is presented. Chapter 3 gives an overview about approaches to achieve fault-tolerance and reliability in current storage systems. An introduction into the theory of error- and erasure-correcting codes is given in Chapter 4. This is the foundation for a detailed discussion of a novel compute-efficient coding scheme presented in Chapter 5. Chapter 6 shows the performance characteristics of the coding scheme for the two different usage scenarios, the vectorized implementation for execution on a modern SIMD-enabled CPU, and a many-core version which is run on a modern GPU-based co-processor. The final chapter gives a conclusion and provides an outlook for further research.

<sup>&</sup>lt;sup>4</sup>In fact, most high-entropy data storage formats display a uniform distribution of the polynomial coefficients.

## 2. Storage Technologies

This chapter gives a short overview of the important (secondary) storage technologies and their characteristics. The first sections reviews the hierarchy of storage technologies in relation to access time, capacity and relative cost. The following sections describe the essentials of magnetic disk and solid state storage. A micro-benchmark for hard disks is presented subsequently, illustrating the characteristics of a system composed of rotating disks. In the final section the reliability models of disks and secondary storage systems composed of disks are discussed.

## 2.1. Storage hierarchy

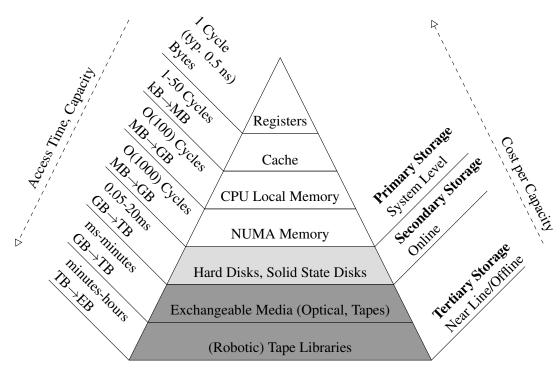

Figure 2.1.: Storage hierarchy [23].

An overview of the hierarchy of storage technologies is shown in Figure 2.1. Access times and available capacities are increasing while going from the top towards the base, whereas the opposite is true for cost

| Device                     | Capacity     | Typical price |

|----------------------------|--------------|---------------|

| CPU registers <sup>1</sup> | $\sim$ 4 KiB | 2000 EUR/CPU  |

| CPU cache                  | 24MiB        | 2000 EUR/CPU  |

| CPU local RAM              | 256 GiB      | 3.200 EUR     |

| Multi CPU NUMA RAM         | 1 TiB        | 12.800 EUR    |

| Hard disks                 | 4 TB         | 300 EUR       |

| Solid state disks          | 512 GB       | 1000 EUR      |

| Optical media (Blue Ray)   | 50 GB        | 10 EUR        |

| Tapes                      | 5 TB         | 300 EUR       |

| Full tape library [24]     | 1 EB         | N/A           |

Table 2.1.: Capacities and prices for top-of-line storage devices commercially available in 2012

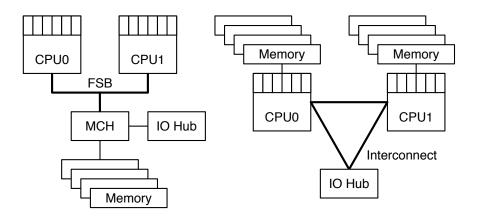

per capacity. Capacities and typical prices for several top-of-line products are presented for reference in Table 2.1. The *primary storage* devices are used at system level and include mainly volatile memory system that are rather close to the CPU. Registers and caches are typically a part of the processor and reside therefore on the same die. On modern multiprocessor systems a fraction of the total random access memory is usually directly attached to each CPU. These configurations are called *non-uniform memory architecture* (*NUMA*). From the view of the single processor the local memory has lower access latencies and can be accessed directly, while access to the remote memories requires transfers over some intermediate system I/O network. The following layer of *secondary storage* includes persistent online storage devices such as *hard disk drives* (*HDDs*) and *solid state drives* (*SSDs*). Due to their performance characteristics SSDs are often used in a caching layer on top of large scale HDD-based storage systems. All devices that use exchangeable media, such as optical disks and magnetic tapes and larger archival libraries that are built thereof, form the layer of *tertiary storage* devices. Tertiary storage can be characterized as offline storage, as random access is not always possible and explicit media change is often necessary. While reliability is evidently a critical issue for all storage components, the following sections are dedicated to the middle layer of secondary storage devices.

Today there are mainly two technologies for secondary storage: Rotating magnetic disks and solid state storage. While non-volatile solid state storage devices have been available from the early 1970s [26], the utilization of solid state devices for (mass market) persistent secondary storage is a relatively new development. Around the year 2004 several vendors started offering devices with SATA, SAS, and ATA interfaces on a larger scale, however, capacities were several orders of magnitudes lower than for hard drives and prices were several orders of magnitudes higher. The origins of magnetic disk storage on the contrary are in the 1950s [27]. Growing demand for online storage with the possibility for random access drove the transition from punchcards and magnetic tapes to rotating magnetic disks.

<sup>&</sup>lt;sup>1</sup>Counting the 16 general purpose 64-bit registers and the 16 256-bit vector registers. The actual number of registers can be larger, since not all registers are exposed.

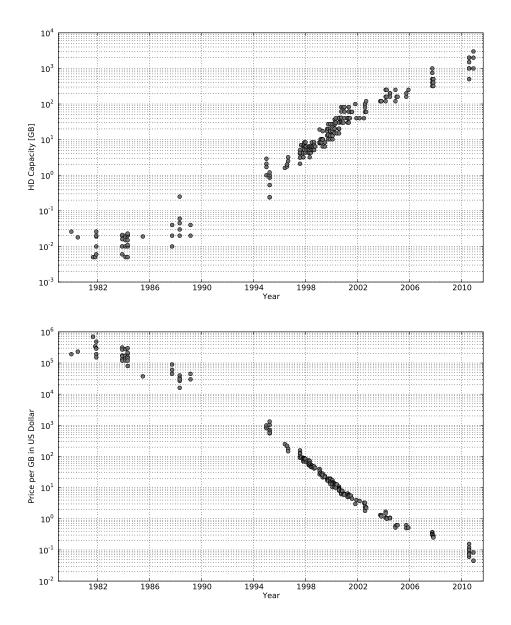

Figure 2.2.: Development of hard disk capacities and relative costs [25].

The first patent describing a magnetic data storage machine based on a set of rotating disks was granted in 1964 [28]. Several decades of active research and continuous development and innovation have lead

to a remarkable role of magnetic disk storage today. In 2003 it was estimated that 92 % of all new information is stored on magnetic media, primarily hard disks [2], and the total amount of hard disk storage worldwide at the end of 2008 was estimated at roughly 200 exabytes [29]. The development of hard disk capacities and relative prices is shown in Figure 2.2. This plot of historical data illustrates one of the reasons for the success of magnetic disks: the aerial storage density doubles approximately every 12 to 18 months, in analogy to the well known law for the doubling of the transistor count by Gordon Moore, this is known as Kryder's law [30, 31]. The relative price for magnetic disk storage on the other hand has been decreasing with the same pace.

### 2.2. Magnetic disk storage

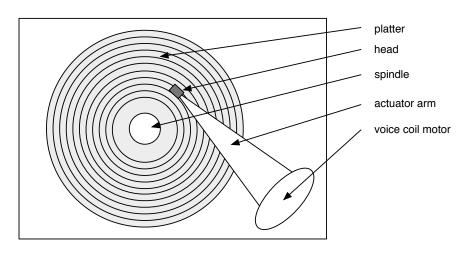

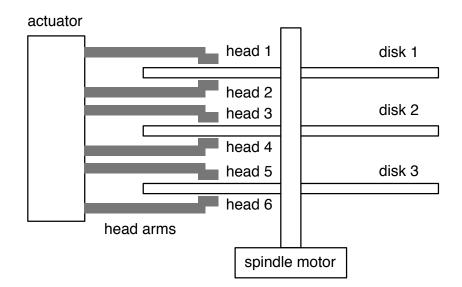

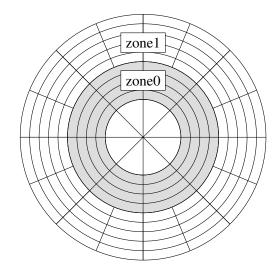

Figure 2.3.: Top view of a hard disk

A generic view of a hard disk drive is depicted in Figures 2.3 and 2.4. In general it consists of a collection of platters which rotate on a spindle at a fixed number of revolutions per minute [32]. The platters themselves are built of three layers: The rigid substrate (based on metal, glass or ceramic), a layer of magnetic recording material, and a protective overcoat layer [33, 34]. The substrate must be extremely uniform, free of material defects, and unsusceptible to thermal expansion. The magnetic recording material consists of several thin film layers [35] (for example containing Cobalt, Chromium, and Platinum) with different properties. The thin overcoat layer protects against microscopic particles, dust, and vapors. Multiple platters are arranged on top of each other with enough space between them to allow both sides of the platter to be accessed by an actuator arm. In principle it is possible to stack as many platters as needed, however, current disks contain only up to five platters to limit the number of mechanical components and control the vibration and power consumption. The read and write heads are positioned at the tip of the actuator arm and the distance between the head and the platter is only several nanometers in modern disks. The heads are responsible for storing and reading back data on the magnetic layer. Individual bits are stored in sub-micrometer-sized regions containing a small number

Figure 2.4.: Hard disk side view.

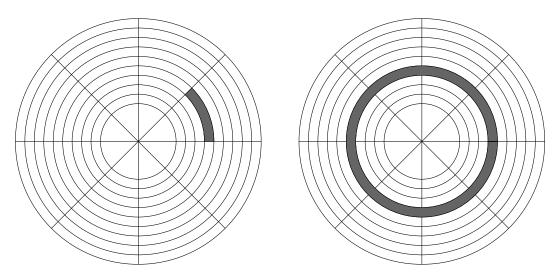

of magnetic grains. Originally, longitudinal magnetization (parallel to the plane of the disk) was used. However, starting in 2005 manufacturers switched to perpendicular magnetization in order to achieve higher storage densities. In 2012 the highest magnetic storage density achieved was one terabit per square inch [36]. Consecutive bits are stored in the circumferential direction of the platter, forming the so-called *track*. Tracks are subdivided into *sectors* which are the smallest accessible unit for data storage. Sectors contain header information, the actual data and a field containing information for error-correction. Traditionally sectors contained space for 512 bytes of user accessible data, however, starting in 2009 a transition to a capacity of 4096 bytes per sector has begun. This allowed for better storage efficiency and it was possible to introduce stronger error-correcting capabilities. The concepts of tracks and sectors are illustrated in Figure 2.5.

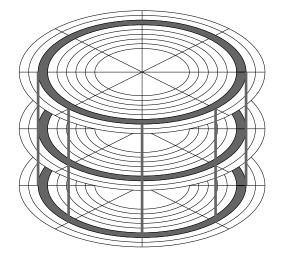

All tracks with equal radius on different disks form a *cylinder*, as shown in Figure 2.6. The write head consists of a micro-fabricated electromagnet which induces a magnetization in the region of an individual bit. The read head, on the other hand, uses the *giant magnetoresistance (GMR)* or *tunnel magnetoresistance (TMR)* effects to detect the stray field at the bit region borders. Both are quantum mechanical effects which manifest as a significant change in the electrical resistance depending on the parallel or anti-parallel orientation of the magnetization of neighboring ferromagnetic layers [37]. To achieve precise positioning of the read and write heads, the movements of the actuator arm are controlled by voice coil motors. The platters on the spindle are directly connected to the spindle motor, which has to maintain a constant speed with minimal vibration. This is achieved by using a servo-controlled closed loop which reads servo information embedded on the magnetic surface between the actual data elements. The final component is the disk controller hardware and its associated firmware. The controller is responsible for actually performing the conversion from the digital information to the magnetic signal on the media using sophisticated signal amplification and processing. Furthermore, it

Figure 2.5.: Sector (left) and track (right).

Figure 2.6.: Cylinder.

manages the communication with the host CPU, performs command queueing and scheduling, provides error-correction and data integrity checks, manages buffering, and also controls the servo loop.

The market for hard disks is divided into three major categories: Desktop, nearline and enterprise disk drives [38]. These categories reflect different usage models with very different requirements in terms of robustness, reliability, performance, features, and cost. Desktop (and laptop) drives are designed for non-contiguous operation and a low duty cycle with a strong focus on power consumption, capacity, and low cost. Nearline devices provide high storage capacities with increased reliability. They are designed for continuous availability with a moderately higher workload as desktop drives. Nearline hard drives are used in scenarios where large amounts of data need to be available at all times without interruption (bulk storage), but without the highest demands on performance and throughput, such as

|                          | Desktop                      | Nearline                     | Enterprise                   |

|--------------------------|------------------------------|------------------------------|------------------------------|

| Capacity (mid 2012)      | 3 TB                         | 2TB                          | 900 GB                       |

| Cost (mid 2012)          | $\sim 150 \text{EUR}$        | $\sim 300 \text{EUR}$        | $\sim$ 700EUR                |

| Power Consumption (rel)  | 1x                           | 1.2x                         | 1.5x                         |

| Reliability (MTTF)       | 600kh                        | 1200kh                       | 1600kh                       |

| Spindle Speed (RPM)      | 5.4k-7.2k                    | 7.2k-10k                     | 10-15k                       |

| Duty cycle               | $<\!10\%$                    | $<\!\!20\%$                  | 100%                         |

| Power-on hours           | 2400h/a                      | 8760h/a                      | 8760h/a                      |

| Performance (rel)        | 1x                           | 1x                           | 1.4x - 2.5x                  |

| T10 data integrity       | no                           | no                           | yes                          |

| Unrecoverable error rate | $10^{-14} \text{ bits}^{-1}$ | $10^{-15} \text{ bits}^{-1}$ | $10^{-16} \text{ bits}^{-1}$ |

Table 2.2.: Comparison of desktop, nearline, and enterprise disks [38, 40, 41].

backup and reference data sets, cloud and scale-out storage. Enterprise disks aim at applications which require highest operational availability and workloads. Their platters are usually smaller in diameter to reduce rotational vibration, head arms and voice coils are designed for 100% duty cycles, and controller electronics and software are generally more sophisticated (containing for instance dual CPUs and better error resilience). They provide the highest performance together with the highest reliability and the lowest uncorrectable error rate. In addition to the error-correcting codes in the disk itself, enterprise disks provide end-to-end data integrity mechanisms from the user perspective: Supplementary 8 byte of information are added to every sector to store user or operating system generated checksums and reference information [39]. With these boundary conditions, enterprise drives are generally more expensive while providing less storage capacity. An overview of different properties of desktop, nearline, and enterprise disks is shown in Table 2.2.

The *super-paramagnetic effect* sets a lower limit for the volume of the magnetic grains that can be used in magnetic storage devices [42]. At this limit the magnetization can be spontaneously flipped due to thermal fluctuation which leads to information loss. To compensate one can increase the magnetic anisotropy of the medium, which at the same time requires an increased magnetic field for which larger heads are needed. Because of this trade-off, for a long time the predicted maximum areal density was several hundreds of gigabits per square inch. However, the transition from longitudinal to perpendicular magnetic recording already allowed for much higher densities of up to 1 terabit per square inch. The road maps for upcoming magnetic recording technologies include several approaches that promise several order of magnitudes higher areal storage densities beyond the super-paramagnetic limit: *Bitpatterned magnetic recording (BPMR)* uses magnetic nano-islands with well defined positions to store information, which are assembled with nano-lithographic processes. *Heat-assisted magnetic recording (HAMR)* employs an additional laser in the read/write head to locally raise the temperature above the Curie temperature and to then change the magnetization with a relatively small magnetic field. Re-

#### 2. Storage Technologies

lated is the *microwave assisted magnetic recording (MAMR)*, where the write head contains a nano microwave oscillator instead of the more complex optical system. With *shingled magnetic recording (SMR)* neighboring tracks overlap heavily (more than two thirds of the track are covered by the adjacent track). This technique has no disadvantages in case of reading, but for writing it requires an extended read-modify-write cycle, since direct write access to an inner overlapped track would damage the neighbor tracks. SMR can be combined with *two dimensional magnetic recording (TDMR)* where a 2D-image is built up from multiple adjacent tracks and sophisticated image detection and decoding techniques are employed to reconstruct the original data. As a result the problem of destructive interference of shingled tracks can be resolved. All these proposed technologies indicate that magnetic disc storage will remain a core component of secondary storage systems in the next decades, even though alternative non-volatile memory technologies are reaching maturity [31].

## 2.3. Solid state storage

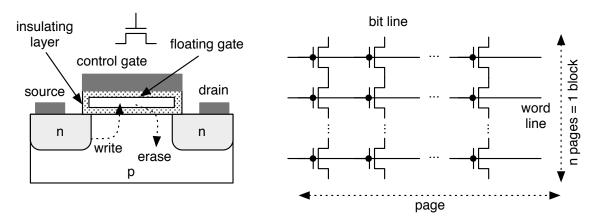

The success of solid state storage has been driven by the demand for low-power, light, and robust nonvolatile storage for mobile applications. Starting with memory cards for digital cameras, USB thumb drives, digital audio players, and mobile phones, flash-based storage is today increasingly used for high performance secondary storage in the form of solid state drives (SSDs). The basic building block of a flash cell is a floating gate MOS transistor which can be arranged in a NOR-type or NAND-type configuration to obtain the two fundamental flash architectures [43, 44, 45]. NOR flash delivers a high read performance, but suffers from low write performance. It can be randomly accessed (similar to DRAM) and application code can be executed from it. Available capacities are rather low and it is therefore often used to store the boot code or firmware for computers or embedded systems. NAND flash, on the other hand, enables much higher cell densities and allow fast erase and write operations, but it cannot be directly addressed and requires complex controller hardware. It offers larger capacities and lower cost and is, therefore, better suited for bulk data storage applications. Since almost all solid state block storage devices are based on NAND-type flash, the architecture and properties of these memories are reviewed in the following paragraphs.

Figure 2.7 on the facing page shows a NAND flash floating gate transistor and the architecture of a NAND flash memory. A single level cell (SLC) transistor stores one bit of data, whereas a multi level cell (MLC) is able to store multiple bits. The value of the bits is determined by the amount of charge stored in the floating gate. Since the floating gate is surrounded by insulating material, the charge is transported by a quantum mechanical tunnel mechanism: It is injected into the floating gate during writing and persistently stored there (in this case the bit value is 0). During erase operations the charge is released from he floating gate, reverting the bit value to 1. To form a memory device, the floating gate transistors are assembled into an array: Several of them are connected in series via a bit line, whereas their control gates are connected to individual word lines. All transistors sharing the same word line form a *page*, and all pages make up a *block* (Figure 2.7 on the next page, right). In order to read, all but one word line are pulled up above the threshold voltage of the transistors,

Figure 2.7.: NAND Flash transistor cell (left) and NAND flash memory architecture (right) [43].

the bit line is then conductive or non-conductive depending on state of the singled out transistor. For writing, a high positive voltage is applied to the control gate, which allows tunneling of electrons in to the floating gate. Therefore, a page is the smallest amount of data that must be read or written at a time. Since erasure requires the eviction of electrons from the floating gate by applying a high voltage to the substrate, it can only be done for the entire block (bulk erasing). In effect, an individual page in a NAND flash block cannot be directly overwritten, but the write request has to be redirected to another block by a transparent management layer. If it is clear that all pages in certain block are not used anymore, the whole block can be erased and used for future write requests. The number of write or erase cycles, however, is finite due to two wear-out effects: Electrons can be trapped in the insulating layer around the floating gate or the insulting layer can break down all together. As a result electrons cannot tunnel anymore between the floating gate and the substrate. The page can then not be used anymore and has to be added to a list of bad pages (write endurance for flash devices is in the order of  $10^5 - 10^6$  cycles). To avoid the breakdown of pages that are frequently written, write counters and address mapping mechanisms are used to distribute the writes evenly over different blocks (wearleveling). All these characteristics of NAND flash require an intermediate software or firmware layer which organizes the logical to physical mapping, the garbage collection, the wear leveling, the bad block handling, and the error-correction. Since file systems usually only remove the directory entry of a file upon deletion, the TRIM command has been implemented to let the management layer know that the page is not used anymore. This decreases the reorganization of pages that do not contain valid data anymore and alleviates the performance degradation of background garbage collection. Typical values for a current enterprise level NAND flash storage device are shown in Table 2.3 on the following page. While offering significantly higher random access bandwidth and I/O operations per second than hard disks, capacities and cost differ by at least one order of magnitude. Remarkably, the values for the mean time to failure and the unrecoverable error rate are at par with those of an enterprise disk drive (although the SSD does not contain an equally complex mechanical system). In addition to the problem of limited write endurance due to degradation of the insulation layer, flash storage reliability is affected by several effects [48, 49]: Especially NAND flash is prone to bit flipping in neighboring

| Typical value                |

|------------------------------|

| SAS 6 Gb/s                   |

| MLC                          |

| 400 - 800 GB                 |

| 4-8 kB                       |

| $\geq$ 256 pages             |

| 180k IOPS                    |

| 75k IOPS                     |

| 2000 MB/s                    |

| 1000 MB/s                    |

| $10^{-16} \text{ bits}^{-1}$ |

| 2.000.000 h                  |

| 7-14 PB                      |

| $\sim 5~{ m US/GB}$          |

|                              |

Table 2.3.: Characteristics of a top-of-line NAND flash SSD in mid 2012 [46, 47].

cells during read and write operations. Furthermore, the charge in the floating gate can slowly leak and lead to a wrong interpretation of the bit value. The ability to retain data is also influenced by the number of experienced erase or write cycles. Flash devices can contain up to 5 % of initial bad blocks due to production yield constraints, as well as the bad blocks accumulated during operation. Failure to detect and manage both types can lead to data loss. To increase reliability it is essential to use strong error-correcting codes (BCH, Reed-Solomon) on a page level, similar to the sector protection scheme of hard disks.

Solid state storage is often seen complementary to hard disk storage as the top layer in tiered storage scenarios. While hard disks fulfill the requirements for high capacity and low cost, SSD provide higher bandwidths and drastically higher rates of I/O operations per second. However, projections show that as storage densities of flash devices increase, properties such as performance, endurance, energy efficiency and data retention time could be adversely affected [50].

## 2.4. Disk micro-benchmark

Listing 2.1: Definition of the sg\_io\_hdr\_t data structure in the linux kernel

```

unsigned char mx_sb_len; /* [i] max length to write to sbp */

6

unsigned short iovec_count; /* [i] 0 implies no scatter gather */

7

unsigned int dxfer_len; /* [i] byte count of data transfer */

8

9

void __user *dxferp;

/* [i], [*io] points to data transfer memory

or scatter gather list */

10

unsigned char __user *cmdp; /* [i], [*i] points to command to perform */

11

void __user *sbp; /* [i], [*o] points to sense_buffer memory */

unsigned int timeout;

12

/* [i] MAX_UINT->no timeout (unit: millisec) */

13

unsigned int flags;

/* [i] 0 -> default, see SG_FLAG... */

14

15

int pack_id;

/* [i->o] unused internally (normally) */

16

17

unsigned char masked_status;/* [0] shifted, masked scsi status */

18

unsigned char msg_status; /* [o] messaging level data (optional) */

19

unsigned char sb_len_wr; /* [0] byte count actually written to sbp */

20

unsigned short host_status; /* [o] errors from host adapter */

21

unsigned short driver_status; /* [o] errors from software driver */

22

int resid;

/* [0] dxfer_len - actual_transferred */

23

24

25

sg_io_hdr_t; /* 64 bytes long (on i386) */

26

```

To illustrate the characteristics of direct disk operations a small micro-benchmark was developed for this thesis. The benchmark utilizes the SCSI Generic (sg) driver found in the linux kernel [51]. The drivers allows user applications to directly send SCSI commands to the device. Therefore, an object of type  $sg_io_hdr_t$  (defined in Listing 2.1) is prepared and handed to an  $ioctl()^1$ . The  $sg_io_hdr_t$  data structure itself contains a low level description of a SCSI request using various input and return parameters needed to perform the operation. The ioctl() is blocking until the prepared SCSI command is finished. This behavior can be used to probe the internal structure of a disk by measuring the repeated execution time for different SCSI commands. With this low-level access many layers of the operation system can be bypassed and the disturbing effect of caching and queueing systems can be avoided. All benchmarks were performed with an off-the-shelf IBM enterprise-class SCSI disk<sup>2</sup>. For this disk an excellent and comprehensive specification and documentation is available [52], such that the measured properties can be verified. All relevant characteristics are summarized in Table 2.4. To reduce noise during the measurement the disk was installed as secondary (non-OS) disk and used as a pure block device (that is, a file system was not installed on the disk). For all measurements the disk cache was disabled.

#### 2.4.1. Data zones

The disk characteristic to validate the easiest is the *Zone Bit Recording (ZBR)*. Since the track length (or circumference) increases with the distance from the center of the disk, it is possible to fit more

<sup>&</sup>lt;sup>1</sup>ioctl() is short for input/output control and is special system call for non-generic input/output operations specific to a certain device.

<sup>&</sup>lt;sup>2</sup>Model IC35L018UWD210-0

| Value             |

|-------------------|

| 18.35 GB          |

| 3                 |

| 2                 |

| 18,351,959,040    |

| 35,843,670        |

| 10,000 RPM        |

| 4096 KiB          |

| 17                |

| 750 sectors/track |

| 390 sectors/track |

| 4.9 ms            |

| 10.5 ms           |

| 0.88 ms           |

| 0.72 ms           |

|                   |

Table 2.4.: Drive characteristics of the IBM IC35L018UWD210-0 disk [52].

Figure 2.8.: Illustration of hard disk zones. The number of sectors is dependent on the length of the tracks. Hence outer tracks hold more sectors. As a trade-off tracks are grouped into zones.

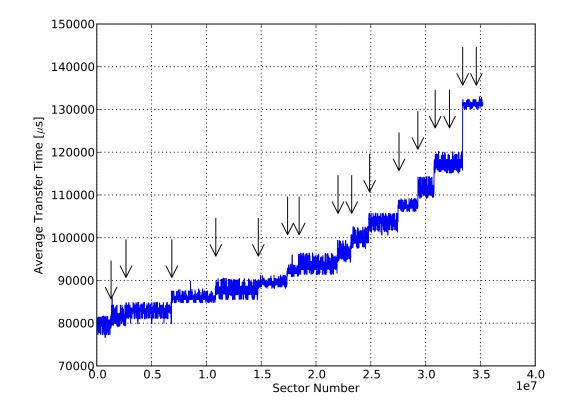

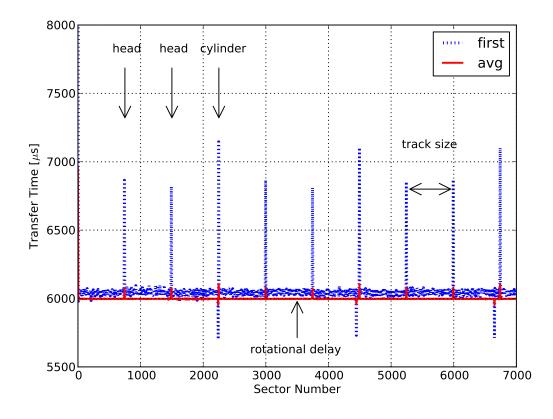

sectors on the outer tracks. Disks are therefore partitioned into a certain number of zones with constant number of sectors per track as illustrated in Figure 2.8. Since during a full revolution the amount of data read in the outermost zone is larger than in the inner zones, the zoning schema can be directly seen by observing the data transfer rate of a small number of consecutive sectors in the respective zone. Figure 2.9 shows the measured data transfer time depending on the sector number and hence depending on the position of the disk. The arrows indicate the zone borders according to the specification of the used disk.

Figure 2.9.: Hard disk zones become visible when measuring the transfer times for a fixed-sized chunk with different staring positions on the disk. The arrows indicate the zone borders according to the specification of the used disk.

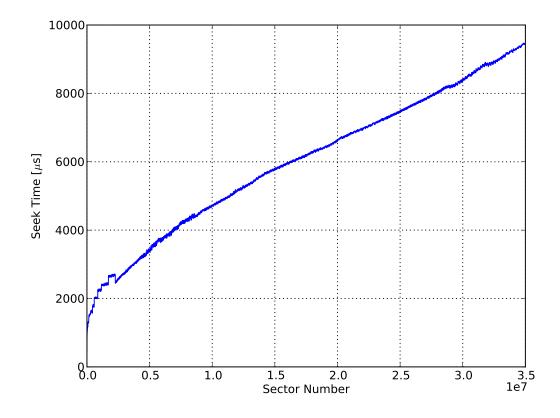

### 2.4.2. Seek time

The seek time is measured from the start of the actuator movement to the start of a reliable read or write operation. The average seek time  $\overline{T}$  is specified in the data sheet [52] as weighed average of all possible seek combinations<sup>3</sup>:

$$\overline{T} = \frac{1}{s_{\max}(s_{\max}+1)} \quad \sum_{n=1}^{s_{\max}} (s_{\max}+1-n)(T_n^{in}+T_n^{out}),$$

(2.1)

where  $s_{\text{max}}$  is the maximum seek length,  $T_n^{in}$  is the inward measured seek time to track *n*, and  $T_n^{out}$  is the outward measured seek time to track *n*. Figure 2.10 shows the seek times for all destination sectors.

<sup>&</sup>lt;sup>3</sup>The definition of the average seek time varies considerably between hard drive manufacturers. Often the average seek time is calculated as the sum of all possible seek times divided by the number of seeks. It can be shown that this corresponds to one-third of the full stroke seek time.

Figure 2.10.: Seek times. The patterns for small sector numbers indicate that the hard disk firmware employs different strategies for shorter movements of the actuator arm.

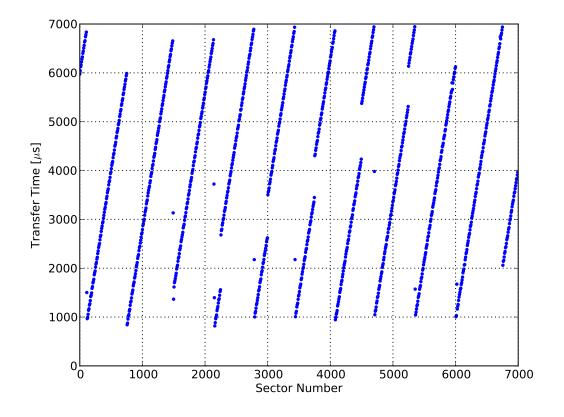

#### 2.4.3. Jump time

In this particular test the time to read a particular sector directly after reading sector 0 is measured (with two consecutive but separate read commands). The head not only has to seek to the correct track, but also has to wait for the correct sector to be in reach. Figure 2.11 shows the result for the first 7000 sectors. The execution time increases at first with increasing sector number, since the requested sector is too close to sector 0. After the time needed to process the second read request, the requested sector has already passed the head. Therefore almost another full rotational delay is required to access the second sector. When the distance between the two sectors becomes comparable to the distance corresponding to the request processing time, the execution time drops drastically and is effectively reduced to the seek time. This pattern repeats periodically as the second read request moves through the upward tracks. The occasional gaps in the slope correspond to the times required to switch heads inside a cylinder (head skew) and the times to switch to the next cylinder (cylinder skew).

Figure 2.11.: Jump time: Read a particular sector directly after reading sector 0 (with two consecutive but separate read commands).

### 2.4.4. Window read

The window read benchmark exposes the most information about the structure of the hard disk. The time to repeatedly read a small chunk of consecutive sectors is measured. If the chunk lies in the middle of a track, the measured time reflects the time needed to perform a full rotation (the chunk size is negligible compared to the number of sectors on an outer track). However, if the chunk crosses a disk border, that is, the next sector still lies on the same cylinder but on another platter, the head skew time becomes visible. Furthermore, if the chunk crosses a cylinder border one can observe the cylinder skew. These two penalties show up as distinct peaks in Figure 2.12 and can be used to estimate the size of tracks and cylinders. The mean time needed for one full rotation is measured as  $5999 \pm 31\mu$ s, therefore the number of rotations per minute can be estimated as

~~~

$$RPM = \frac{60s}{5.999 \cdot 10^{-3}s} = 10.001 \pm 52,$$

(2.2)

Figure 2.12.: Window read times for chunks of 10 consecutive sectors. The dotted curve indicates the first read operation, whereas the solid curve shows the average. Head and cylinder skew, as well as the rotational delay and the track size in zone 0, can be directly estimated.

which is in remarkable accordance with the data sheet. The peaks in execution time indicate head (platter) switches at sector 750 and 1500, and cylinder switches at sector 2250.

Figure 2.12 shows the average execution time as well as the time needed for the very first access. The times for the first access are significantly higher, especially when a platter or cylinder switch is necessary. This indicates an intrinsic caching mechanism which cannot be switched off with the disk cache.

## 2.5. Reliability modeling and failure modes

This section provides a short survey of reliability and availability theory, particularly with respect to storage devices. A comprehensive overview can be found in [53] and [54], on which several parts of this introduction are based.

### 2.5.1. Introduction

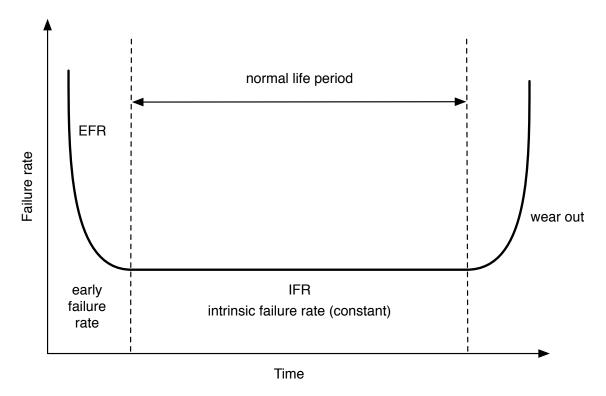

The failure rate of hardware components is often associated with the so-called *bathtub curve*, illustrated in Figure 2.13. In this plot the failure rate is shown over the operational time. During the first period of operation poorly manufactured or weak components contribute greatly to the high failure rate until most problematic components have been sorted out and the failure rate stabilizes. This first phase is often called *infant mortality period*. The period with a constant intrinsic failure rate is considered the *normal life period* of the component. At the end of the normal life period the components enter the *wear out period*, associated with a greatly increasing failure rate. Manufacturers often try to reduce the early failure rate visible to the customer by applying burn-in tests, where the component is exposed to increased stress for a short period of time.

Figure 2.13.: Bathtub curve

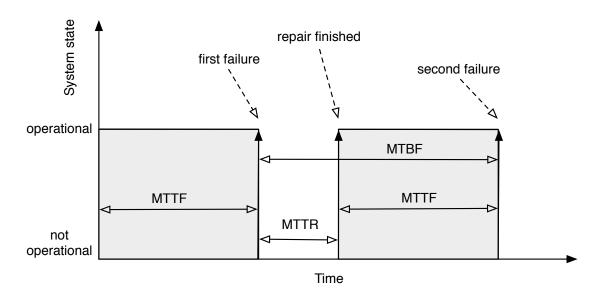

In the context of failure rates different mean times are often used: The *Mean Time To Failure (MTTF)* is the arithmetic mean of the times from start of the component to the failure. The *Mean Time To Repair (MTTR)* is the average time until the component repair is completed. Finally, the *Mean Time Between Failure (MTBF)* is the average time between two failures, or simply the sum of MTTF and MTTR. An illustration of MTTF, MTBF, MTTR is shown in Figure 2.14 on the following page. The availability A of a repairable system is defined as the probability that the system is operational. With the definitions

Figure 2.14.: Mean time to failure (MTTF), mean time between failure (MTBF), and mean time to repair (MTTR).

from above the availability can be written as

$$A = \frac{MTTF}{MTTF + MTTR} = \frac{MTTF}{MTBF}.$$

(2.3)

Highly available systems are often grouped into availability classes, depending on the number of nines in the decimal places of the availability: For example A = 0.99999, referred to as *five nines*, corresponds to a combined down time of 5.26 minutes per year of operation.

#### 2.5.2. Reliability theory

The reliability R(t) is the probability that a system is operating correctly until the time t. Let T be a random variable denoting the time of a failure. The reliability is then the probability that T is greater than t

$$R(t) = P(T > t), \quad t \ge 0.$$

(2.4)

Conversely, the failure probability F(t) is

$$F(t) = P(T \le t), \quad t \ge 0.$$

(2.5)

F(t) is often called the *cumulative failure distribution function (CFDF)* and is related to the reliability function by

$$R(t) = 1 - F(t).$$

(2.6)

The derivative of F(t) is called the *failure density function*,

$$f(t) = \frac{\mathrm{d}F(t)}{\mathrm{d}t} = -\frac{\mathrm{d}R(t)}{\mathrm{d}t}.$$

(2.7)

Integration of Equation 2.7 leads to

$$F(t) = \int_0^t f(\tau) \mathrm{d}\tau$$

(2.8)

and

$$R(t) = 1 - \int_0^t f(\tau) \mathrm{d}\tau = \int_t^\infty f(\tau) \mathrm{d}\tau.$$

(2.9)

The relationship can be interpreted as follows: The failure density function gives the probability for a failure at a given point in time. Integration over the complete time must give 1. Therefore, the failure probability by time t is the sum of all failure probabilities from time 0 to t. On the other hand, the survival probability by time t is the remaining part of the integral from time t to infinity.

The expected value of a real valued random variable X with a probability density function f(x) is defined as

$$E(X) = \int_{-\infty}^{\infty} x f(x) \mathrm{d}x.$$

(2.10)

Therefore the Mean time to failure (MTTF) is defined as<sup>4</sup>

$$MTTF = \int_0^\infty t f(t) dt, \qquad (2.11)$$

and it can be shown (details can be found in [53]) that with the above definitions the MTTF can be expressed as

$$MTTF = \int_0^\infty R(t) \mathrm{d}t. \tag{2.12}$$

The hazard function (or instantaneous failure rate function) can then be defined as

$$h(t) = \frac{f(t)}{R(t)}.$$

(2.13)

In many cases an exponential failure distribution is chosen where the failure density function is given by

$$f(t) = \begin{cases} \lambda e^{-\lambda t} & t > 0\\ 0 & t \le 0, \end{cases}$$

(2.14)

where  $\lambda$  is constant. This results in the reliability function

$$R(t) = e^{-\lambda t}, \qquad (2.15)$$

<sup>&</sup>lt;sup>4</sup>Only  $t \ge 0$  is relevant for failure analysis.

and the failure density function

$$F(t) = 1 - e^{-\lambda t}.$$

(2.16)

The hazard function

$$h(t) = \frac{\lambda e^{-\lambda t}}{e^{-\lambda t}} = \lambda$$

(2.17)

is therefore constant and its inverse is the mean time to failure

$$MTTF = \frac{1}{\lambda}.$$

(2.18)

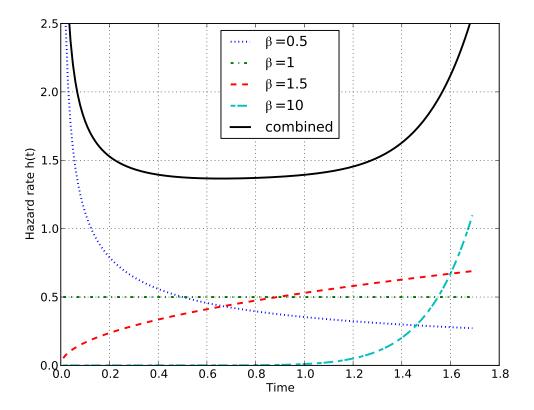

Inherent to the exponential distribution is the property of memorylessness, meaning that the failure rate is independent of the history of failures. However, this is not always an appropriate assumption. The three-parameter *Weibull distribution* provides a generalization of the exponential distribution. The shape of the distribution depends significantly on the specific values of the parameters and it is particularly suitable to model the different phases of the bathtub curve. The failure density function is given by

$$f(t,\boldsymbol{\beta},\boldsymbol{\theta}) = \begin{cases} \frac{\boldsymbol{\beta}(t-\boldsymbol{\gamma})^{\boldsymbol{\beta}-1}}{\boldsymbol{\theta}^{\boldsymbol{\beta}}} e^{-\left(\frac{t-\boldsymbol{\gamma}}{\boldsymbol{\theta}}\right)^{\boldsymbol{\beta}}} & t > \boldsymbol{\gamma} \\ 0 & t \le \boldsymbol{\gamma} \end{cases},$$

(2.19)

where  $\beta$  is called the shape parameter,  $\theta$  is called the scale parameter, and  $\gamma$  is called the location parameter. Since  $\gamma$  is used to specify a guaranteed failure free period from t = 0 to  $t = \gamma$ , in the following  $\gamma = 0$  is assumed.

The reliability function is then

$$R(t) = e^{-\left(\frac{t}{\theta}\right)^{\beta}} \quad \text{for } t > 0, \ \beta > 0, \ \theta > 0,$$

(2.20)

and the corresponding hazard function

$$h(t) = \frac{\beta t^{\beta - 1}}{\theta^{\beta}} \quad \text{for } t > 0, \ \beta > 0, \ \theta > 0.$$

$$(2.21)$$

When  $\beta = 1$  the Weibull distribution is equivalent to the exponential distribution, since then

$$f(t) = \frac{1}{\theta} e^{-\left(\frac{t}{\theta}\right)} \tag{2.22}$$

and

$$h(t) = \frac{1}{\theta}.$$

(2.23)

For  $\beta = 2$  the failure density function is reduced to a function which is also known as Raleigh distribution:

$$f(t) = \frac{2t}{\theta^2} e^{-\left(\frac{t}{\theta}\right)^2},\tag{2.24}$$

24

and

$$h(t) = \frac{2t}{\theta^2}.$$

(2.25)

In general the shape parameter influences the time dependence of the hazard rate and the interpretation is as follows:

- $\beta < 1$ : The hazard rate is decreasing over time. This is used to model the burn-in period.

- $\beta = 1$ : The hazard rate is constant and as for the exponential distribution. This behavior models the normal life period.

- $\beta > 1$ : The hazard rate is increasing over time, which represents the wear-out period.

The hazard rate of the Weibull distribution for different values of  $\beta$  is depicted in Figure 2.15. The combination of the individual hazard rates can be used to model the characteristic shape of the bathtub curve.

Figure 2.15.: Weibull hazard rates and their additive combination to model the bathtub curve.

#### 2.5.3. RAID reliability

In the original RAID publication [6] the MTTF of a collection of disks, assuming exponentially distributed time to failure and constant failure rate, is given by

$$MTTF = \frac{MTTF_{\text{single disk}}}{N},$$

(2.26)

where *N* is the number of disks in the collection. With the 1-error tolerance of the original RAID systems, the *Mean Time To Data Loss (MTTDL)* of a RAID array is

$$MTTDL_{\text{RAID}} = \frac{MTTF_{\text{single disk}}^2}{N \cdot (G-1) \cdot MTTR},$$

(2.27)

where N denotes the total number of disks, and G is the number of disks in a (parity) group. MTTR is the mean time to repair or replace the failed disk and to reconstruct the lost data. Later, this has been extended for 2-error tolerant RAID-6 arrays [55]:

$$MTTDL_{\text{RAID6}} = \frac{MTTF_{\text{single disk}}^3}{N \cdot (G-1) \cdot (G-2) \cdot MTTR^2}.$$

(2.28)

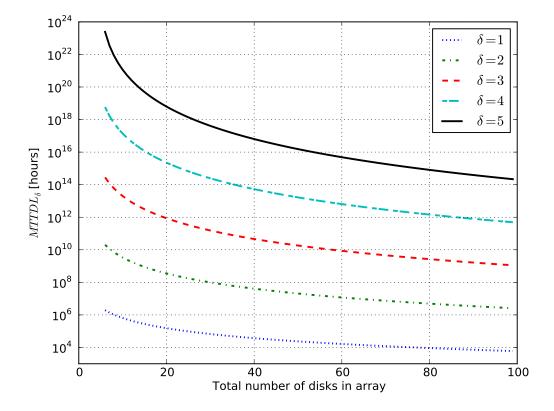

The generalization to a  $\delta$ -error tolerant array is straight-forward

$$MTTDL_{\delta} = \frac{MTTF_{\text{single disk}}^{\delta+1}}{N \cdot \prod_{i=1}^{\delta} (G-i) \cdot MTTR^{\delta}}.$$

(2.29)

Equation 2.29 can be rewritten to make the benefit of additional error-tolerance in this model more apparent:

$$MTTDL_{\delta} = \frac{MTTF_{\text{single disk}}}{N \cdot \prod_{i=1}^{\delta} (G-i)} \cdot \left(\frac{MTTF_{\text{single disk}}}{MTTR}\right)^{\delta}.$$

(2.30)

The *MTTDL* for the system is multiplied by the ratio of  $MTTF_{\text{single disk}}$  and MTTR for every additional error the system can withstand. Clearly  $MTTR \ll MTTF_{\text{single disk}}$  holds, since realistically the *MTTR* is in the order of several ten hours (assuming a 2 TiB disk with a moderate reconstruction rate of 50 MiB/s), whereas the order of the  $MTTF_{\text{single disk}}$  of a modern disks ranges from 10<sup>5</sup> to 10<sup>6</sup> hours. Therefore, the repeated division by the size of the parity group is small against the additional power of the ratio.

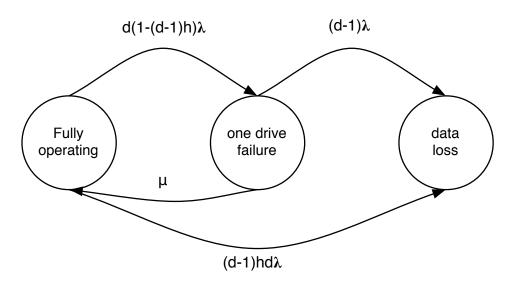

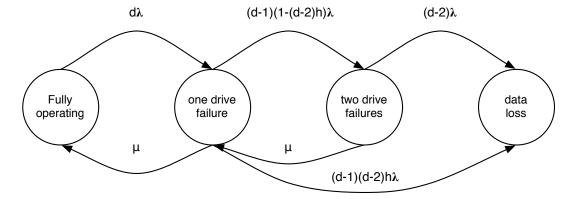

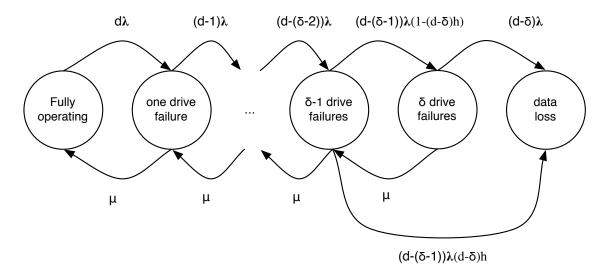

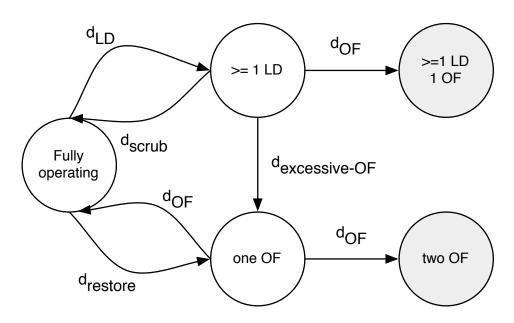

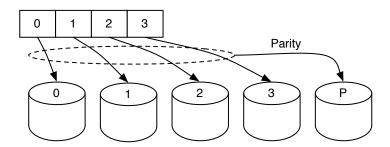

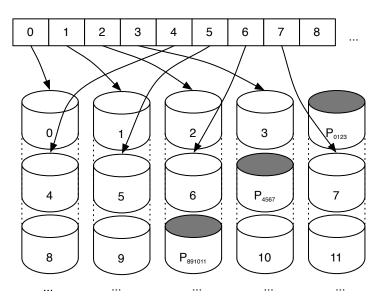

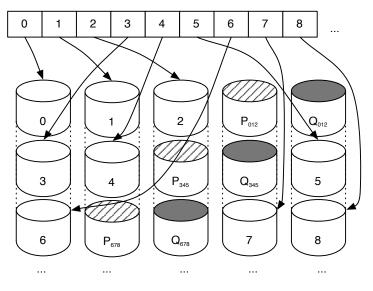

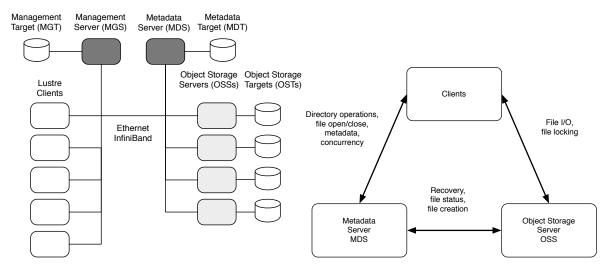

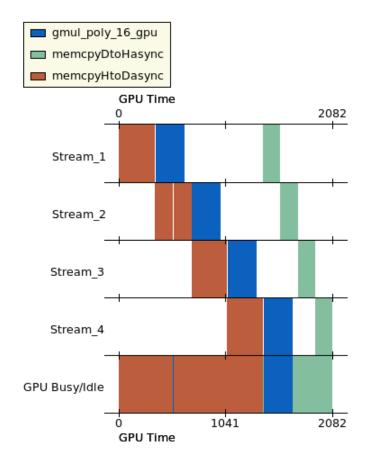

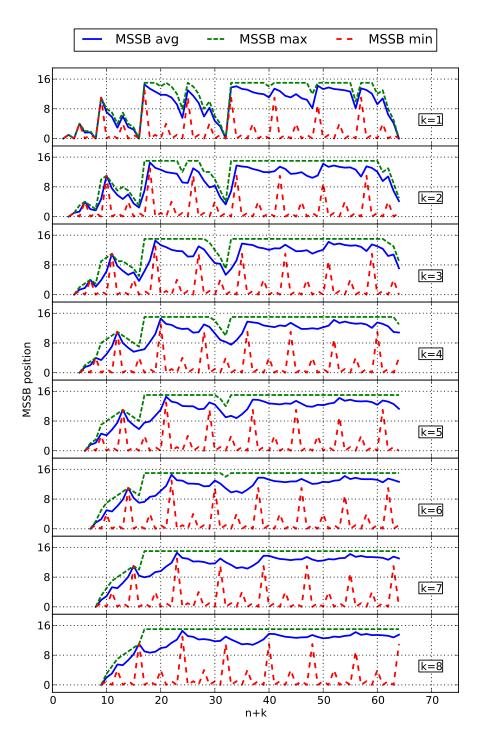

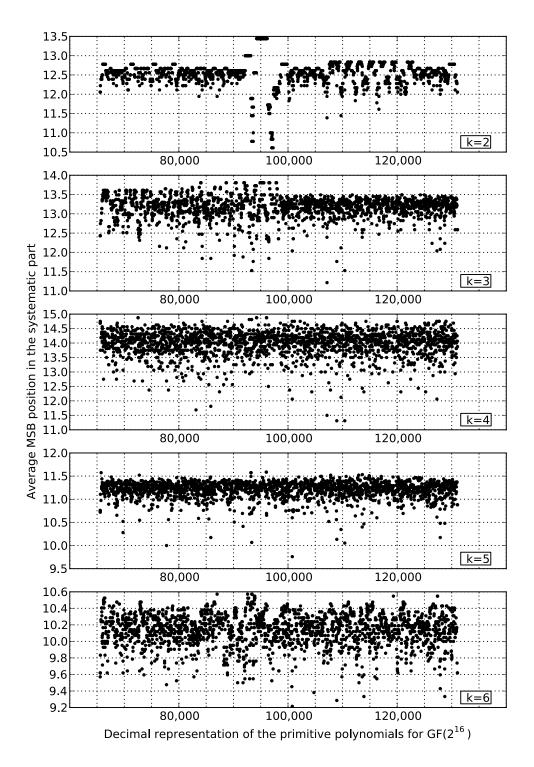

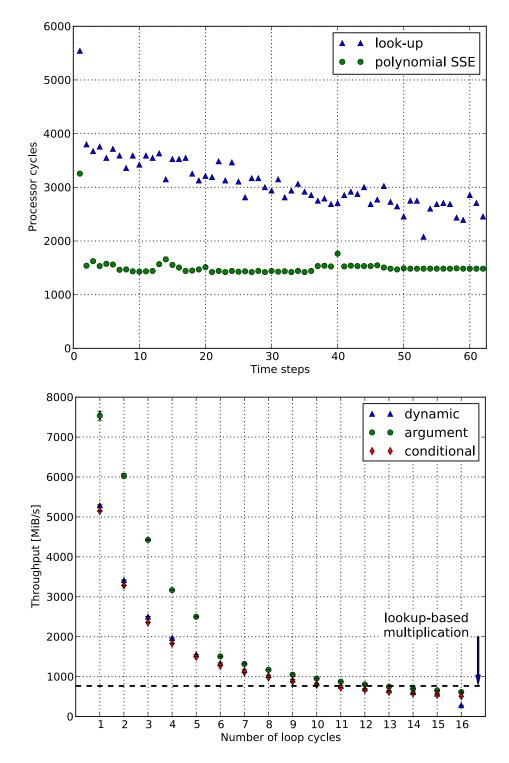

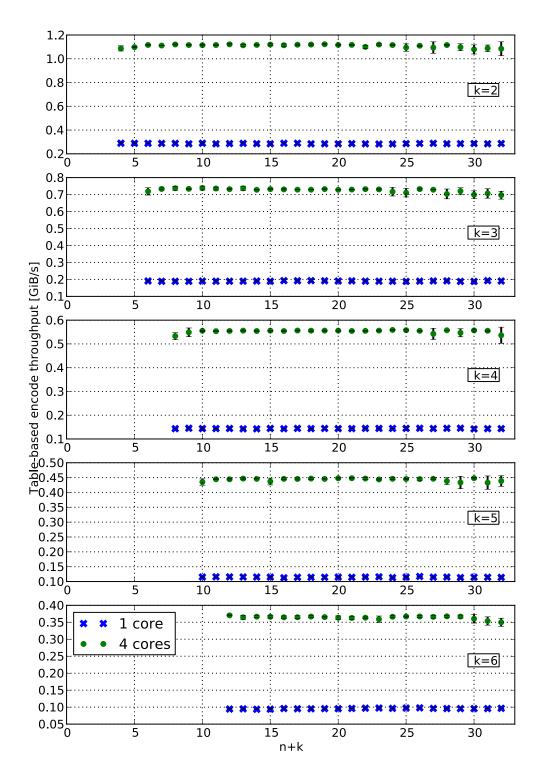

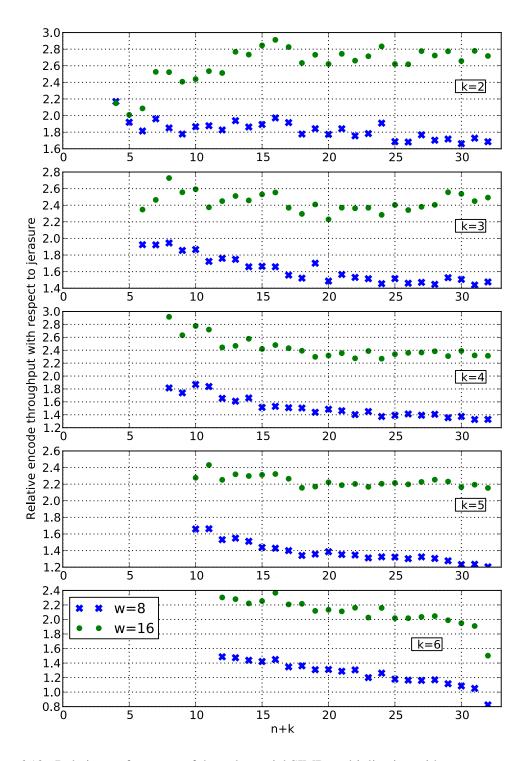

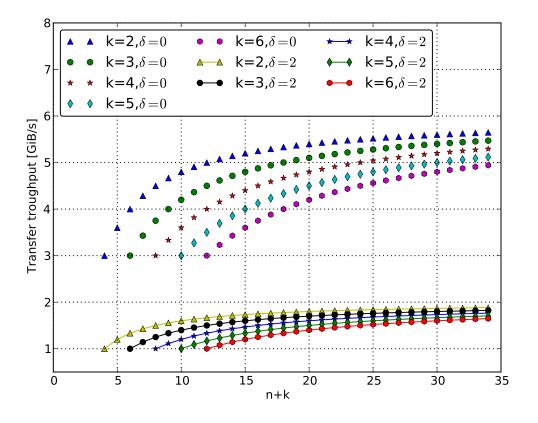

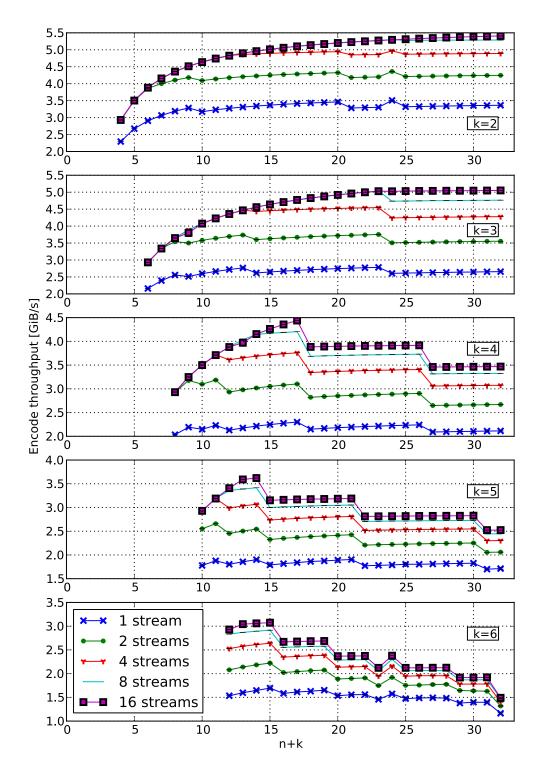

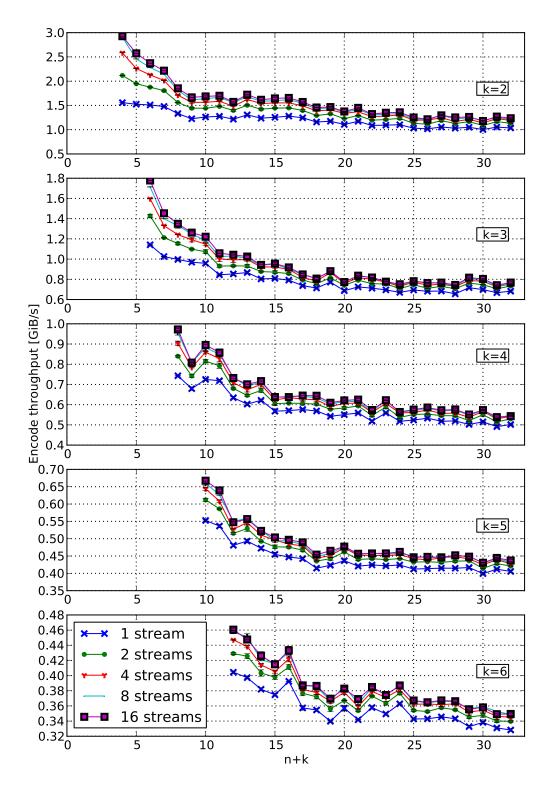

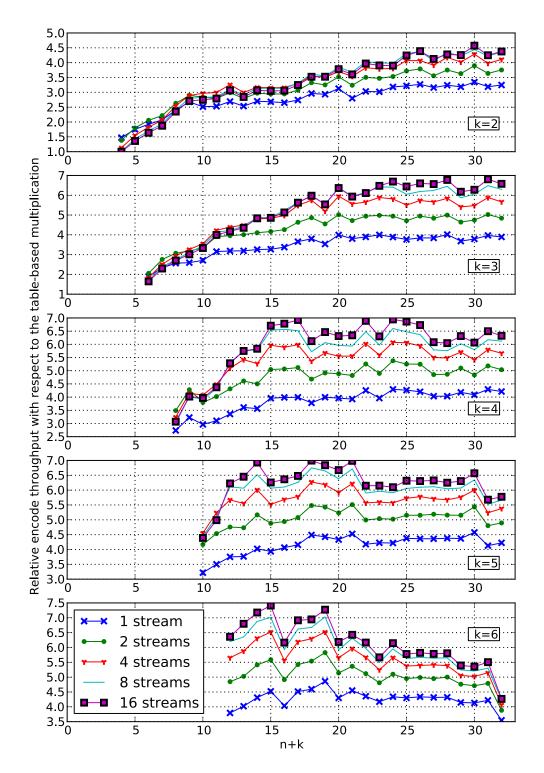

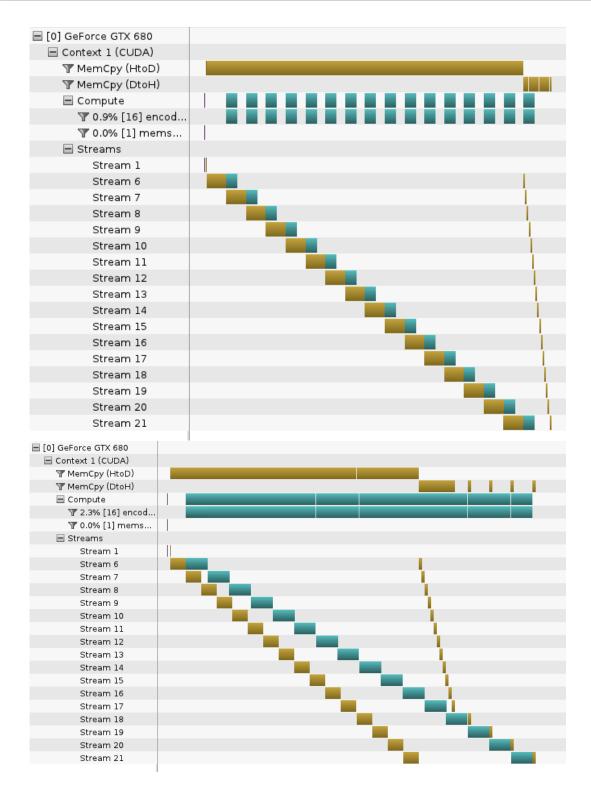

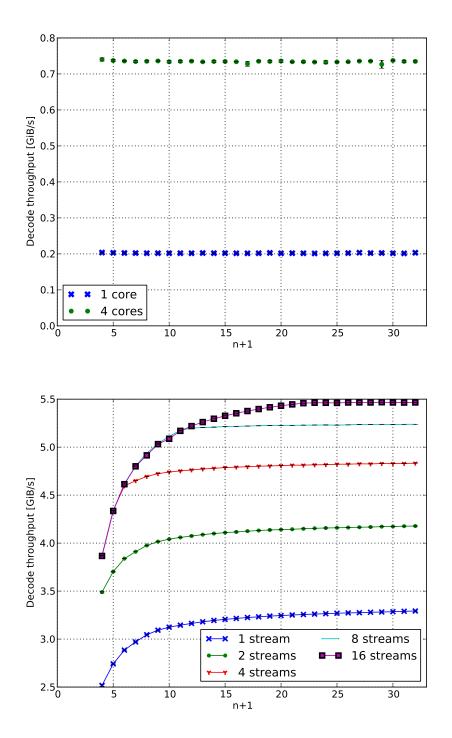

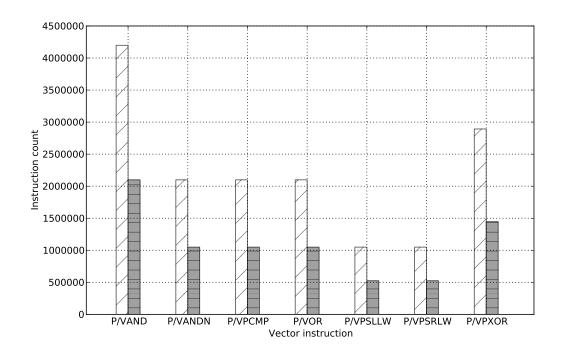

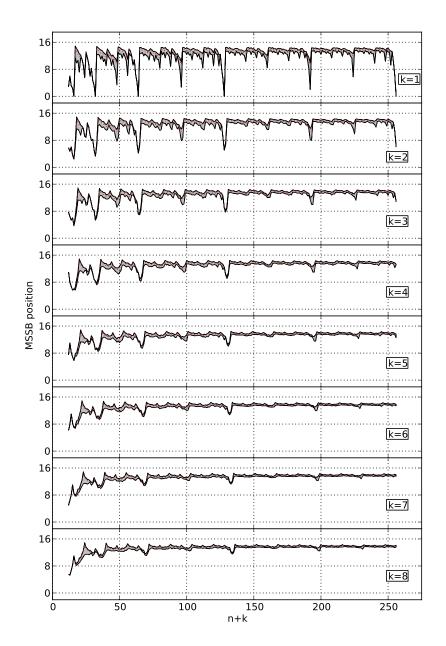

#### 2.5.4. Markov models