## A Highly Dependable, Analog Multi-Core Mixed-Signal Task Distribution System

Dissertation zur Erlangung des Doktorgrades der Naturwissenschaften

vorgelegt beim Fachbereich Informatik und Mathematik der Goethe-Universität in Frankfurt am Main

von

Julius von Rosen

aus Frankfurt

Frankfurt (2014) (D 30) vom Fachbereich Informatik und Mathematik der Goethe-Universität als Dissertation angenommen

Dekan:

Prof. Dr. Uwe Brinkschulte

Gutachter:

Prof. Dr. Lars Hedrich Prof. Dr. Uwe Brinkschulte

Datum der Disputation: 9. Juni 2015

Acknowledgments

### Abstract

The objective of this thesis is to develop an analog architecture, which distributes decentralized, highly dependable and self-reliant tasks within a mixed-signal multi-core System-on-Chip. Hence, every step of the design process and their results to develop such an analog system are presented, since the synthesis of analog circuits is still mostly done manually, contrary to the almost fully autom-atized and formalized design of digital circuits. Especially the validation and long-term satisfaction of the specification of the analog components need a high degree of verification and testing done by hand.

The usability of the design is evaluated against known task distribution approaches, which are either highly sophisticated digital circuits or software implementations, which have shown their usability in real-world applications already. Further, evaluations are done against analog approaches, which are capable of being transformed to match the objectives of this thesis. This allows to clearly differentiate the developed and designed architecture from the existing approaches.

The design of an artificial, analog hormone system is a bio-inspired replica to distribute information and tasks within a system. The endogenous transmitters are mapped to voltages and currents, which are, properly coordinated, spreading throughout the full system. Those hormones can be applied locally, but are noticed globally at every core. However, the physical laws of electrical engineering have to be taken into consideration as equally as the balance of the hormones to guarantee the reliable and dependable functionality of the task distribution.

Within the design process a complete formal description of the analog components of the hormone system is done. Based on the description, solving the differential equations and inequalities, which mirror the behavior of the hormone system, enables to issue a reliability analysis. With this analysis the fail-safety of the components are classified, the dependencies of the circuit parameters are determined and a set of specification, needed for the design process, are derived. Further, a robustness value has been defined, which quantifies the interval of legitimacy within which any process variation, noise and similar effect is fully absorbed - the correct functionality of the hormone system is unharmed.

Next to the specification of the components, the prototypical implementation of the system is done, followed by the placing, routing and layouting of the components. Lastly, the layout has been fabricated. The results of the simulations of the implementations, the extracted view and the measurements of the prototypical chip are presented and compared to evaluate the analog hormone system against the presented approaches. The detailed comparison classifies each presented approach and the hormone system based on the following key points, which are essential for autonomous task distribution architectures:

- self-control,

- size increase,

- real-time capability,

- reliability gain,

- scalability,

- mixed-signal capability.

Additionally, monitor circuits are designed, which also increase the reliability of the hormone system and the analog cores. The monitor circuits enable a self-reliant management of the cores by themselves. In turn, the self-reliance guarantees the self-control of each core, distributing self-optimized and decentralized tasks within the system. The focus is on monitoring general performance changes, instead of single failure effects like *electromigration* or *Hot Carrier Injection*. If the changing performances remain within the reliability interval, the hormone system has no need to react to, respectively counteract, the change of the system behavior. If the change exceeds the reliability interval though, the monitors are issuing task reallocations.

Concluding, the thesis presents the complete design process of a reliable architecture, which distributes tasks within a mixed-signal multi-core System-on-Chip highly dependable, decentralized and self-reliant. The design process ends with the fabrication of a prototypical chip. Yet, to truly state the self-control property, further monitor circuits for autonomous operating robots are indispensable. Also, extensive studies concerning the real-time capability of the hormone system within different fields of application can only be carried out, if the prototypical implementation of the analog hormone system is attached to designed analog cores, fabricated and measured.

## Zusammenfassung (German Abstract)

Gegenstand dieser Dissertation ist die Entwicklung einer analogen Architektur, die dezentral, hoch-verlässlich und selbstständig Aufgaben innerhalb eines Mixed-Signal Mehrkern-System-on-Chips verteilt. Dazu werden im Rahmen dieser Arbeit auch alle entscheidenden Zwischenschritte und deren Ergebnisse, die während des Entwurfsprozesses für das Design der analogen Schaltungen entscheidend sind, vorgestellt.

Im Gegensatz zum Entwurfsprozess digitaler Schaltungen, die weitestgehend automatisiert und formalisiert sind, bedarf es bei der Synthese von analogen Schaltungen fast ausschließlich manueller Schritte. Insbesondere im Bereich der Validierung und dauerhaften Sicherstellung der spezifizierten Eigenschaften der analogen Schaltungen, ist eine manuelle Verifikation erforderlich.

Gemessen wird die Nutzbarkeit des Entwurfs anhand der in der Praxis bisher gängigen Verfahren zur zuverlässigen Aufgabenverteilung. Diese beziehen sich jedoch ausschließlich auf Software-Implementierungen, verteilt auf Prozessorkernen, oder hochentwickelte, digitale Schaltungen. Des Weiteren werden aus dem analogen Anwendungsbereich zwei Verfahren herangezogen, die auch auf die Thematik dieser Dissertation übertragen werden können. Für jedes dieser vorgestellten Verfahren wird eine Charakterisierung vorgenommen, um die Verfahren gegeneinander zu bewerten. Dadurch lässt sich die entwickelte Architektur klar von den bestehenden Verfahren abgrenzen, da ein solches analoges System zur Verteilung von Aufgaben bisher nicht existiert. Die herangezogenen Verfahren, die als Aufgabenverteilungs-Architektur realisiert werden können, sind

- ein Agenten-basiertes System,

- ein künstliches neuronales Netzwerk,

- ein analoges Voting Verfahren, sowie

- ein digitales, künstliches Hormon System.

Für den umfassenden Vergleich wird das Agenten-basierte Verfahren als Orientierung genutzt, anhand dessen geprüft wird, wie die anderen Verfahren bestehen. Damit lässt sich eine Rangliste der Verfahren anfertigen.

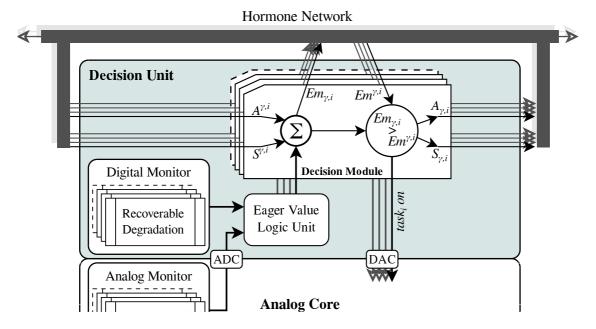

Der Entwurf eines künstlichen, analogen Hormonsystems (AAHS) ist die Abbildung eines Systems aus der Natur zur Verteilung von Informationen und Aufgaben. Hormone werden abstrahiert als Ströme und Spannungen dargestellt. Diese müssen jedoch entsprechend koordiniert über Leitungen verteilt werden. Die Auswertung und Steuerung der Hormone geschieht lokal in den Entscheidungseinheiten, die jeweils an einem Kern angeschlossen werden. Damit stellen die Entscheidungseinheiten dezentrale und redundante Bauteile dar. Allerdings müssen die Hormone auch global allen anderen Kernen zugänglich gemacht werden, damit diese ihre Entscheidungen auf gleiche beziehungsweise ähnliche Hormonwerte stützen. Ansonsten werden unter Umständen fehlerhafte Allokationen durchgeführt. Dies kann im besten Fall eine nicht optimale Aufgabenverteilung zur Folge haben, jedoch im schlechtesten Fall zu Doppel-Allokationen oder ähnlichem führen. Daher ist die Einhaltung bestimmter zeitlicher Schranken von großer Bedeutung. Auch müssen die physikalischen Gesetze der Elektrotechnik weiterhin berücksichtigt werden, damit das Gleichgewicht der Hormone gewahrt wird, um die Funktionalität der zuverlässigen Aufgabenverteilung zu gewährleisten.

Im Rahmen des Entwurfsprozesses erfolgt eine vollständige formale Beschreibung der analogen Komponenten des Hormonsystems. Auf Basis dieser formalen Beschreibung wird ein Differentialgleichungssystem aufgestellt. Dieses muss um Ungleichungen erweitert werden, um das gesamte Schaltungsverhalten abzubilden. Dazu muss das kontinuierliche System zu unterschiedlichen Zeitpunkten diskretisiert werden. Die Lösung dieses diskreten Systems ermöglicht nicht nur eine Zuverlässigkeitsanalyse, sondern auch die Bestimmung der verschiedenen Abhängigkeiten der Hormone und die Spezifikation der Komponenten, die für den Entwurf benötigt werden.

Die Zuverlässigkeitsanalyse klassifiziert jedes einzelne Bauteil anhand seiner Ausfallsicherheit. Durch die Analyse kann eine Aussage getroffen werden, wie wahrscheinlich ein Fehler in den verschiedenen Fehlerklassen auftritt, um dadurch unter anderem auch Rückschlüsse auf die Zuverlässigkeit der Aufgabenverteilung und des Gesamtsystems ermöglichen. Die Abhängigkeit der verschiedenen Bauteile, respektive der Hormonwerte ist ebenso wichtig für den Entwurfsprozess, wie die Spezifikation der einzelnen Komponenten, die sich anhand der Zuverlässigkeitsanalyse definieren lassen. Für die Spezifikation werden verschiedene Kriterien herangezogen, unter anderem die genutzte Technologie, damit verbunden die Größe der Bauteile und die Versorgungsspannung, und die Verwendung des Bauteils innerhalb der Hormonarchitektur.

Auch wird ein Robustheitsfaktor definiert. Dieser bestimmt ein Zulässigkeitsintervall, innerhalb dessen jegliche Prozessschwankungen, aber auch Rauschen und ähnliche Störverhalten, abgefangen werden, ohne die korrekte Funktionalität des Hormonsystems zu beeinflussen. Somit werden für das analoge, künstliche Hormonsystem drei zuverlässigkeitsrelevante Bewertungen definiert:

- 1. die Ausfallsicherheit  $P(X = \Psi) : \Psi \in$  Fehlerklasse  $\{A, B, C\}$ ,

- 2. die Kern-Ausfall-Toleranz  $F_t$  und

- 3. der Robustheitsfaktor  $r_{CC}$ .

Die Kern-Ausfall-Toleranz betrachtet das Gesamtsystem und wie sich der Verlust von Kernen im ungünstigsten Fall auf das Gesamtsystem auswirkt. Je höher der Wert, desto länger kann das System ausfallende Kerne kompensieren. Im Normalfall liegt der Wert  $F_t$  zwischen (0..1), jedoch existiert ein Sonderfall für den  $F_t = 0$  definiert werden muss. Dieser Sonderfall inkludiert all die Fehlerszenarien, in denen ein einziger auftauchender Fehler zum Verlust des Gesamtsystems führt. Mit den drei definierten zuverlässigkeitsrelevanten Bewertungen kann die Zuverlässigkeit genau bestimmt und damit auch die Verbesserung der Zuverlässigkeit beziffert werden.

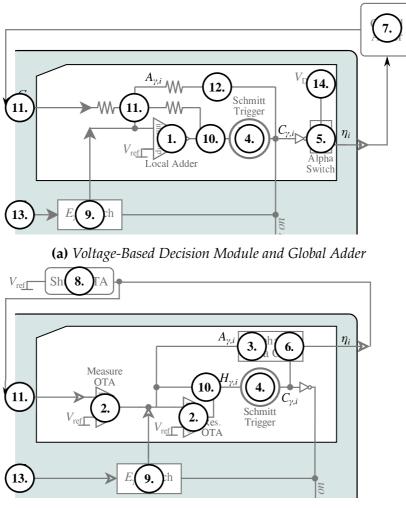

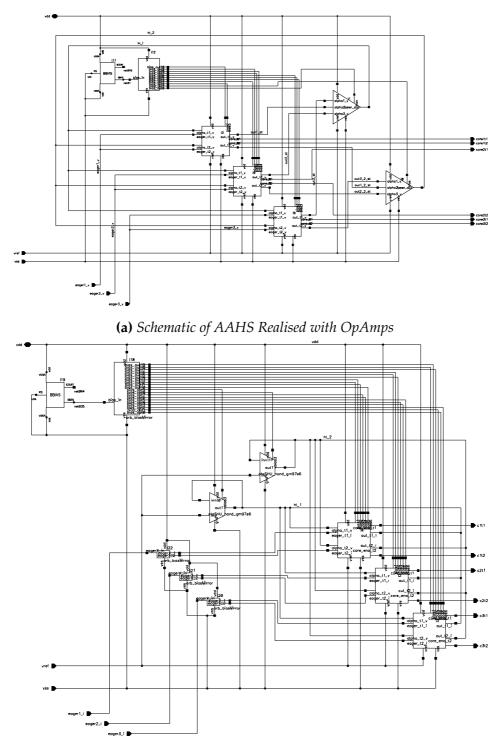

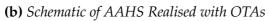

Dem Entwurfsprozess folgt nach der Spezifikation der Komponenten die prototypische Implementierung der Schaltungen. Für diese wurde auf ein semi-automatisietes Synthese-Framework zurückgegriffen, die den sehr zeitaufwändigen Prozess des Entwurfes der Operationsverstärker signifikant verkürzt. Mit dem Synthese-Framework konnten die sechs Operationsverstärker für die zwei Hormonarchitekturen implementiert werden:

- der lokale Addierer, ein lokaler Schmitt-Trigger und der globaler Addierer,

- zwei lokale und ein globaler Transkonduktanzverstärker.

Jeder dieser Operationsverstärker erfüllt die teilweise sehr anspruchsvollen Spezifikationen, wie beispielsweise den geringen Overshoot bei den Operationsverstärkern oder die geringe  $R_{\text{Last}}$  bei einem der Transkonduktanzverstärkern. Zusätzlich sind zwei weitere Schmitt-Trigger entworfen worden, um den unterschiedlichen Anforderungen der Entscheidungseinheiten gerecht zu werden. Die Schmitt-Trigger basieren auf Sechs-Transistor Modellen. Nach der Implementierung folgt das Layouten inklusive der Platzierung und Verdrahtung der einzelnen Komponenten. Die Simulationsergebnisse der Implementierungen lassen sich anschließend mit den Simulationsergebnissen der extrahierten Sicht vergleichen und analysieren. Veränderungen des Schaltungsverhaltens auf Grund der Fertigung werden erstmals sichtbar, zeigen jedoch, dass das analoge, künstliche Hormonsystem die erwartete Zuverlässigkeit erfüllt und nachweislich funktioniert. Anschließend wurde das Layout lithografiert und gefertigt, so dass neben den ersten Simulationsergebnissen, auch das analoge Hormonsystem auf einem gefertigten Chip ausgemessen werden kann. Die Ergebnisse dieser drei Auswertungen werden präsentiert und verglichen, um das künstliche, dezentrale, analoge Hormonsystem entsprechend gegen die anderen Verfahren zu bewerten. Ein umfassender Vergleich ermöglicht eine eindeutige Klassifizierung der unterschiedlichen Ansätze. Dabei liegt der Fokus auf folgenden Punkten, die im Rahmen der Anwendungsbereiche von autonomen Aufgabenverteilungsarchitekturen von Bedeutung sind:

- Selbst-Kontrolle,

- Flächenzuwachs,

- Echtzeitfähigkeit,

- Zuverlässigkeitssteigerung,

- Skalierbarkeit,

- Mixed-Signal Fähigkeit.

Auch werden die Vor- und Nachteile der Strom- und Spannungsbasierten Architekturen aufgezeigt, so dass eine Präferenz abgegeben werden kann, welche die zu bevorzugende AAHS Implementierung ist und welchen Kompromiss diese dafür verlangt.

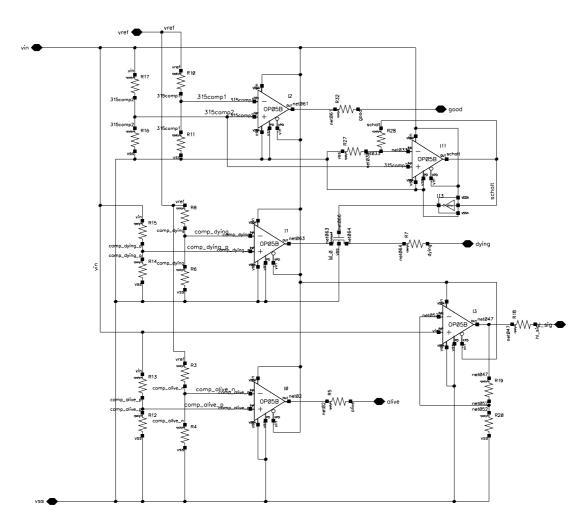

Neben der Hormonarchitektur sind auch Monitor-Schaltungen entworfen worden, die die Zuverlässigkeit des Hormonsystems, sowie der analogen Kerne, erhöhen. Die Monitore ermöglichen die Selbstständigkeit der Kerne und erfüllen damit eine weitere Bedingung der Selbstkontrolle, um als autonome Systeme agieren zu können. Des weiteren gilt, dass eine verlässliche Selbstkontrolle die selbst-optimierende und dezentrale Aufgabenverteilung im Gesamtsystem gewährleistet. Dabei liegt der Fokus nicht auf einzelnen Fehlereffekten wie *Elektromigration* oder *Hot Carrier Injection*, sondern auf der allgemeinen Veränderung der Schaltungen, wie dies zum Beispiel mit dem Spannungsdrift-Monitor geprüft wird. Bewegt sich die Veränderung innerhalb des Zulässigkeitsintervalls, bedarf es praktisch keinem Eingreifen. Veränderungen aber, die das Intervall verletzen, führen Reaktionen bei der Aufgabenverteilung nach sich. Der Spannungsdrift-Monitor misst die Differenz an den Eingangstransistoren und lässt diese gegen die Schwellspannung eines Schmitt Triggers laufen. Wird die Schwellspannung überschritten, dann zeigt der Trigger *Verstärker defekt* an. Sinkt nun die Eingangsspannung wieder, so dass die negative Schwellspannung des Triggers unterschritten wird, dann liegt am Ausgang des Schmitt Triggers wieder die Versorgungsspannung an, der Monitor klassifiziert den Kern wieder als *gesund und aktiv*.

Auch wenn in dieser Arbeit ein produzierter Chip vorgestellt wird, der nachweisbar die richtige und verlässliche Funktionsweise zeigt, an Hand dessen Aufgaben zuverlässig auf einem Mixed-Signal Mehrkern-System-on-Chip verteilt werden, braucht es zum einen weitere Monitor-Schaltungen um der Eigenschaft der Selbst-Kontrolle, die für autonom agierende Roboter unabdingbar ist, vollständig gerecht zu werden und zum anderen ein Re-Design, um alle Single-Point-of-Failure (auch Leitungsverluste) zu eliminieren. In der Arbeit wurden einige Lösungsvorschläge zum Minimieren der Single-Point-of-Failure unterbreitet. Interessant wäre es, diese vollständig zu implementieren und zu fertigen. Dies würde eine Bewertung ermöglichen, in der eine weitere Minimierung der Ausfallsicherheit gegen die zusätzlich benötigte Fläche durchgeführt wird. Auch ließe sich die zeitliche Veränderung der Systeme zeigen.

Zudem müssten prototypische Chips mit den Aufgaben-ausführenden Kernen in Verbindung mit dem Hormonsystem entworfen und produziert werden, um weitere Studien zur echtzeitfähigen Einsetzbarkeit des Hormonsystems in unterschiedlichen Anwendungsbereichen durchführen zu können. Diese prototypischen Gesamtsysteme könnten wiederum auch genutzt werden, um die Veränderungen im Verhalten des Hormonsystems zu zeigen, wenn der Chip Umwelteffekten, wie Strahlungen und/oder Hitze, ausgesetzt ist.

## Contents

| A  | cknov   | vledgments                         | i   |

|----|---------|------------------------------------|-----|

| Al | bstrad  | ct                                 | iii |

| Zι | ısamı   | menfassung (German Abstract)       | v   |

| Li | st of ' | Tables                             | xvi |

| Li | st of I | Figures                            | xix |

| Li | st of   | Symbols and Abbreviations          | xxi |

| 1  | Intr    | oduction                           | 1   |

|    | 1.1     | Analog Circuit Design Flow         | 2   |

|    | 1.2     | Circuit Reliability                | 4   |

|    | 1.3     | Reliability-Aware Architectures    | 15  |

|    |         | 1.3.1 Artificial Neural Networks   | 17  |

|    |         | 1.3.2 Analog Voting                | 22  |

|    |         | 1.3.3 Artificial Hormone System    | 26  |

|    | 1.4     | Motivating Example                 | 29  |

|    | 1.5     | Publications                       | 30  |

|    | 1.6     | Overview                           | 31  |

| 2  | Con     | nparison of Reliable Architectures | 33  |

|    | 2.1     | Size Overhead                      | 36  |

|    | 2.2     | Reliability Gain                   | 42  |

|    | 2.3     | Real-Time Bounds                   | 45  |

|    | 2.4     | Summary of the Comparison          | 48  |

|    | 2.5     | Contributions                      | 51  |

| 3 | Reli | able, M | Iixed-Signal Architecture           |      |      |    |     |   |   |   |   |   |   | 53  |

|---|------|---------|-------------------------------------|------|------|----|-----|---|---|---|---|---|---|-----|

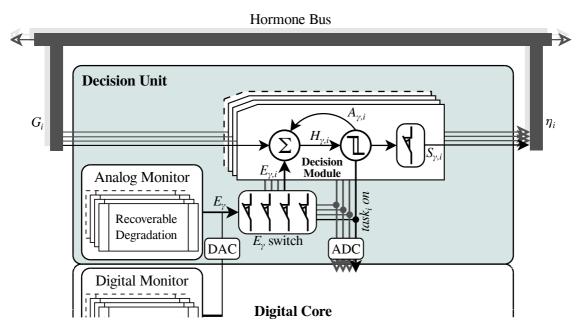

|   | 3.1  | Artific | ial Hormone System with Analog Corr | npor | lent | ts |     | • | • | • | • |   |   | 54  |

|   | 3.2  | Analo   | g Artificial Hormone System         |      |      |    |     | • | • |   | • | • | • | 55  |

|   |      | 3.2.1   | Defining the Analog Hormone System  | n    |      |    |     | • | • | • | • | • | • | 59  |

|   |      | 3.2.2   | Designing the Analog Hormone Syste  | em   |      |    |     | • | • | • | • | • | • | 64  |

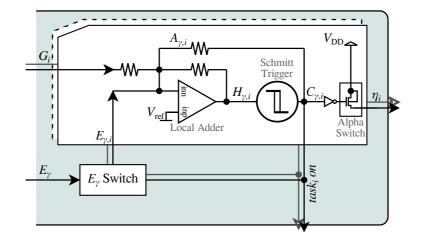

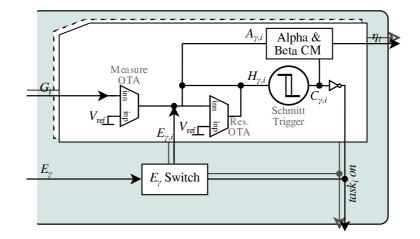

|   |      |         | 3.2.2.1 The Decision Module         |      |      |    |     | • | • | • | • | • | • | 65  |

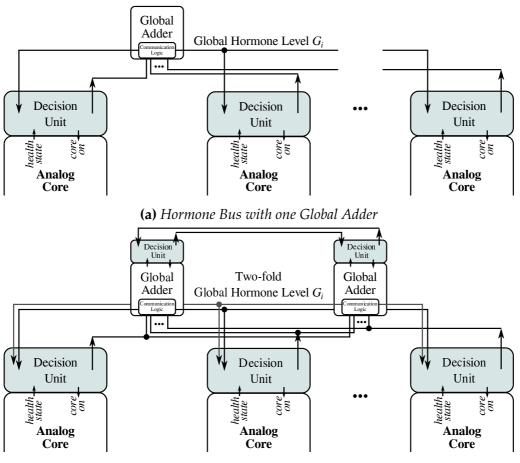

|   |      |         | 3.2.2.2 The Hormone Bus             |      |      | •  |     | • | • | • | • | • | • | 68  |

|   |      |         | 3.2.2.3 Comparing the Architecture  | s    |      | •  |     | • | • | • | • | • | • | 72  |

|   |      |         | 3.2.2.4 Open Design Measures        |      |      |    |     | • | • | • | • | • | • | 72  |

|   |      | 3.2.3   | Task (Re-)Allocation Process        |      |      | •  |     | • | • | • | • | • | • | 73  |

|   |      |         | 3.2.3.1 Allocating Tasks            |      |      |    |     | • | • | • | • | • | • | 74  |

|   |      |         | 3.2.3.2 Migrating within one Doma   | in . |      | •  |     | • | • | • | • | • | • | 76  |

|   |      |         | 3.2.3.3 Migrating between Domains   | 5    |      | •  | • • | • | • | • | • | • | • | 77  |

| 4 | Dep  | endabi  | ility Analysis                      |      |      |    |     |   |   |   |   |   |   | 79  |

|   | 4.1  | Desig   | n Analysis                          |      |      |    |     | • | • |   |   |   |   | 80  |

|   |      | 4.1.1   | Algebraic Description               |      |      |    |     | • | • |   | • | • | • | 82  |

|   |      | 4.1.2   | Symbolic Solution                   |      |      |    |     | • | • | • | • | • | • | 85  |

|   | 4.2  | Reliab  | ility Analysis                      |      |      |    |     | • | • | • | • | • | • | 91  |

|   |      | 4.2.1   | Failure Classification              |      |      |    |     | • | • |   | • | • | • | 92  |

|   |      | 4.2.2   | Fail-Safety Investigation           |      |      |    |     | • | • | • | • | • | • | 94  |

|   |      | 4.2.3   | Failure Sensitivity                 |      |      |    |     | • | • | • | • | • | • | 100 |

|   |      | 4.2.4   | Monitor Decisions                   |      |      | •  | • • | • | • | • | • | • | • | 104 |

| 5 | Des  | ign Me  | thodology                           |      |      |    |     |   |   |   |   |   |   | 105 |

|   | 5.1  | Specif  | ication Generation                  |      |      |    |     | • | • |   |   |   |   | 106 |

|   | 5.2  | Semi-A  | Automated Analog Circuit Design     |      |      |    |     | • | • |   |   |   |   | 109 |

|   | 5.3  | Horm    | one System Design                   |      |      |    |     | • | • |   |   |   |   | 112 |

|   |      | 5.3.1   | Hormone System Synthesis            |      |      |    |     | • | • |   |   | • | • | 113 |

|   |      | 5.3.2   | Hormone System Layout               |      |      |    |     | • | • |   |   | • | • | 118 |

|   |      | 5.3.3   | Full System Task Migration          |      |      |    |     | • | • |   |   |   |   | 122 |

|   | 5.4  | Monit   | oring                               |      |      |    |     | • | • |   |   | • | • | 123 |

|   |      | 5.4.1   | Hormone System Monitoring           |      |      | •  |     | • | • | • |   | • | • | 123 |

|   |      | 5.4.2   | Working Core Monitoring             |      |      | •  |     | • | • |   | • | • | • | 125 |

|   |      | 5.4.3   | Hormone Bus Monitoring              |      |      | •  |     | • | • | • | • | • | • | 128 |

| 6  | Rest  | alts                                                             | 129 |

|----|-------|------------------------------------------------------------------|-----|

|    | 6.1   | Validating the Design                                            | 130 |

|    |       | 6.1.1 Simulation Runs of the Architectures                       | 133 |

|    |       | 6.1.2 Simulation Runs of the Extracted View of the Architectures | 141 |

|    |       | 6.1.3 Hardware Measurements                                      | 147 |

|    | 6.2   | Meet the Challenge                                               | 149 |

|    | 6.3   | Application Usage                                                | 155 |

|    |       |                                                                  |     |

| 7  | Con   |                                                                  | 159 |

|    | 7.1   | Summary                                                          | 159 |

|    | 7.2   | Challenges and Future Work                                       | 161 |

| Α  | Арр   | endix                                                            | 165 |

|    | A.1   | Major Functions of the Algebraic Analysis                        | 165 |

|    |       | Determine the Number of Voters                                   |     |

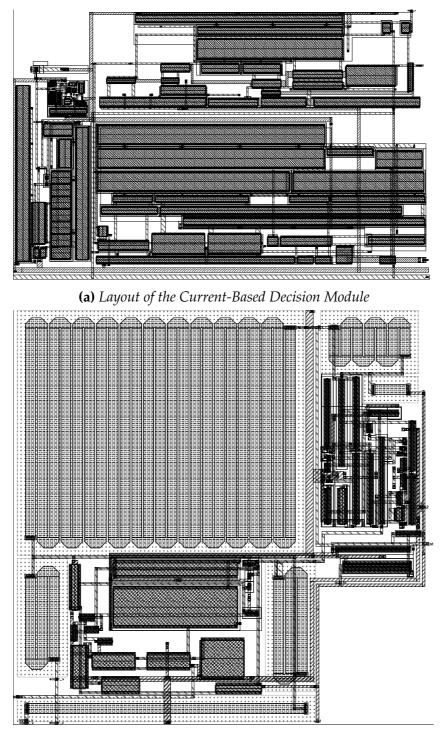

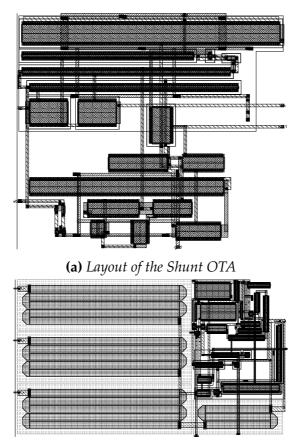

|    | A.3   | Layouts                                                          | 168 |

| Bi | bliog | raphy                                                            | 173 |

## List of Tables

| 1.1 | Voter Costs                                                     | 25  |

|-----|-----------------------------------------------------------------|-----|

| 2.1 | Size Increase of the Different Reliable Architectures           | 36  |

| 2.2 | Comparison of the Failing Core Tolerance                        | 45  |

| 2.3 | Summary of the Comparison Results                               | 50  |

| 3.1 | Size Increase of the Analog Artificial Hormone System           | 61  |

| 3.2 | Preliminary Summary of the Analog Hormone System                | 62  |

| 4.1 | Evaluation of the Symbolic Analysis                             | 86  |

| 4.2 | Evaluation of Combined Sets                                     | 88  |

| 4.3 | Evaluation of the Specific Set                                  | 88  |

| 4.4 | Evaluation Comparison of $\theta_{\gamma,i}$ and $E_{\gamma}$   | 88  |

| 4.5 | Evaluation of the Corner Case Analysis                          | 90  |

| 4.6 | Failure Class Occurrences                                       | 93  |

| 4.7 | Failure Susceptibility                                          | 101 |

| 4.8 | Failure Sensitivity of Sample Working Cores                     | 103 |

| 5.1 | Derived Hormone Values                                          |     |

| 5.2 | Generating the Specification                                    | 110 |

| 5.3 | Set of Derived Specifications                                   | 111 |

| 5.4 | Measurement Table of the Semi-Automated Synthesized             | 115 |

| 6.1 | Classification of the System States                             | 130 |

| 6.2 | Signals of the Voltage-Based Architecture                       | 135 |

| 6.3 | Signals of the Current-Based Architecture                       | 139 |

| 6.4 | Timing Constraints of the Current-Based Architecture            | 139 |

| 6.5 | Signals of the Extracted View of the Voltage-Based Architecture | 141 |

| 6.6 | Timing Constraints of the Simulation of the Extracted View      | 142 |

| 6.7  | Hysteresis of the Schmitt Trigger of the Voltage-Based Architecture | 143 |

|------|---------------------------------------------------------------------|-----|

| 6.8  | Signals of the Extracted View of the Current-Based Architecture     | 145 |

| 6.9  | Timing Constraints of the Simulation of the Extracted View          | 146 |

| 6.10 | Hysteresis of the Schmitt Trigger of the Current-Based Architecture | 147 |

| 6.11 | Comparing the Timing Constraints                                    | 150 |

| 6.12 | Comparing the Failure Class Areas                                   | 151 |

| 6.13 | Measured Eager Value Allocation Bounds                              | 151 |

| 6.14 | Advantages of the Architectures                                     | 152 |

| 6.15 | Completed Summary of AAHS                                           | 153 |

| 6.16 | Real Comparison of AHS and AAHS                                     | 154 |

| A.1  | Determine the Minimum Number of Voters                              | 169 |

# List of Figures

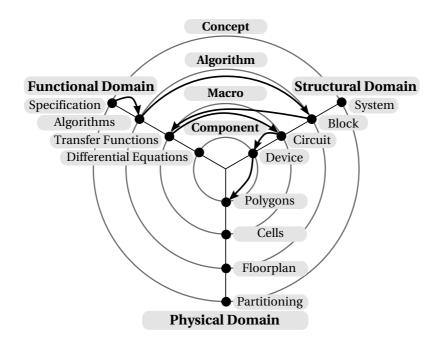

| 1.1  | Y-chart of the Analog Design                                      | 3  |

|------|-------------------------------------------------------------------|----|

| 1.2  | Failure Severity Diagram                                          | 5  |

| 1.3  | Performance Degradation of Different Reliability-Aware Approaches | 10 |

| 1.4  | Sine Input Sigal with Resulting Probability for Defect            | 11 |

| 1.5  | Analog, Adaptive Body Biasing Based NBTI Monitor                  | 12 |

| 1.6  | On-Chip Monitor to Detect HCI and NBTI Degradation                | 13 |

| 1.7  | Centralized Reliability-Aware Architectures                       | 16 |

| 1.8  | Reliable Architecture using ANN                                   | 18 |

| 1.9  | Artificial Neuron                                                 | 19 |

| 1.10 | Implementation of an Artificial Neural Network                    | 21 |

| 1.11 | Artificial Neural Networks as Task Distribution System            | 23 |

|      | Reliable Architecture using AV                                    | 24 |

| 1.13 | Reliable Architecture using AHS                                   | 27 |

| 1.14 | Assignment of Generalized Tasks                                   | 27 |

| 1.15 | Artificial Hormone Loop                                           | 28 |

| 1.16 | Failing of a Motor Control using a PID-Controller                 | 29 |

| 1.17 | Failing of a Signal Filtering                                     | 30 |

| 2.1  | Different Reliability-Aware Architectures                         | 35 |

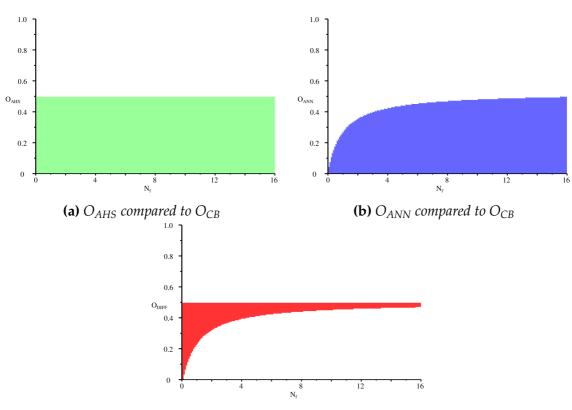

| 2.2  | Allowed Overhead of ANN and AHS                                   | 41 |

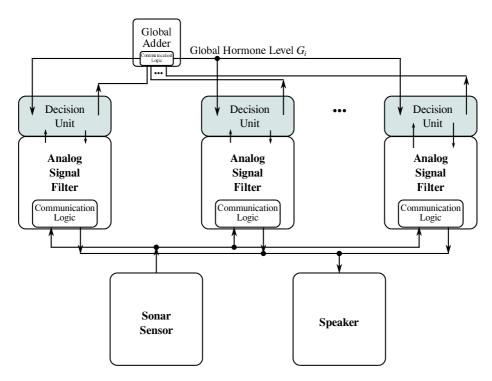

| 3.1  | Digital Hormone Loop for Analog Cores                             | 55 |

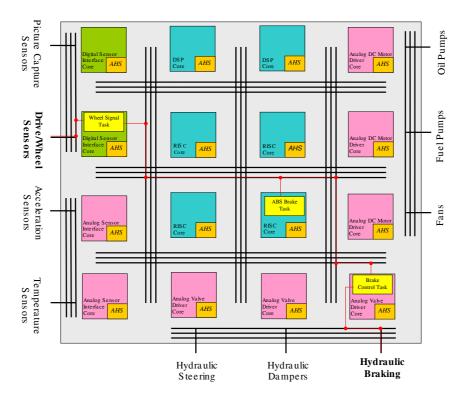

| 3.2  | ABS Braking System using the AHS/AHS-A Architecture               | 56 |

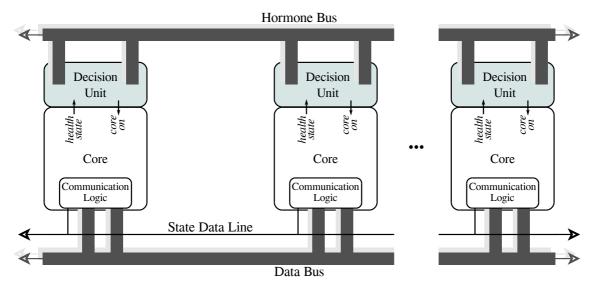

| 3.3  | Model of a Multi-Core System                                      | 57 |

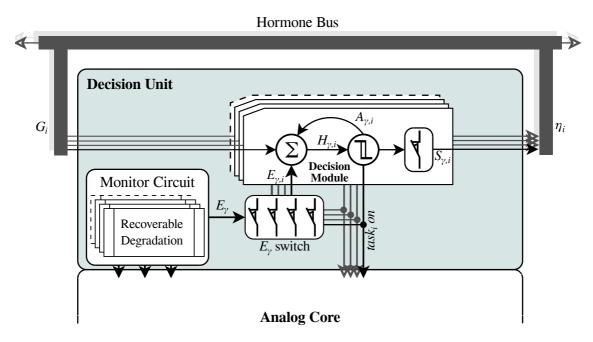

| 3.4  | Analog Artificial Hormone Based Control Loop                      | 59 |

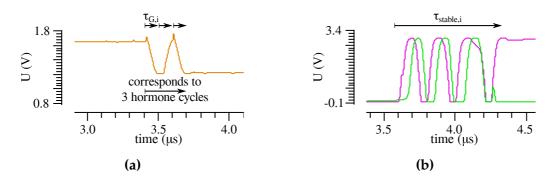

| 3.5  | Sketches outlining $\tau_{G,i}$ and $\tau_{\text{stable},i}$      | 60 |

| 3.6  | Analog Hormone Loop for Digital Cores                             | 63 |

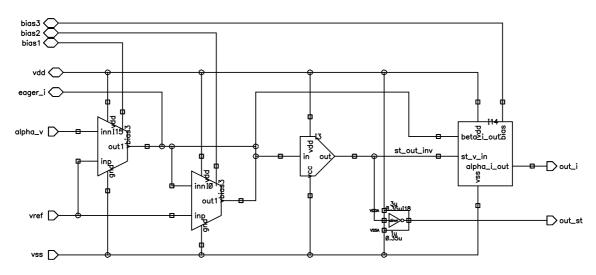

| 3.7  | Implementation of the Decision Module with OpAmps                 | 65 |

|      |                                                                   |    |

| 3.8  | Implementation of the Decision Module with OTAs                              |

|------|------------------------------------------------------------------------------|

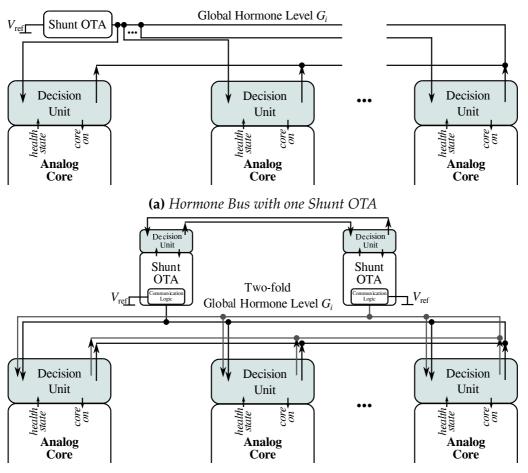

| 3.9  | Voltage-based Hormone Bus Structure                                          |

|      | Current-based Hormone Bus Structure                                          |

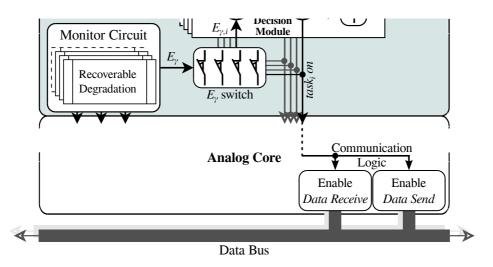

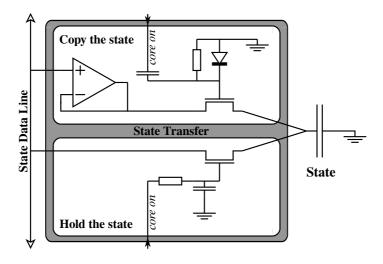

|      | Communication Logic of a Core75Analog State Transfer76                       |

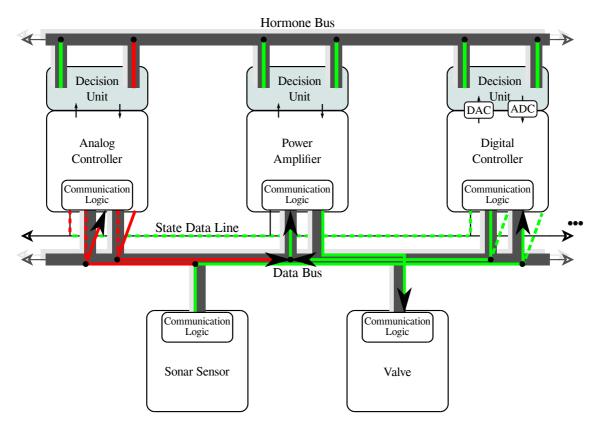

|      | Analog State Transfer76Task Migration between an Analog and a Digital Core77 |

| 5.15 | lask inigration between an Analog and a Digital Core                         |

| 4.1  | Sketch of the Analog Hormone System                                          |

| 4.2  | Block Diagram of a Limiting Adder Circuit 81                                 |

| 4.3  | Four Polyhedrons Representing Different Feasible Regions 89                  |

| 4.4  | Chebyshev Sphere inside the Polyhedron 90                                    |

| 4.5  | Polyhedron representing Feasible Region of the Corner Case 90                |

| 4.6  | Degradation Effects of a Schmitt Trigger                                     |

| 4.7  | Classifying the Fail-Safety of the Decision Modules 94                       |

| 4.8  | Sensitivity Diagram of the Analog Hormone System 102                         |

| 5.1  | Flow of the Design Methodology of the Hormone System 106                     |

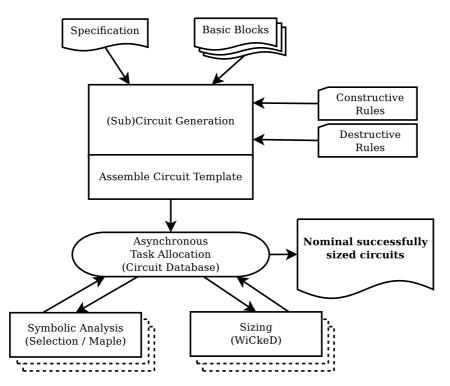

| 5.2  | Fully Automated Analog Synthesis Framework Flow                              |

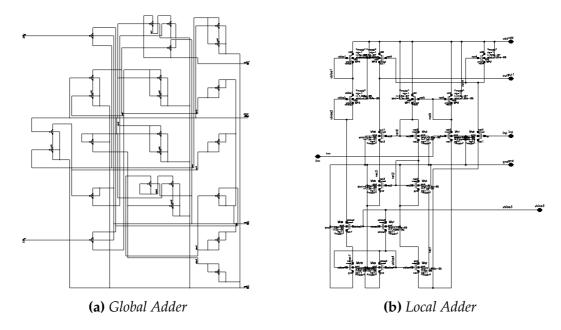

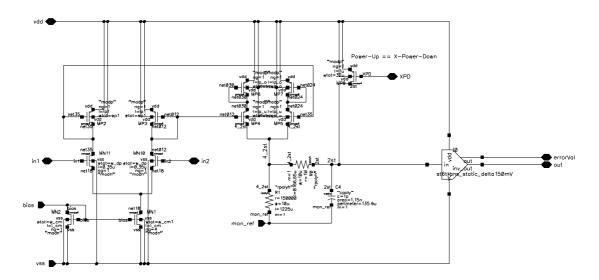

| 5.3  | Schematics of the Voltage Adder                                              |

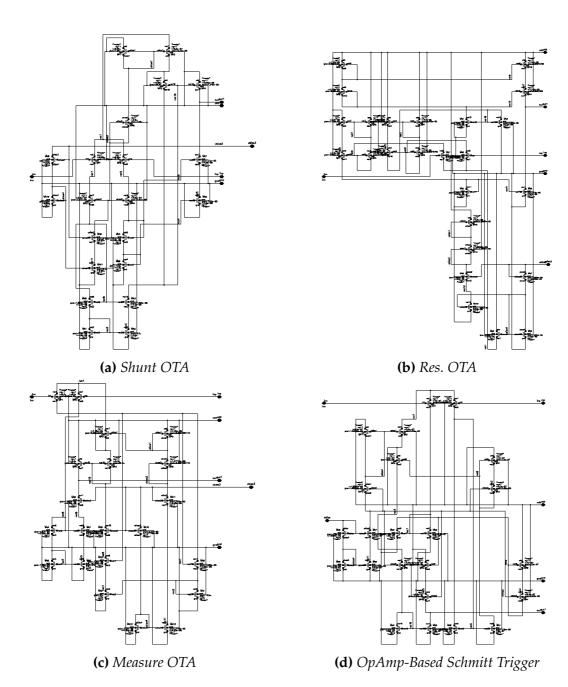

| 5.4  | Schematics of the OTAs and ST                                                |

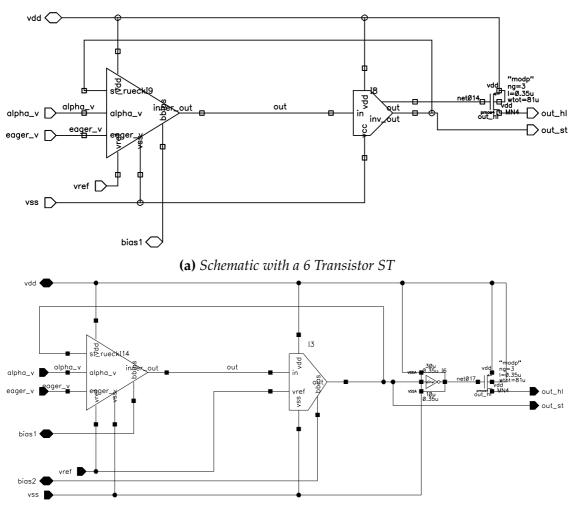

| 5.5  | Schematics of the Decision Modules using OpAmps                              |

| 5.6  | Schematic of the Decision Module using OTAs                                  |

| 5.7  | Schematics of the Architectures                                              |

| 5.8  | The Fully Layouted Architectures                                             |

| 5.9  | Voltage Drift Monitor                                                        |

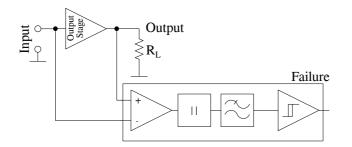

| 5.10 | Block Diagram of a Monitor Circuit for an Output Stage                       |

| 5.11 | Monitoring the Supply Voltage of a Battery                                   |

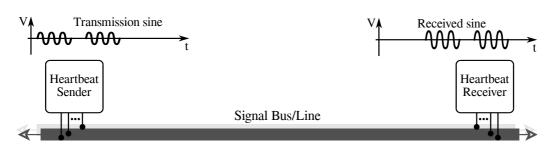

|      | Heartbeat Signal Monitor                                                     |

|      |                                                                              |

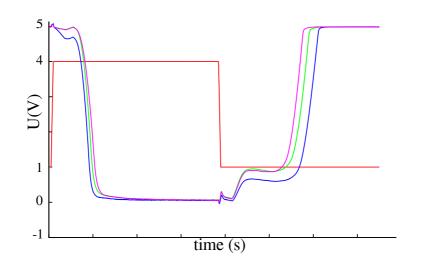

| 6.1  | Simulation Run of the Voltage-Based Architecture                             |

| 6.2  | Allocation Processes of the Voltage-Based Architecture                       |

| 6.3  | Simulation Run of the Current-Based Architecture                             |

| 6.4  | Visualized Timing Behavior of the Current-Based Architecture 140             |

| 6.5  | Extracted View Simulation of the Voltage-Based Architecture 142              |

| 6.6  | Re-Issued Simulation of the Extracted View                                   |

| 6.7  | Simulation Run of the Current-Based Architecture                             |

| 6.8  | Photograph of the Test Chip                                                  |

| 6.9  | Reliability Prove of the Current-Based Architecture                          |

| 6.10 | Motor Control using AAHS                                | 155 |

|------|---------------------------------------------------------|-----|

| 6.11 | Simulation Result of the <i>Right Arm</i> Motor Control | 156 |

| 6.12 | Simulation Result of the Signal Filtering               | 157 |

| 6.13 | Signal Filtering using AAHS                             | 158 |

| A.1  | Layout of the Decision Modules of the Architectures     | 170 |

|      | Layout of the Global Units of the Architectures         |     |

## List of Symbols and Abbreviations

| Notati     | on                                                    |

|------------|-------------------------------------------------------|

| ω          | Word containing a set of letters                      |

| Ω          | Set of words                                          |

| x          | Absolute value of <i>x</i>                            |

| ż          | Temporal derivative of $\mathbf{x}(t)$                |

| 1 <i>x</i> | Sequence of an ordered list of integers from 1 to $x$ |

#### Symbols

| 0 / 110 010                |                                         |

|----------------------------|-----------------------------------------|

| $	au_X$                    | Time constant of component <i>X</i>     |

| Ν                          | Number of cores                         |

| т                          | Number of tasks                         |

| $SR_E$                     | Slew Rate of the eager value            |

| 0                          | Size Overhead                           |

| t, f                       | State of a core having a task allocated |

| α, β                       | Scalar factors                          |

| $	heta_X$                  | Trigger value of component X            |

| $\epsilon$                 | Error function                          |

| $T_i$                      | Task i                                  |

| $C_{\gamma}$               | Core $\gamma$                           |

| $A_{\gamma,i}$             | Local Accelerator Hormone               |

| $E_{\gamma}, E_{\gamma,i}$ | Eager Value Hormone                     |

| $G_i$                      | Global Hormone Level                    |

|                            |                                         |

| $H_{\gamma,i}$  | Local Hormone Level               |

|-----------------|-----------------------------------|

| $S_i$           | Global Suppressor Hormone         |

| $F_t$           | Failing Core Tolerance            |

| r <sub>CC</sub> | Robustness Value                  |

| $\Box_X$        | Area of X                         |

| χ               | Component of AAHS                 |

| $\mathcal{C}_0$ | State Coverage                    |

| $\mathcal{C}_1$ | Allocation Coverage               |

| $\mathcal{O}$   | Asymptotic upper complexity bound |

| Η               | Frequency Response                |

#### Abbreviations

| AC                                    | Alternating Current                                                                                                                                                  |

|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AAHS                                  | Analog Artificial Hormone System                                                                                                                                     |

| AHS                                   | Artificial Hormone System                                                                                                                                            |

| AHS-A                                 | Artificial Hormone System with Analog Cores                                                                                                                          |

| AMAS                                  | Auction-based Multi-Agent System                                                                                                                                     |

| AMS                                   | Analog/Mixed-Signal                                                                                                                                                  |

| ANN                                   | Artificial Neural Networks                                                                                                                                           |

| BTI                                   | Bias Temperature Instability                                                                                                                                         |

| CAD                                   | Computer-Aided Design                                                                                                                                                |

| СМ                                    | Current Mirror                                                                                                                                                       |

|                                       |                                                                                                                                                                      |

| CMOS                                  | Complementary Metal Oxide Semiconductor                                                                                                                              |

|                                       |                                                                                                                                                                      |

| CMOS                                  | Complementary Metal Oxide Semiconductor                                                                                                                              |

| CMOS<br>DAE                           | Complementary Metal Oxide Semiconductor<br>Differential Algebraic Equation                                                                                           |

| CMOS<br>DAE<br>DC                     | Complementary Metal Oxide Semiconductor<br>Differential Algebraic Equation<br>Direct Current                                                                         |

| CMOS<br>DAE<br>DC<br>DF               | Complementary Metal Oxide Semiconductor<br>Differential Algebraic Equation<br>Direct Current<br>Design Failures                                                      |

| CMOS<br>DAE<br>DC<br>DF<br>DRC        | Complementary Metal Oxide Semiconductor<br>Differential Algebraic Equation<br>Direct Current<br>Design Failures<br>Design Rule Check                                 |

| CMOS<br>DAE<br>DC<br>DF<br>DRC<br>EDA | Complementary Metal Oxide Semiconductor<br>Differential Algebraic Equation<br>Direct Current<br>Design Failures<br>Design Rule Check<br>Electronic Design Automation |

- FPAA Field Programmable Analog Arrays

- FPGA Field-Programmable Gate Array

- HDL Hardware Description Language

- HCI Hot Carrier Injection

- HNN Hardware Neural Networks

- IVR Input Voltage Range

- KCL Kirchhoff's Current Law

- KVL Kirchhoff's Voltage Law

- LVS Layout Versus Schematic

- MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

- MTDC Multiple Task Distribution Controllers

- NRD Non-Recoverable Degradation

- NMR *N*-tuple Modular Redundancy

- NP Nondeterministic Polynomial Time

- ODE Ordinary Differential Equation

- OpAmp Operational Amplifier

- OR Output Resistance

- OTA Operational Transconductance Amplifier

- OVR Output Voltage Range

- PID Proportional-Integral-Derivative (controller)

- RD Recoverable Degradation

- SAT Satisfiability Problem of Boolean Formulas

- SBD Soft Breakdown

- SPICE Simulation Program with Integrated Circuit Emphasis

- SR Slew Rate

- TE Technology Effects

- TDDB Time Dependent Dielectric Breakdown

- TMR Triple Modular Redundancy

- VHDL Very High Speed Integrated Circuit Hardware Description Language

- WCTDT Worst Case Task Distribution Time

# Introduction

The continuous spreading of embedded System-on-Chips interacting with its environment is inevitable. With the increasing dependency on embedded electronic devices, the failure susceptibility has to be minimized. However, new requirements like upcoming applications or new hardware platforms have to be faced and handled by the embedded system with equal consistency as the already known failure sources, impeding the efforts to minimize the failure susceptibility. The electronic systems need to be designed highly dependable and robust to execute their assigned tasks reliable. Further, any real-time bound needs to be hold, if the system is operated in a live-critical environment.

Therefore, designing reliable mixed-signal architectures using unreliable hardware is the key challenge. The unreliability is caused by different effects. Just increasing the integration density leads to degrading process reliability and device aging already. The proneness to production failures increases, permanently affecting the system behavior. Also, decreasing the technology size intensifies the failure susceptibility further, as do environmental effects. Any variation of the performances and the system behavior could eventually lead to failing components or failing task executions.

To handle or avoid failures, erroneous behaviors and performances affecting the system, counter mechanisms are necessary. Additionally, for embedded System-on-Chips those counter measurements need to apply autonomously during run-time, not affecting any real-time bounds. Hence, many reliable systems were proposed mainly for digital systems, not taking mixed-signal processing into account, let alone any kind of analog components.

Therefore, the goal of this thesis is to design a reliable analog architecture providing hardware redundancy and a dependable task distribution system. The cores are held redundant, forming a multi-core design with respect to mixedsignal processing. The task distribution system enhances the system to be dependable and robust to failures. Further, the reliability is increased by minimizing (to the maximum extent of eliminating) the single points of failure.

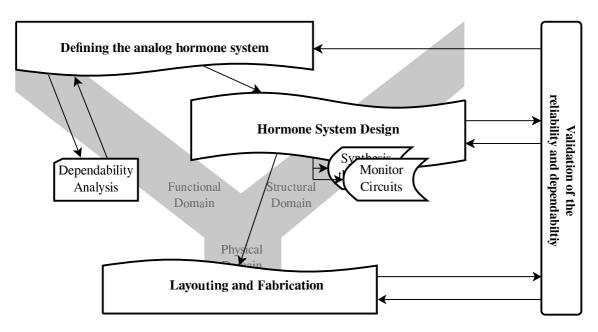

#### 1.1 Analog Circuit Design Flow

To design analog circuits from scratch is a challenging task. It starts with defining the designs' functional specification and ends at the physical layout, which satisfies the defined specifications. To meet the complexity of this task, several design steps in between are required to partition the design hierarchically into solvable subtasks. The design steps were classified in [GK83], the abstraction levels and domains of the design process were defined with a graph called Y-chart. Until nowadays, the application of the Y-chart has been edited and further defined for the complex analog design tasks [GDWL92, HBKK94]. The three axis of the graph illustrates three views of the design:

- **Functional Domain:** The functional domain describes the temporal and functional circuit behavior in different levels of abstraction. The design starts at the uppermost level, the concept layer, with the definition of the specification of the circuit. Descending to the algorithm layer, functional models are defined to describe the intended analog circuit behavior in a top-level and abstract manner. At the macro layer the transfer functions are determined by the desired behavior models, while the differential equations of the lowermost layer specify each component in detail.

- **Structural Domain:** The structural domain specifies the system and subsystems and the interconnections of all the devices. The behavior describing models at the block layer are mapped to top-level building blocks. Those blocks are either generated from scratch (a top-down design flow) or taken out of existing libraries (a meet-in-the-middle design flow). Descending the abstraction levels to the devices, all interconnections are being defined. Further,

Figure 1.1: Y-chart of the Analog Design with Exemplary Synthesis Steps [Ste11]

the size and the topology of the devices determine the behavior/transfer function of the circuit components. The proper selection of the device parameters classify the circuit as *specification is met*.

**Physical Domain:** At the physical domain the geometric properties of the system and all their components are defined. At the uppermost layer a general partitioning of the system occurs, followed by placing of the devices. The lowermost layer implies the layout generation, the implementation of the devices and their topology as polygons. With the layouted circuit the physical structure is realized in silicon, ready to go into production.

The different abstraction layers map the design flow from the top-level concept to the low-level components and all the needed steps in between. Descending layers, increasingly defining the details of the design, is called synthesis. Contrary, to verify the conformance of lower levels with higher levels even upon different domains is called analysis. Figure 1.1 shows the Y-chart with the analog design flow, beginning with the functional specification at the top-left side, showing a typical design flow of an analog circuit. For the final layouted design and the manufactured circuit, the specification is used as benchmark to be tested against.

#### 1.2 Circuit Reliability

The analog design still suffers from the major flaw of non-standardized analog design specification, huge design space and missing abstraction like Boolean algebra. So far, standardized components of analog circuit libraries are non existing. Operational amplifiers (OpAmp) or current mirrors (CM) are highly versatile and can be optimized in many directions, such as a high slew rate (SR), no (almost non) offset or many others. This variety hinders standardization and leads to the need to design analog parts almost always from scratch. In Chapter 5.1 follows a detailed list of the specification needed of the analog circuit components used for this thesis, indicating the need to design all components from scratch.

Over the last years, research identified different critical areas of analog circuits, which are classifiable by their failure severity. Also, the rising complexity of analog circuits due to increasing process variation and shrinking technology size cause further sensitive areas. Those areas within the design process call for either a full design verification [GDWM<sup>+</sup>08, GMDW11] to ensure reliability or reliable circuit enhancements to counteract the identified failure mechanisms [BGL<sup>+</sup>06] (Definition 1.2.1).

#### Definition 1.2.1 (Failure Mechanism)

Failure mechanisms are the physical progress of the failures (which are described by abstract failure models).

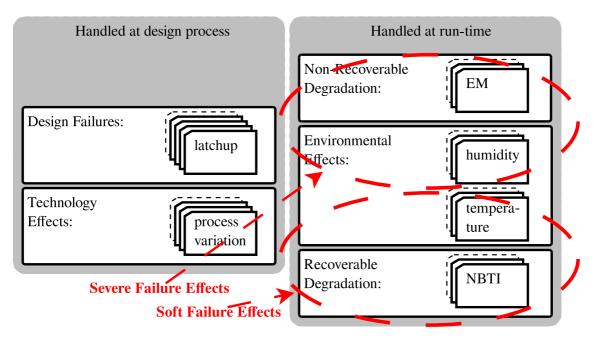

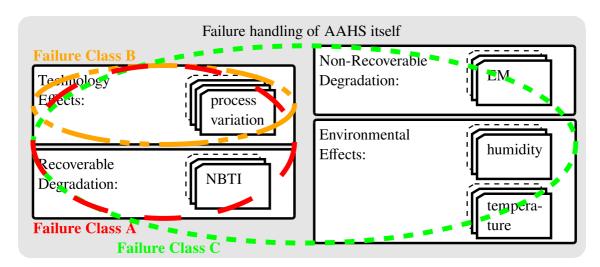

Typical circuit enhancements are increasing the transistors size to minimize failure occurrences, or monitoring circuits, which detect failures prematurely and allowing countermeasures to apply. Figure 1.2 structures a set of failure classes with their identified failures [Phe06]. Technology effects and design failures are confronted at the design process for example through verification methods [GMDW11]. Degradation and environmental effects, however, can not be countered by verification methods, but are handled during run-time. They are parted into two distinct categories, Definition 1.2.2 and 1.2.3:

#### **Definition 1.2.2 (Soft Failure Effects)**

Soft failing effects are physical effects, which influence/worsen the behavior of the circuit (in regard to the defined specification).

#### **Definition 1.2.3 (Severe Failure Effects)**

Severe failure effects are physical effects, which, if occurring, result in the total loss of functionality of the circuit.

Figure 1.2: Failure Severity Diagram

Soft failure effects are monitorable during runtime and the initial behavior recoverable, if according countermeasures are applied. Since severe failure effects must be prevented under all circumstances, the countermeasures need to be applied during the design process or monitor circuits must be able to detect failures before they occur. The following, detailed description of Figure 1.2 outlines several failure mechanisms:

- **Design Failures:** Until now the design process is mostly done by hand. Faulty and erratic design drafts are common, calling for the need to verify the designs to eliminate any self-made design failure. Typical design failures (DF) are shortages, latchups, leakages, current crowding and cross talks.

- The latchup effect is a shortage caused by a parasitic CMOS structure, which acts as two stacked thyristors (a P-N-P-N structure) keeping themselves in saturation and creating a low-impedance path between the two input signals [RCN04].

- Affected by leakage are capacitors, semiconductors and interconnects, increasing the power consumption leading to the total circuit loss eventually [Phe06, NC10].

- Charged capacitors are gradually discharged by the attached components, since even in power-down mode some components con-

duct small amounts of current. Also, imperfect or damaged dielectric materials of the capacitor lead to the flow of a leakage current, a constant loss of energy [NC10].

- Semiconductors suffer from the phenomenon of charges tunneling through the insulating regions or the source and drain terminals (called subthreshold conduction). The thickness of the insulating regions determines the leakage current flow, the amount of current, which is lost [NC10].

- Current crowding is an effect evoked by a nonhomogenous current density distribution through the (semi-)conductors, potentially leading to thermal runaways or electromigration, if not addressed properly during the design process [GAY89].

- In analog designs, the effects of crosstalk are defined as the capacitive effects a signal has upon a nearby signal. Crosstalked signals may falsify any output, the circuit is getting useless. The most common prevention methods of crosstalk are increasing the wire spacing and sizes, as well as a reordering of the wires [VMS97, VCMS<sup>+</sup>99].

Design failures are prevented by the design verification through the Design Rule Check (DRC), the Layout Versus Schematic (LVS) test and the parasitic extraction (for the final simulation runs) or other design verification methods [GMDW11].

- **Technology Effects:** Next to the design failures are the failures caused by the chosen technology and the fabrication process, for example the following:

- Process variation,

- Shrinking technology size,

- Shortening production time cycles.

Equivalent to design failures, design verification methods are needed to prevent these technology effects (TE) [GMDW11]. Other methods, like extensive simulation (Monte-Carlo simulations), may eliminate the failures caused by the technology, yes this precludes the desire to shorten the production time cycles.

**Non-Recoverable Degradation:** Severe impacts on analog circuits are caused for example by *Electromigration* (EM) or *Time Dependent Dielectric Breakdown*

(TDDB), abruptly ending the lifetime of the circuits [BGL<sup>+</sup>06, PWMC07, CLL<sup>+</sup>07].

- TDDB "is a measure of how long a dielectric can preserve its high resistivity under thermal and electrical stress." [HL12, p. 127] TDDB occurs as a failure mechanism in MOSFETs, if those are not operating within their specified operating voltages [BGL<sup>+</sup>06, Lie06]. As a result of the long-time application (beyond the operating voltage), the gate oxide is tunneled, forming a conducting path to the substrate [YFB<sup>+</sup>09] and [HL12, p. 127-145], destroying the MOSFET.

- EM is a failure mechanism of the conductors. "Current flow through a conductor produces two forces to which the individual metal ions in the conductor are exposed. [...] The second force [...] is generated by the momentum transfer between conduction electrons and metal ions in the crystal lattice. This force works in the direction of the current flow and is the main cause of electromigration." [Lie06, p. 39] The gradual movement of the metal ions in the direction of the current flow are causing the transport of the material. "This depletes the metal of some of its atoms upstream, while causing a buildup of metal downstream." [KK11, p. 31] The upstream thinning and the downstream buildup leads to two worst case failure state: an open or a short circuit [Lie06].

It is to state that already progressed degradation by the two mentioned failure mechanisms is irreparable. The degradation progress can be slowed down by, for example, reducing the current-density, but can never be recovered (from which the name derives: non-recoverable degradation (NRD)).

- **Environmental Effects:** Heat and radiation are the most commonly mentioned environmental sources, which influence analog circuits and cause failing effects. However, other environmental effects (EE) also exist. Following, a couple of environmental failure effects are introduced:

- Humidity effects provoke shortages, moisture absorption is either done by the package and the circuit or monitors power-off the affected areas to dry out.

- Hydrogen affects the conductors, inducing metal breakdowns similar to EM.

- High temperature degenerate the lifetime of the circuits drastically (accelerating degradation and EM), interrupted only by cool-down phases. Temperature changes can lead to thermal runaways, ending in a destructive manner.

- Radiation/Ionization effects can be classified into two mechanisms, which affect MOSFETs [SM88]:

- 1. The *Total Ionizing Dose* is the cumulative damage worsening the performance over the exposition time. The radiation affects the gate insulation layers of MOSFETs. "Radiation-induced trapped charge has built up in the gate oxide, which causes a shift in the threshold voltage [...] If this shift is large enough, the device cannot be turned off, even at zero volts applied, and the device is said to have failed by going depletion mode." [OM03, p. 483] This applies not only for N-type MOSFET, but also for P-type one, where the shifted transistor threshold is never again met.

- The *Displacement Damage* characterized the displacement of the atoms of the crystal lattice caused by high energetic particles. [SM88] The resulting change of the electrical property of the devices can cause latchups.

Devices exposed to radiation environments as for nuclear industries or for deep space missions are specifically made radiation hard. Radiation hardness is achieved through specific design, material selection and fabrication methods [SM88]. At the digital domain the equivalence to failures caused by radiation are Single-Event-Effects.

- **Recoverable Degradation:** Recoverable degradation (RD) effects are classified as soft failure effects. Threshold voltage drifts of transistors are recoverable and affect the circuits over time [CB05, DLS09, YFB<sup>+</sup>09, vRSH<sup>+</sup>15]. Those drifts are caused for example by:

- Hot Carrier Injection (HCI): "Over time, charge carriers (electrons for negative, or n-channel, MOSFETs; holes for positive, or p-channel, MOSFETs) with a little more energy than the average will stray out of the conductive channel between the source and drain and get trapped in the insulating dielectric. This process [...] eventually builds up electric charge within the dielectric layer, increasing the voltage needed to turn the transistor on. As this threshold voltage increases,

the transistor switches more and more slowly." [KK11, p.31] and [BGL<sup>+</sup>06, YFB<sup>+</sup>09]

(*Positive/Negative*) *Bias Temperature Instability* ((P/N)BTI): "Whenever you apply voltage to the gate, a phenomenon called bias temperature instability can cause a buildup of charge in the dielectric [...]. After that gate voltage is removed, though, some of this effect spontaneously disappears. This recovery occurs within a few tens of microseconds [...]." [KK11, p. 31] The quick recovery phase rises the difficulty to observe BTI effects [SGRG10]. Next to the threshold voltage drifts, a decrease of the transconductance and the drain current of the transistor manifests [JRSR05, BGL<sup>+</sup>06, KCS].

Degradation/aging effects can be treated, if detected, through recovery phases or decreasing the stress level of the circuit or its affected components. However, the according failure models and monitor circuits for the degradation detection, especially detecting BTI effects, are subject of current research as [SH11, vRSH<sup>+</sup>15] state.

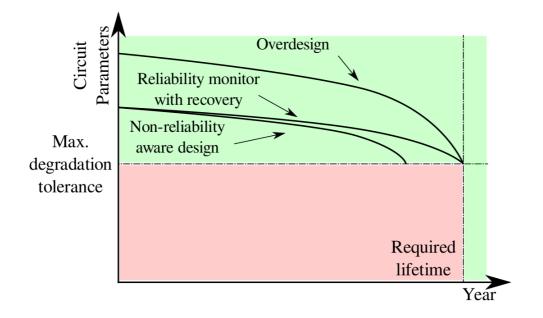

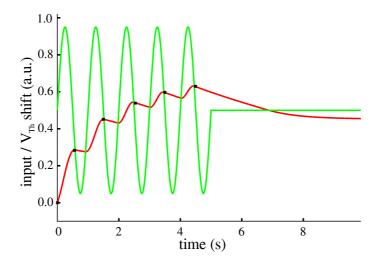

So far, a common method to tackle the environmental and degradation effects is to overdesign the analog circuits by increasing the transistor length and width greatly. Figure 1.3, based on [QS08, Figure 1], illustrates the change of the circuit parameters over time of different circuit designs. The red colored area is defined as non-acceptable circuit behavior due to the parameter decrease. It shows that overdesign and reliability monitoring with the appropriate recovery methods increase the device lifetime [QS08, HG14]. The paper states clearly, as do [JRSR05, SH11, ALHS12], the need for reliability measurements of mixed-signal systems. For example, [SH11] and [ALHS12] propose failure models to predict the degrading voltage drifts over time. To counter such degradation Figure 1.4 shows that a recovery phases of the stress signal reduces the probability for defect. The proposed failure model in [SH11] uses a stress signal, for example an arbitrary sine, as input. The output calculates the degradation parameter as the weighted sum of the probabilities for defect.

Further, in [JRSR05, YFB<sup>+</sup>09] failure mechanisms for NBTI, TDDB and HCI are presented. [Phe06] focuses on the impacts the scaling of the technology size has upon the circuitry and different failure mechanisms, clearly clarifying the challenge to increase reliability on the device level. However, this thesis focuses not as much upon the different failure mechanisms, but more on the different monitor circuits to detect the different failures. A survey of monitor circuits is

**Figure 1.3:** *Circuit Performance Degradation of Different Reliability-Aware Approaches based on* [QS08, Figure 1]

provided in [GALH08] with the distinction in offline and online monitoring. Further, the diagnostic values of the different monitor methods are given, as well as the strengths and weaknesses, allowing a quick, rudimentary comparison of self developed monitor circuits with already existing monitor circuits.

#### **Definition 1.2.4 (Online Monitoring)**

Online monitoring is defined as guarding the behavior of circuits, subparts and/or single transistors on-the-fly, while the circuit is operating.

Offline monitoring differs only within the definition that the circuit is turned off and the monitoring process has unlimited timing resources. Online monitoring (Definition 1.2.4) is preferred in all applications, which are constantly running, since the device does not have to be powered down or taken out of service. E.g. monitoring the health condition or keeping up predictive maintenance of a circuit is done while running. Incipient failures are detected and predefined actions are taken to minimize or even prevent any downtime. However, it has to be mentioned that online monitors are complex circuits itself, added to every existing circuit they monitor [GALH08]. Further, [SBCD04] states that some failure behaviors are more difficult even impossible to detect online, compared to offline tests. Typical fields of application of online monitors [GALH08, p. 4131] are:

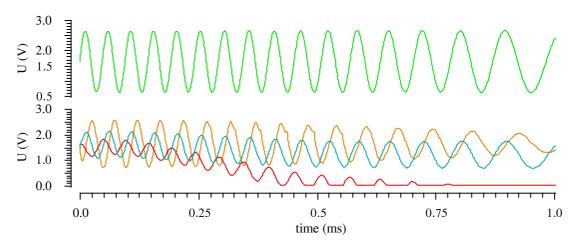

**Figure 1.4:** *Sine (green) Input Signal with Resulting Probability for Defect*  $V_{Th}$  *shift (red)* [SH11, vRSH<sup>+</sup>15]

- Temperature Monitoring,

- Condition Monitors and Tagging Compounds,

- Current monitors (e.g. power management, charging).

In [QS08] several difficulties of circuit monitoring are stated, whereas the important issue is of how monitor circuits actually experience the same stress, the same failing effect as the monitored devices. Each device, each component, each transistor experiences varying levels of stress, indicating monitor circuits for each of those, almost impossible to realize (because of e.g. process variation), even if the huge monitor overhead is set aside. Therefore, monitor circuits are assigned to groups of neighboring components, keeping the monitor overhead at an appropriate level. Compared to overdesigning, as shown in Figure 1.3, where the change in size of each transistor affects the overall performance of the circuit, calling for precise simulation results of the whole system, monitoring needs only to be done at the most critical areas of the circuits [QS08].

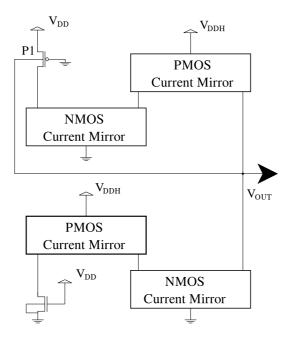

Also, an implementation to monitor NBTI is presented in [QS08], which mitigates the degradation effect by forward biasing the PMOS transistors. The approach introduces a failure mechanism for NBTI and provides a monitor to detect such an effect. Figure 1.5 shows an adaptive body biasing design to monitor NBTI.  $V_{DD}$  equals the supply voltage, while a second power supply  $V_{DDH} > V_{DD}$ for the body effect of P1 is needed, since  $V_{out} \stackrel{!}{=} V_{DD}$  applies, if the circuit is not

Figure 1.5: Analog, Adaptive Body Biasing Based NBTI Monitor [QS08]

stressed. With  $V_{DDH}$  being in full swing ( $V_{Bulk} > V_{Source}$  at P1) and the gate of P1 connected to ground, P1 is exposed to constant NBTI stress. This influences  $V_{OUT}$ , which equals the value of the NBTI monitoring metric, resulting in a decreasing  $V_{out}$  with increasing degradation of P1. If  $V_{OUT}$  equals  $V_{DD}$  no NBTI stress is applied. The approach presented in [SJL08] imposes an on-chip NBTI monitor circuit [SJL08, Fig. 1]. The output of two ring oscillators, one used as reference and stressed only during measurement periods and the other constantly stressed as the monitored circuit, are counted determining the oscillator frequency. The two frequencies are compared, allowing to state the degradation of the constantly stressed ring oscillator.

A circuit implementation to counteract TDDB is presented in [NC13]. The compensation approach is to double the circuit and if the monitor detects any severe breakdown a switching logic turns off the ,old' circuit, while the ,new' circuit is turned on. Yet, the circuit monitoring the soft breakdowns (SBDs), which occur before the catastrophic device failure happen, detectable by unexpected circuit performance variation, is more interesting [NC13]. Fig. 4(a) and (b) in [NC13] show the stress sensor and the reference circuit to monitor sudden performance variations (soft breakdowns). Both outputs are compared to detect the variations.

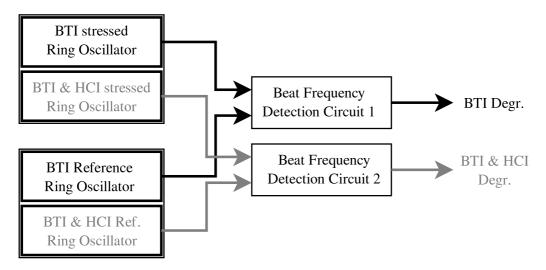

The on-chip implementation, shown in [KWPK10] catches BTI, HCI and TDDB failures. However, the focus lies on HCI, while TDDB is observed by long-

Figure 1.6: On-Chip Monitor to Detect HCI and NBTI Degradation [KWPK10]

term stress experiments. The failure detection of HCI is extracted by comparing the monitor results of two different runs:

- 1. The circuit is stressed so that the degradation is due only to BTI stress.

- 2. The circuit is stressed so that the degradation is suffered from BTI and HCI stress.

Figure 1.6 illustrates the block diagram to monitor HCI and BTI, using four ring oscillators (ROSC), while two are stressed and the other two unstressed as reference. The actual monitor circuit is the beat frequency detection monitor, seen in [KWPK10, Fig. 11(a)]. Using components like edge detectors and counters, the on-chip beat frequency detection is monitoring the frequency degradation of the ring oscillators.

Lastly, in [EKD<sup>+</sup>03] a monitor is presented to dynamically scale the supply voltage for power-aware computing. The new approach of dynamic voltage scaling is called Razor and is used for embedded, digital processors and SoCs. The dynamic scaling is based on the detection and correction of the timing errors of the circuit. A modified pipeline circuit to recover the delay path failures is also presented. The implementation of the digital monitor circuit is shown in [EKD<sup>+</sup>03, Figure 6], adjusting the supply voltage according to the monitored error rate during operation.

To the best of my knowledge, these are the most important monitor circuits. However, almost all monitor circuits are designed for digital circuits using ring oscillators. Recalling Figure 1.3 and page 10 the graph shows the increase of the lifetime of circuits, if the critical components are designed reliable (overdesigned). In [HG14] the authors analyzed the lifetime of MOSFETs exposed to BTI stress and how sizing effects and enhances the lifetime. The received perceptions were validated by a yield comparison of an OpAmp to its fabrication. Next, [JRSR05, Phe06] and [YFB<sup>+</sup>09, MDJG12] present analyzes of analog circuits done by specific reliability simulations. Those analyzes led to an increase of the reliability of circuits by detecting and defining the different impacts of failure mechanisms to improve the reliable design of the circuits. [YFB<sup>+</sup>09] proposes a methodology to design reliable circuits and testing them with according reliability simulations. The methodology is partitioned into four steps:

- 1. The process starts with a new circuit design initially simulated with BSIM models, which are extracted from the technology information.

- 2. Next to the degradation models in regard to the technology information, the stress voltages are abstracted from the circuit simulation runs.

- 3. With the degradation models, the circuit simulations and the abstracted stress voltages the circuit failure analysis is carried out, identifying the reliability-critical devices.

- 4. The analysis results state the lifetime and degradation behavior of the circuits. Further, based on the reliability-critical devices, design improvements are suggested to propose reliable designs.

Another approach is the hierarchical system reliability simulation flow, presented in [MDJG12]. The approach analyzes the reliability of mixed-signal circuits in a hierarchically manner. The flow to improve the reliability of the circuit is as follows:

- 1. Similar to divide and conquer, the system is partitioned.

- 2. Every part/subblock is remodeled as a stochastic degradation model indicating the performance evaluation over time of the subblock.

- The evaluation is done using HCI, BTI and SBD as failure models.

- To each subblock a sample corresponds, which is characterized by the deterministic input and degradation parameters.

- The behavior is modeled by a regression model.

3. The complete system level reliability analysis is evaluated using the generated models from each subblock, abstracting the system performances of the circuit.

The gain of reliable designed circuits is measured by comparing the increase of the design time and work load of the two approaches [YFB<sup>+</sup>09, MDJG12] compared to using monitor circuits. An increase of the circuit complexity increases the work load to design reliable significantly. However, reliable designed subcircuits, which are repeatedly appearing within an overall system, would noticeable decrease the monitor overhead to the price of a single time increased work load, a trade-off, which has to be carefully balanced out.

# 1.3 Reliability-Aware Architectures

Considering the difficulty to enhance reliability and dependability of circuits and systems, a set of criteria classify the different stages of difficulty. The criteria are derived from the conditions the system operates in, the addressed requirements the system needs to fulfill and desired degree of reliability and dependability. The conditions in which the circuit has to operate are for example:

- In a watery or extremly hot environment,

- In an isolated and hard to reach area,

- Exposed to high radiation.

Following are requirements, which the circuit has to fulfill. Examples are:

- Satisfying hard real-time bounds,

- Has to be a low power implementation,

- Minimized in size.

The degree of reliability and dependability for the reliable architecture is defined for example by the following:

- Quality of Service,

- Safety of the system stability,

- Security of the design,

- Needs to be absolutely dependable and reliable (fail-safe), because of operating life-saving devices.

#### 1 Introduction

Figure 1.7: Centralized Reliability-Aware Architectures [BBP13]

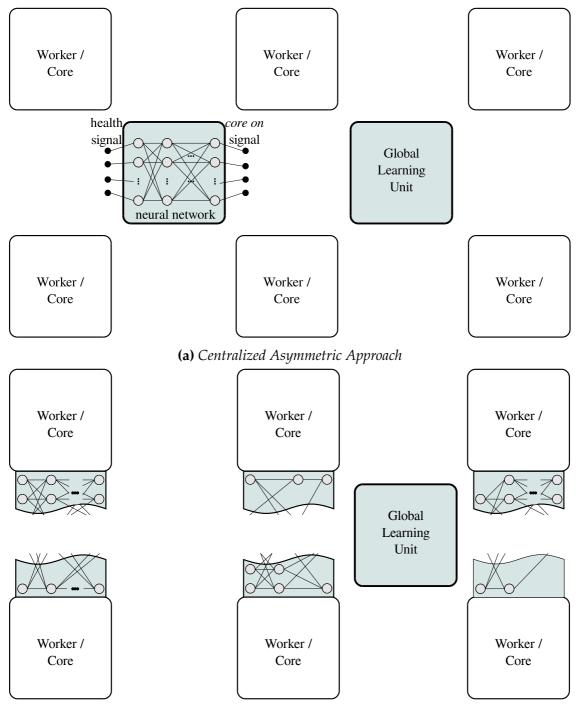

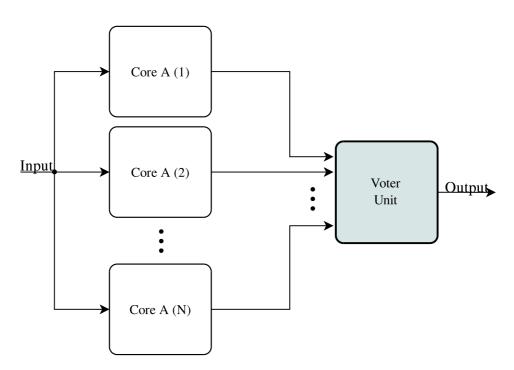

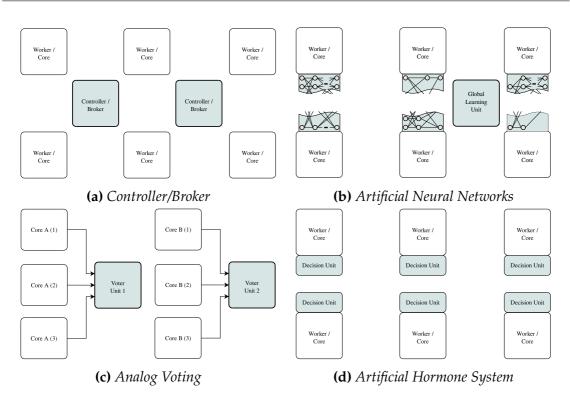

Next to clarify is how the system with its sensors and actuators are interacting with another. The communication can be done by point-to-point connections, by a network to allow advanced broadcasting or basic announcements or simply by signaling paths. Further, those connections are either single ended or advanced to buses to be more robust with a network protocol authorizing re-routing in case of transmission errors. This indicates the possibility of a path monitoring implemented to detect connectivity errors, missing data or the like. All this leads to the specification of a reliable architecture to satisfy the set of criteria defined above. Most commonly implemented are two approaches in the digital domain, which are introduced rudimentary, now. Figure 1.7 illustrates the centralized reliability-aware architecture of the two approaches.

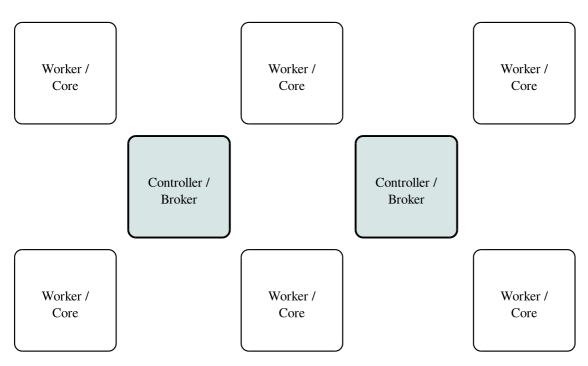

The Multiple Task Distribution Controllers (MTDC) is a redundant, centralized mechanism, regarded to be asymmetric, since cores can acquire two distinct roles: as task receivers (core) or task distributors (controller). Regularly, the controllers send life signs through the system to detect failures within the controllers and determine a leader<sup>1</sup>. The cores send health signals (suitability, health state, workload) to the controllers. The elected leader distributes the tasks upon the

<sup>&</sup>lt;sup>1</sup>A leader is in charge of the distribution. While a leader is determined, the other controllers are almost idle, only monitoring working cores and keeping their health signals active

received information. Further, it evaluates neighborhood relations for potential task clustering and watches, detects and counteracts failures. The leader is the only active controller, while the other controllers just maintain the received information to keep coherency with the leader, the global task distribution map.

The Auction-based Multi-Agent System (AMAS) is a partly decentral and redundant approach. It has two roles to distinguish, the role of the broker and the role of the clients and therefore is considered to be asymmetric. The task distribution is done through an auction initiated by the broker. The clients bid according to their suitability, etc. The highest bidder wins. In case of neighborhood relations the broker can decide to distribute the task to another client. Global task information is held by the broker. Self-healing is not intended by default. Life signs have to be send by the clients to the broker, who can detect and counteract failures, additionally. A dying broker is handled by redundant brokers and a frequent broker auction of the leading broker. To be regarded as completely decentralized, every core must be able to be a broker. This rises complexity to be comparable to a centralized task distribution controller, since additional tasks, like initiating auctions, collecting bids, distributing tasks, monitor clients, must be executable at each core.

However, those two approaches are only used as benchmark in Chapter 2 for the three following approaches, which are capable of being mapped into the analog domain.

### 1.3.1 Artificial Neural Networks

"Artificial neural networks are an attempt at modeling the information processing capabilities of nervous systems." [Roj96, p. 3]. Nervous systems as part of neural networks is a branch of neuroscience<sup>2</sup> [KSJ00, Fin01]. The research has investigated the neural network within brains and based on these discoveries developed computational models, the artificial neural networks (ANNs). The first

<sup>&</sup>lt;sup>2</sup>Neuroscience as a field of study dates back to early periods of human history. Evidences are stated that surgical practice on brains have already been performed during the Neolithic times to relieve cranial pressure or curing headaches. However, not until the mid of the nine-teenths century extensive neuroscientific knowledge was gained by systematic research, with a significant scientific increase through non-invasive studies of the brain of healthy test subjects [KSJ00, Fin01]. Neuroscience as topic includes a broad range of further studies: Molecular, cellular, developmental, structural, functional, evolutionary, computational, and medical aspects of the nervous system. The techniques have expanded from the individual nerve cells and their composition to complex activities of the brain.

Figure 1.8: Reliable Architecture using an ANN [Roj96, p.126]

of such computational models were introduced in 1943 by Warren McCulloch and Walter Pitts and laid the foundation to apply neural networks as instances of artificial intelligence [MP43]. After a period of depression in the 1970s and early 1980s, the neural network research experienced a renaissance in the mid 1980s through associative memory, perceptrons, support vector machines and more recently through deep learning [ZDL90, Hay98].

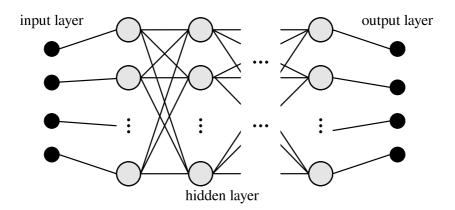

ANNs are systems of interconnected *artificial neurons*, as illustrated in Figure 1.8. "The input is processed and relayed from one layer to the other, until the final result has been computed." [Roj96, p.126] Sensor data for example serve as parameters of the input layer. The intermediate layers with its nodes are called hidden layers, since they are not directly interacting with the external environment [BH00]. "The determination of the appropriate number of hidden layers and number of hidden nodes (NHN) in each layer is one of the most critical tasks in the ANN design." [BH00, p. 22] The output layer represents the network func*tions* or the tasks the network has to process, all the needed steps for a successful execution are represented by the hidden layer. Adding/deleting the connections between neurons increase the quality of the output [vdM90]. Further, changing the weight of the interconnections results in different network functions/different outcomes of the tasks [Roj96]. The proper selection of the weights, the activation function and the net topology enables ANNs to learn to solve complex nonlinear functions and execute various tasks like an autonomously flying aircraft [Cen03]. Therefore, modeling ANNs requires the definition of three important elements [Roj96]:

- 1. The structure of each artificial neuron (nodes),

- 2. The topology of the interconnections (network),

Figure 1.9: Artificial Neuron (based on [Smi97, p.461] and [BH00])

3. The learning algorithm, which weights all interconnections.

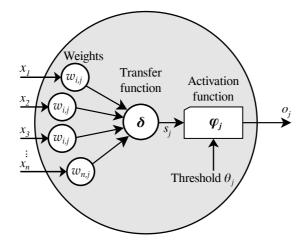

Figure 1.9 shows the structure of an artificial neuron (node) [Smi97, BH00], described by its four basic elements:

- Weight function: All input parameters  $x_i : i \in \{1..n\}$  are weighted  $w_{i,j} = [-1..1]$  against each other, defining the ratio of influence each input has upon the neuron. A weight of zero for an input is equivalent to a not-existing edge, neglecting that input and parts the inhibitory influence (negative sign) from the excitatory influence (positive sign) of that input.

- **Transfer function:** The transfer function  $\delta$  evaluates the overall influence of all inputs, the net value  $s_j$  of the neuron. Equation (1.1) states that the input parameter and the weights define the transfer function, but other characteristics of the architecture may also be included.

- Activation function: The activation function  $\varphi_j$  evaluates the net value  $s_j$  with the threshold value  $\theta_j$  and determines the output  $0_j$  of the neuron. Further,  $\varphi_j$  is defined by the topology of the network and represents the influence each neuron has upon the overall system [MS10]. The functions are usually monotonically increasing, for example as a ramp, piecewise linear or sigmoid, hyperbolic tangent function [SMN11]. Especially in multilayer-perceptron neural networks the sigmoid function is used mostly [Hay98].

**Threshold:** The threshold value  $\theta_j$  characterizes the minimum net value of a neuron to be activated, which corresponds to the threshold potential of biological neurons.

The evaluation of the output  $o_j$  of the artificial neuron is done by the threshold value subtraction, as equation (1.2) states [Roj96, BH00].

$$s_j = \delta_{i=1}^n (x_i w_{i,j}) \tag{1.1}$$

$$o_j = \varphi_j(s_j - \theta_j) \tag{1.2}$$

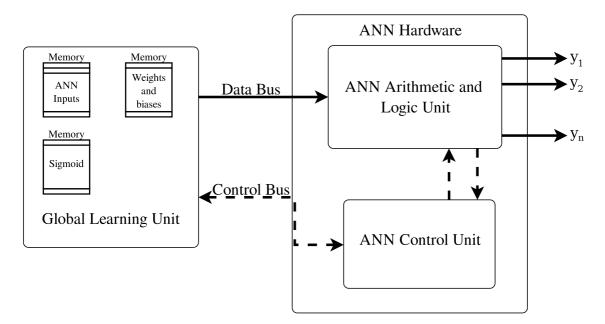

In [Mea89, Roj96, MS10] Hardware Neural Networks (HNNs) were introduced, which begin to supersede the numerous software based implementation [MS10]. In [MS10] the development of hardware implementations of ANNs of the past 25 years has been summarized and the advantages of HNNs compared to ANNs stated as:

- The increase in speed by taking advantage of hardware parallelism,

- The decreasing of costs by lowering for example the component counts and power requirements and

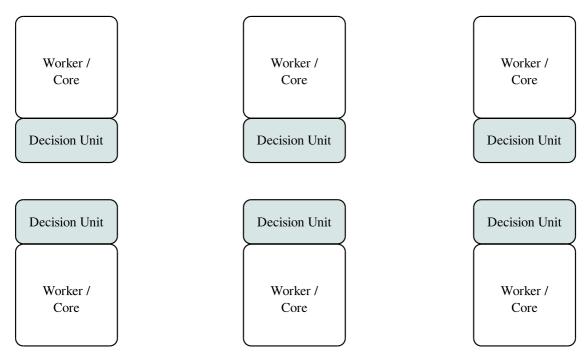

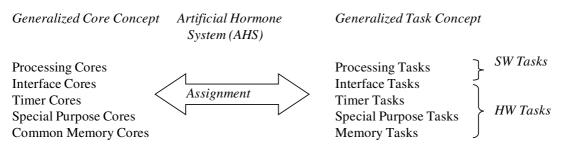

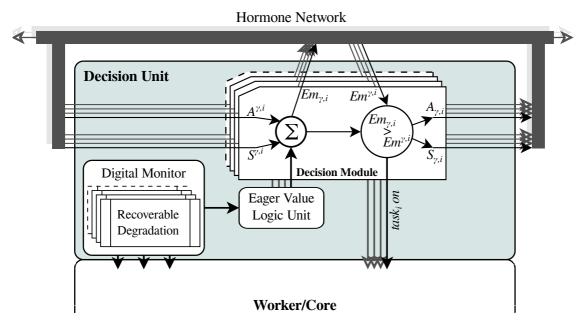

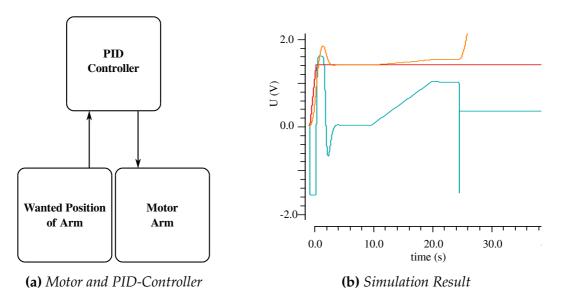

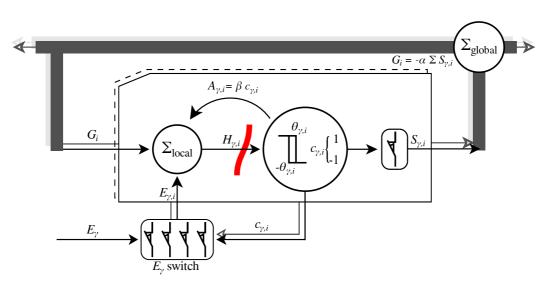

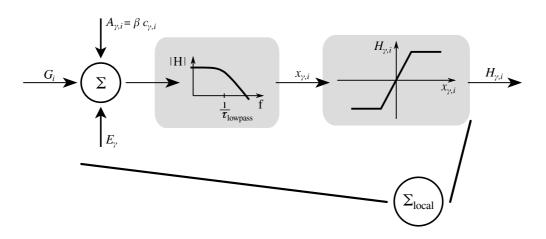

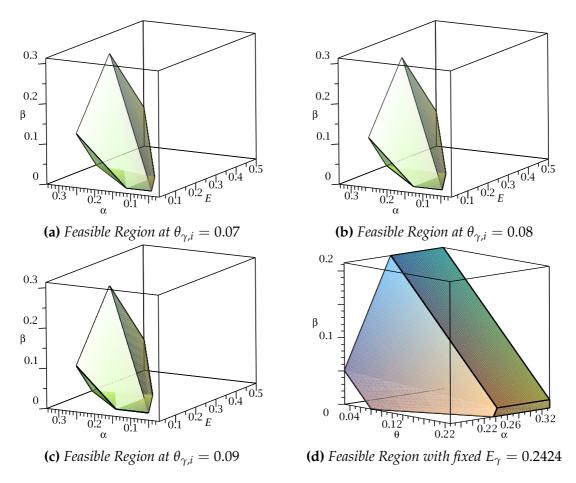

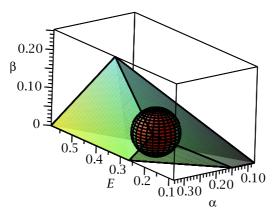

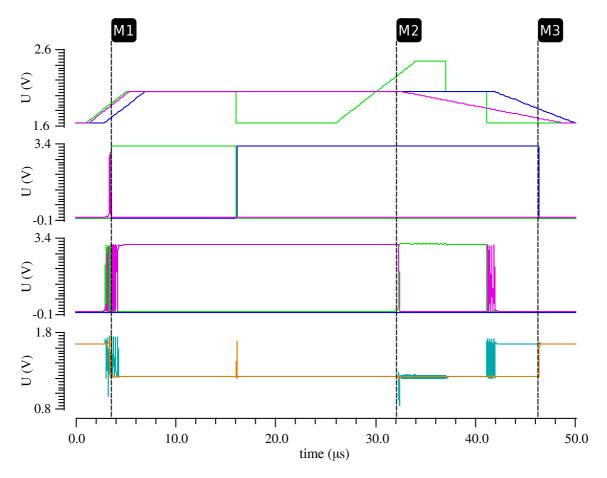

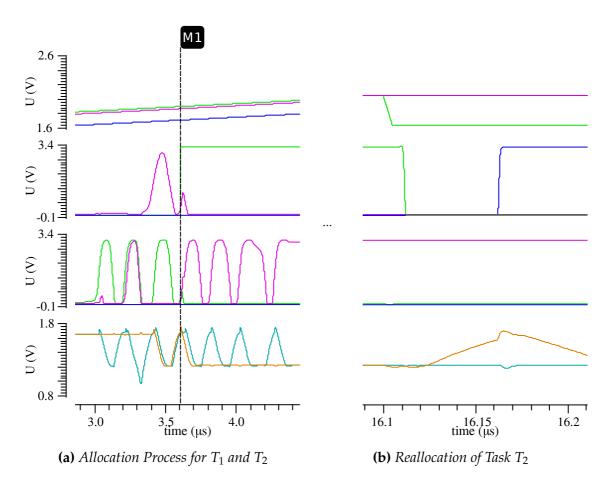

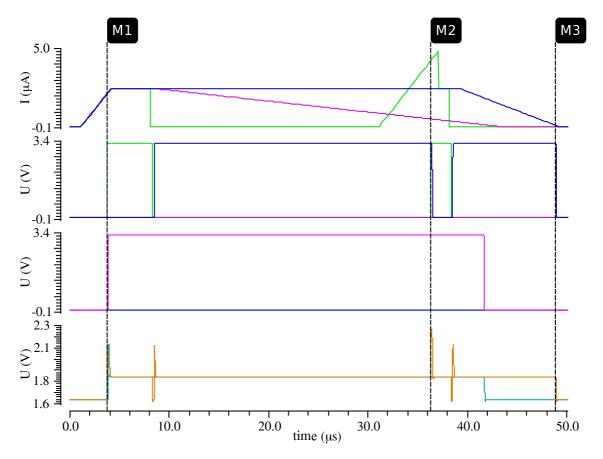

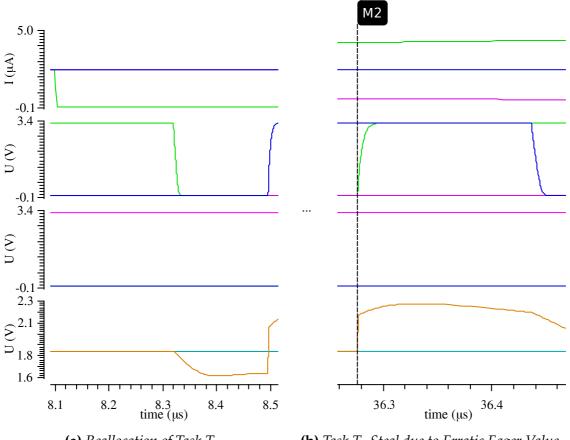

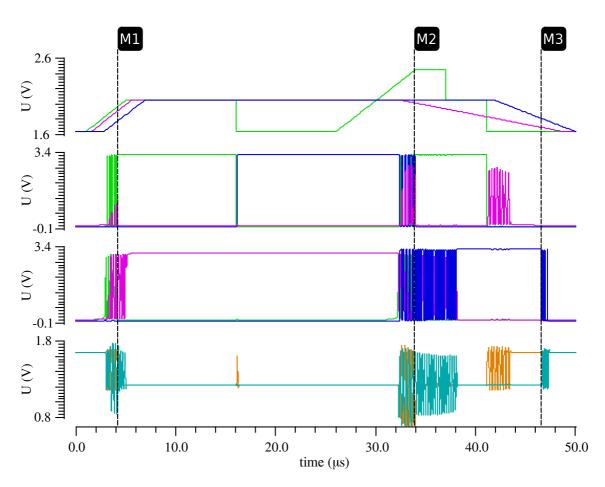

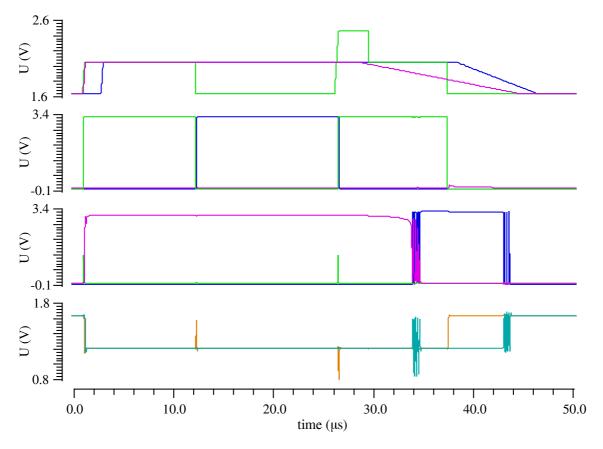

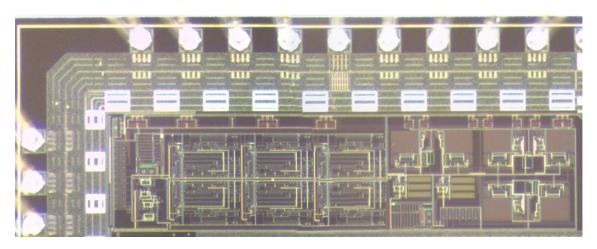

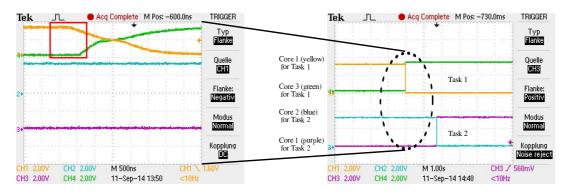

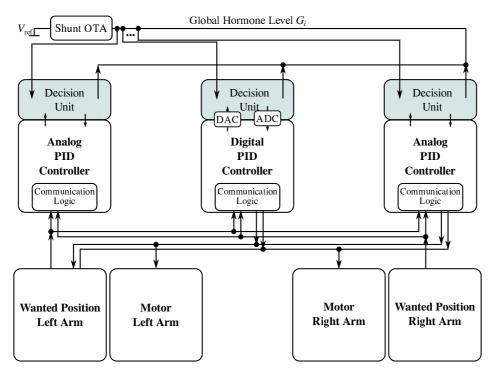

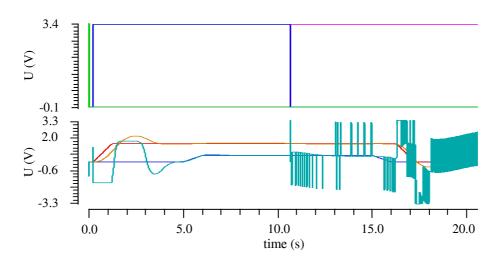

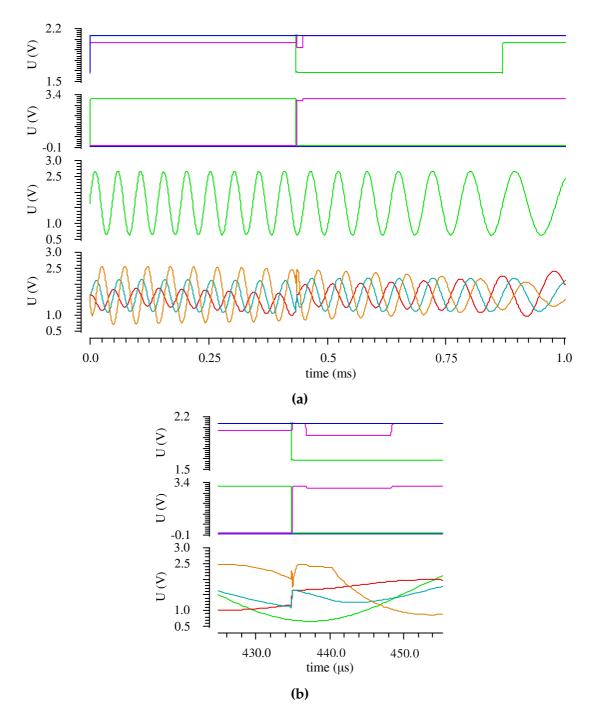

- The ability the counteract degradation through fault tolerance and keeping the system running with reduced performances.