### EUROPEAN ORGANIZATION FOR NUCLEAR RESEARCH

### ALICE upgrades during the LHC Long Shutdown 2

ALICE Collaboration

#### Abstract

A Large Ion Collider Experiment (ALICE) has been conceived and constructed as a heavy-ion experiment at the LHC. During LHC Runs 1 and 2, it has produced a wide range of physics results using all collision systems available at the LHC. In order to best exploit new physics opportunities opening up with the upgraded LHC and new detector technologies, the experiment has undergone a major upgrade during the LHC Long Shutdown 2 (2019–2022). This comprises the move to continuous readout, the complete overhaul of core detectors, as well as a new online event processing farm with a redesigned online-offline software framework. These improvements will allow to record Pb–Pb collisions at rates up to 50 kHz, while ensuring sensitivity for signals without a triggerable signature.

© 2023 CERN for the benefit of the ALICE Collaboration. Reproduction of this article or parts of it is allowed as specified in the CC-BY-4.0 license.

### Contents

| 1 | Intr | oductio   | n                                                                           | 11 |

|---|------|-----------|-----------------------------------------------------------------------------|----|

|   | 1.1  | Motiva    | ution                                                                       | 11 |

|   | 1.2  | Experi    | mental setup                                                                | 11 |

|   | 1.3  | Data s    | amples                                                                      | 13 |

|   | 1.4  | Outlin    | e                                                                           | 14 |

| 2 | Syst | em desi   | gn and common developments                                                  | 15 |

|   | 2.1  | System    | n design                                                                    | 15 |

|   | 2.2  | Comm      | on readout unit                                                             | 16 |

|   | 2.3  | The A     | LPIDE Chip                                                                  | 18 |

|   |      | 2.3.1     | Technology, Sensing, Pixels                                                 | 18 |

|   |      | 2.3.2     | Analog Front-End and Discriminator                                          | 19 |

|   |      | 2.3.3     | Matrix and Readout                                                          | 22 |

|   |      | 2.3.4     | Features for integration of ITS2 modules                                    | 23 |

|   |      | 2.3.5     | Power consumption                                                           | 24 |

|   |      | 2.3.6     | Results from the experimental characterization in laboratory and beam tests | 25 |

|   | 2.4  | SAMP      | Α                                                                           | 26 |

|   |      | 2.4.1     | CSA and shaper                                                              | 28 |

|   |      | 2.4.2     | ADC                                                                         | 28 |

|   |      | 2.4.3     | DSP and readout                                                             | 28 |

|   |      | 2.4.4     | Physical implementation and packaging                                       | 30 |

|   |      | 2.4.5     | SAMPA performance and tests                                                 | 30 |

| 3 | Dete | ector sys | stems                                                                       | 32 |

|   | 3.1  | Coord     | inate system                                                                | 32 |

|   | 3.2  | Inner 7   | Fracking System                                                             | 32 |

|   |      | 3.2.1     | Stave modules                                                               | 33 |

|   |      | 3.2.2     | Global support mechanics and services                                       | 38 |

|   |      | 3.2.3     | Readout and powering systems                                                | 40 |

|   |      | 3.2.4     | The readout system                                                          | 41 |

|   |      | 3.2.5     | The powering system                                                         | 42 |

|   |      | 3.2.6     | Component production, detector assembly, and commissioning on surface       | 42 |

|   |      | 3.2.7     | Detector calibration                                                        | 44 |

|     | 3.2.8   | Installation and global commissioning                     | 44 |

|-----|---------|-----------------------------------------------------------|----|

|     | 3.2.9   | First results from global commissioning                   | 45 |

| 3.3 | Muon    | Forward Tracker                                           | 48 |

|     | 3.3.1   | Detector layout                                           | 48 |

|     | 3.3.2   | Ladder assembly and testing                               | 49 |

|     | 3.3.3   | Half-Disks                                                | 51 |

|     | 3.3.4   | Cone and Barrel                                           | 51 |

|     | 3.3.5   | Services                                                  | 53 |

|     | 3.3.6   | Readout                                                   | 54 |

|     | 3.3.7   | Detector commissioning                                    | 54 |

| 3.4 | Time I  | Projection Chamber                                        | 56 |

|     | 3.4.1   | Introduction                                              | 56 |

|     | 3.4.2   | Readout chamber design                                    | 57 |

|     | 3.4.3   | Foil production, chamber production and quality assurance | 59 |

|     | 3.4.4   | Field cage                                                | 60 |

|     | 3.4.5   | HV system                                                 | 61 |

|     | 3.4.6   | Front-end electronics and readout                         | 62 |

|     | 3.4.7   | Installation                                              | 64 |

|     | 3.4.8   | Performance                                               | 65 |

|     | 3.4.9   | Calibration                                               | 66 |

| 3.5 | Fast In | teraction Trigger                                         | 69 |

|     | 3.5.1   | FT0                                                       | 69 |

|     | 3.5.2   | FV0                                                       | 70 |

|     | 3.5.3   | FDD                                                       | 70 |

|     | 3.5.4   | Electronics and readout scheme                            | 71 |

| 3.6 | Muon    | System                                                    | 72 |

|     | 3.6.1   | Muon Tracking                                             | 72 |

|     | 3.6.2   | Muon Identifier                                           | 76 |

| 3.7 | Transi  | tion Radiation Detector                                   | 81 |

|     | 3.7.1   | High-voltage distribution and common mode                 | 81 |

|     | 3.7.2   | Readout                                                   | 81 |

|     | 3.7.3   | Detector control                                          | 84 |

|     | 3.7.4   | Standalone tracking                                       | 85 |

|   |       | 3.7.5    | Calibration                                                    | 85  |

|---|-------|----------|----------------------------------------------------------------|-----|

|   |       | 3.7.6    | Quality Control                                                | 86  |

|   | 3.8   | Time-o   | f-Flight detector                                              | 87  |

|   |       | 3.8.1    | Implementation of continuous readout                           | 87  |

|   |       | 3.8.2    | The new Data Readout Module (DRM2)                             | 88  |

|   |       | 3.8.3    | Additional upgrades in low voltage and quality control systems | 90  |

|   | 3.9   | High-m   | nomentum particle identification                               | 92  |

|   |       | 3.9.1    | Introduction                                                   | 92  |

|   |       | 3.9.2    | Upgrading of readout firmware and trigger                      | 92  |

|   |       | 3.9.3    | New readout firmware and readout rate                          | 92  |

|   |       | 3.9.4    | Detector calibration formalism                                 | 93  |

|   |       | 3.9.5    | Other subsystems                                               | 93  |

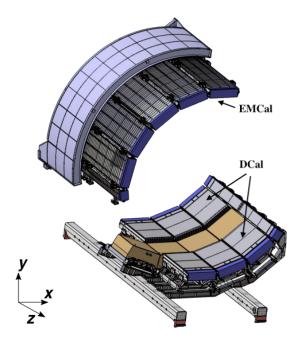

|   | 3.10  | Electro  | magnetic Calorimeter                                           | 96  |

|   |       | 3.10.1   | The readout system                                             | 97  |

|   |       | 3.10.2   | Trigger                                                        | 97  |

|   |       | 3.10.3   | Spare production                                               | 98  |

|   |       | 3.10.4   | Front-end electronics firmware upgrade                         | 98  |

|   |       | 3.10.5   | Data compression                                               | 99  |

|   |       | 3.10.6   | Calibration                                                    | 99  |

|   |       | 3.10.7   | Quality Control                                                | 99  |

|   | 3.11  | Photon   | Spectrometer                                                   | 101 |

|   |       | 3.11.1   | Detector layout                                                | 101 |

|   |       | 3.11.2   | Readout                                                        | 102 |

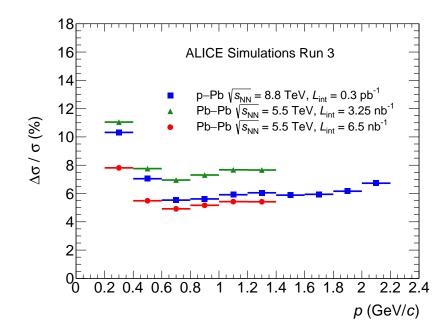

|   |       | 3.11.3   | Performance                                                    | 103 |

|   | 3.12  | Zero-D   | Pegree Calorimeter                                             | 105 |

| 4 | Maal  | honica   | and integration                                                | 108 |

| 4 | wiech | names a  | and integration                                                | 109 |

| 5 | Read  | lout and | d data processing                                              | 110 |

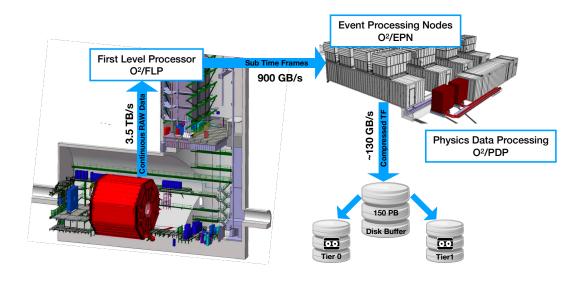

|   | 5.1   | Readou   | It data flow                                                   | 110 |

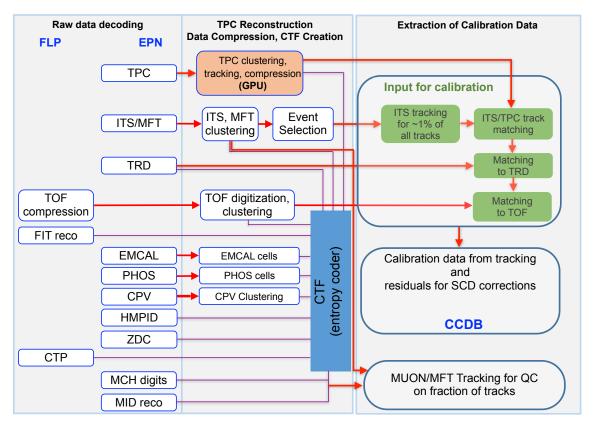

|   |       | 5.1.1    | Synchronous reconstruction                                     | 112 |

|   | 5.2   | First-L  | evel Processors                                                | 114 |

|   |       | 5.2.1    | The FLP detector readout farm                                  | 114 |

|   |       | 5.2.2    | Data quality control                                           | 115 |

|      | 5.2.3    | Services                                   | 116 |

|------|----------|--------------------------------------------|-----|

|      | 5.2.4    | Installation and commissioning             | 118 |

| 5.3  | Event    | Processing Nodes                           | 118 |

|      | 5.3.1    | EPN farm                                   | 118 |

|      | 5.3.2    | EPN installation                           | 119 |

|      | 5.3.3    | $O^2$ data distribution                    | 120 |

| 5.4  | Physic   | s data processing                          | 122 |

|      | 5.4.1    | Asynchronous reconstruction                | 122 |

|      | 5.4.2    | Simulation                                 | 123 |

|      | 5.4.3    | Analysis                                   | 124 |

| 5.5  | Centra   | l Trigger System                           | 124 |

|      | 5.5.1    | Requirements of the Central Trigger System | 125 |

|      | 5.5.2    | Trigger hardware and interfaces            | 125 |

|      | 5.5.3    | Trigger protocol and data format           | 125 |

| 5.6  | Detect   | or Control System                          | 126 |

|      | 5.6.1    | DCS computing hardware upgrades            | 128 |

|      | 5.6.2    | DCS software upgrades                      | 128 |

|      | 5.6.3    | DCS conditions data                        | 131 |

|      | 5.6.4    | DCS operator environment                   | 132 |

| Phys | sics per | formance                                   | 135 |

#### 7 Conclusions and outlook

6

140

# List of Figures

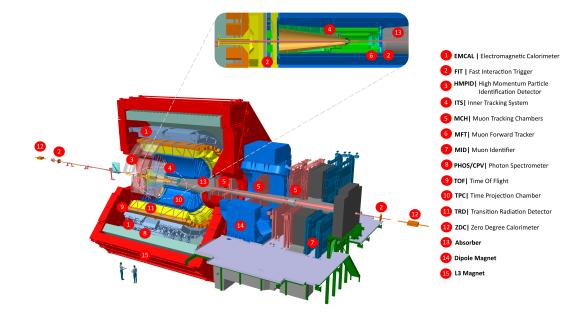

| 1  | ALICE 2 detector systems                                     | 12 |

|----|--------------------------------------------------------------|----|

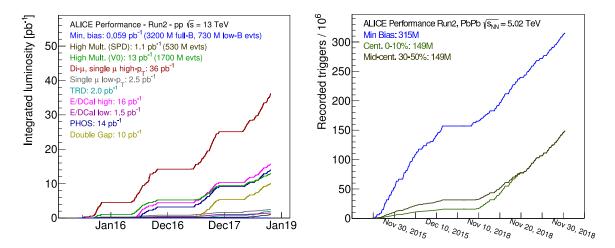

| 2  | Accumulation of integrated luminosity                        | 14 |

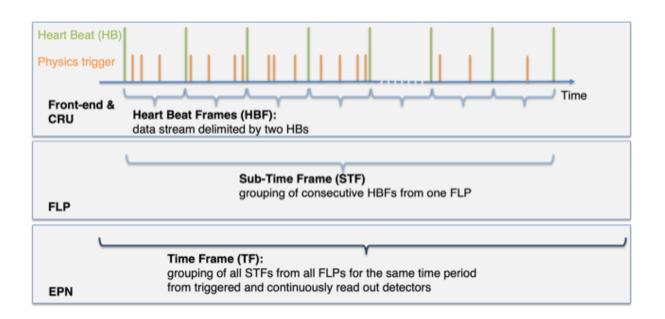

| 3  | Time frame and heartbeat frame structure                     | 16 |

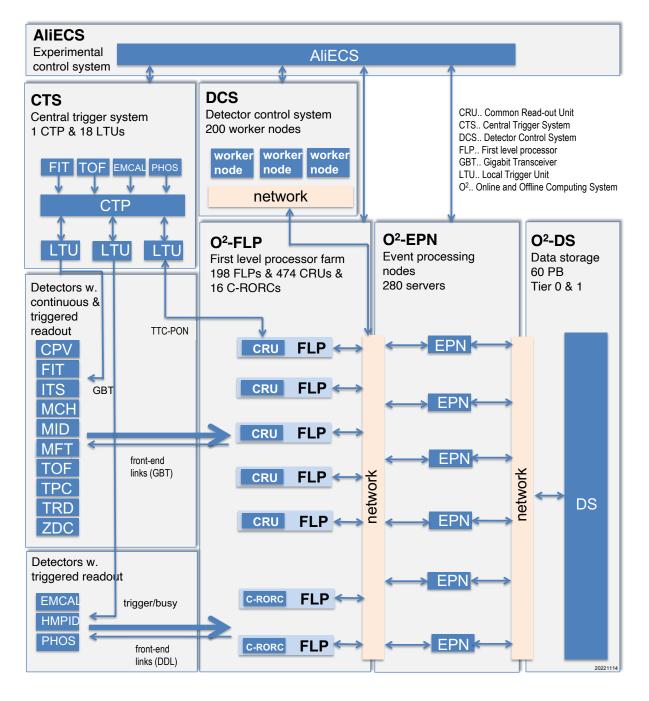

| 4  | ALICE readout architecture                                   | 17 |

| 5  | Block diagram of the common readout unit                     | 19 |

| 6  | Picture of a common readout unit                             | 20 |

| 7  | Picture of ALPIDE                                            | 20 |

| 8  | Cross section of ALPIDE pixel cell                           | 21 |

| 9  | ALPIDE architecture                                          | 21 |

| 10 | Block diagram of the ALPIDE chip.                            | 23 |

| 11 | Diagrams of the ITS2 inner barrel and outer barrel modules   | 24 |

| 12 | ALPIDE detection efficiency and fake-hit rate                | 25 |

| 13 | ALPIDE position resolution and cluster size                  | 26 |

| 14 | Block diagram of the SAMPA ASIC                              | 27 |

| 15 | Block diagram of the front-end implemented in the SAMPA ASIC | 28 |

| 16 | Block diagram of the SAMPA SAR ADC                           | 29 |

| 17 | Diagram of SAMPA DSP                                         | 29 |

| 18 | SAMPA chip                                                   | 30 |

| 19 | Example response curve for 4 mV/fC configuration.            | 31 |

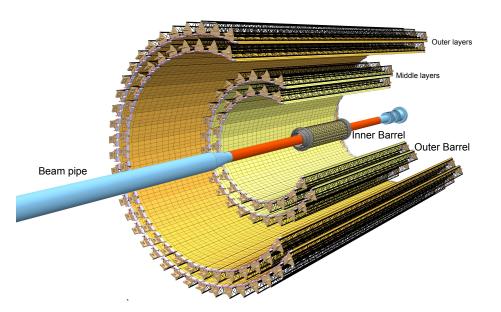

| 20 | ITS2 layout                                                  | 33 |

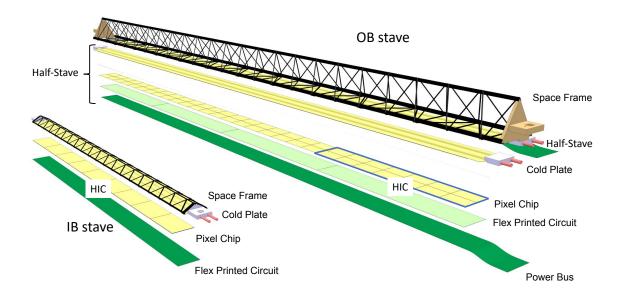

| 21 | ITS2 stave layout                                            | 34 |

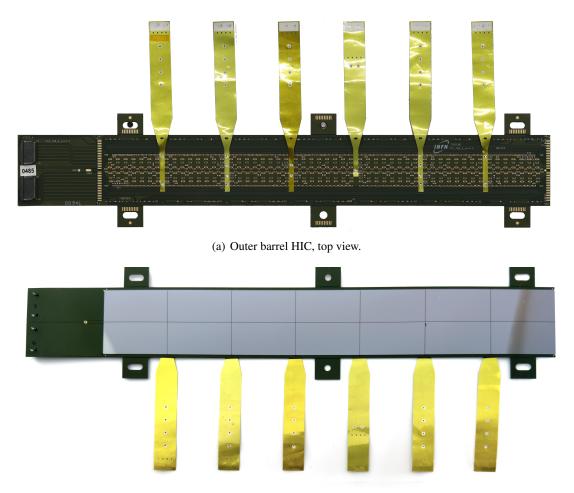

| 22 | ITS2 hybrid integrated circuit                               | 35 |

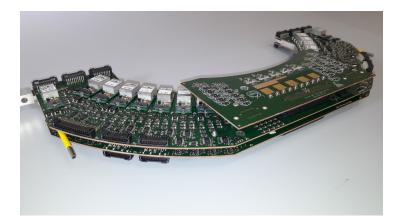

| 23 | ITS2 outer barrel HIC                                        | 36 |

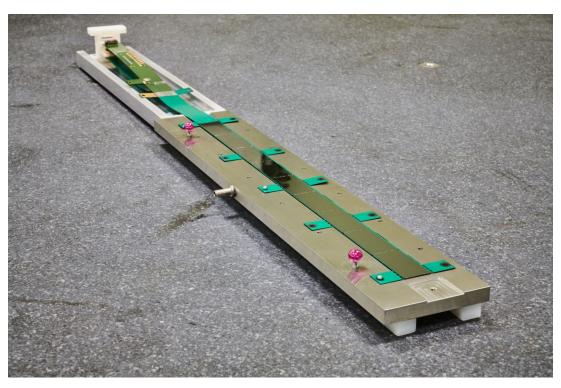

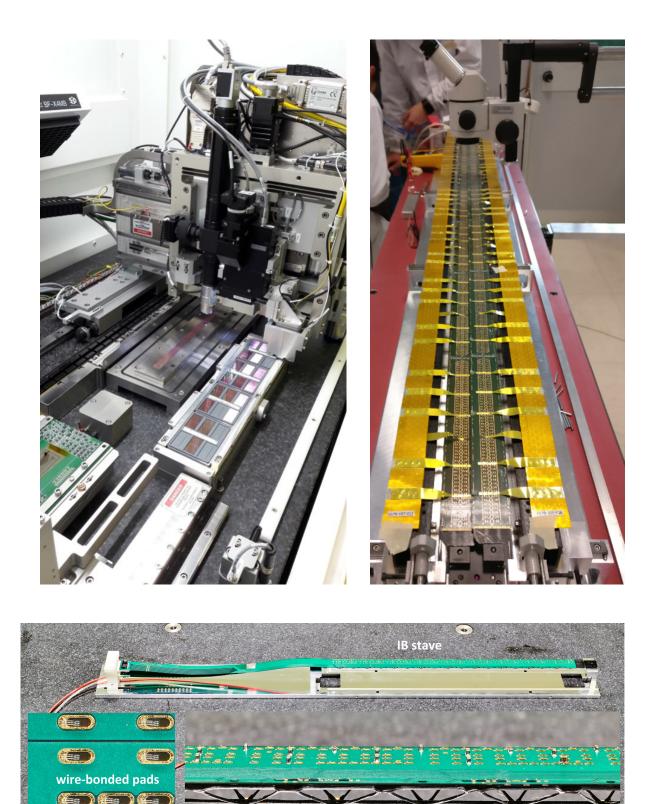

| 24 | Pictures of the ITS2 assembly                                | 37 |

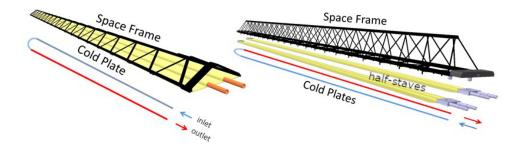

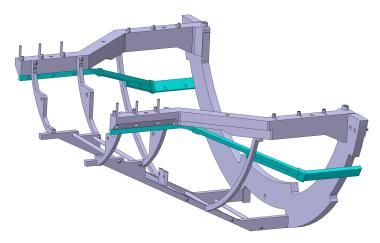

| 25 | Space frame and cold plate cooling scheme                    | 38 |

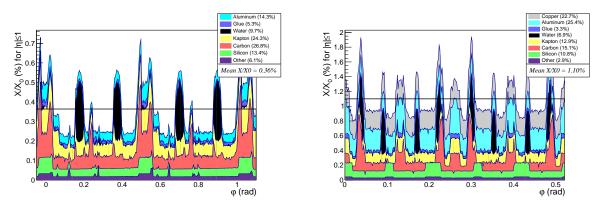

| 26 | Material composition of ITS2 staves                          | 39 |

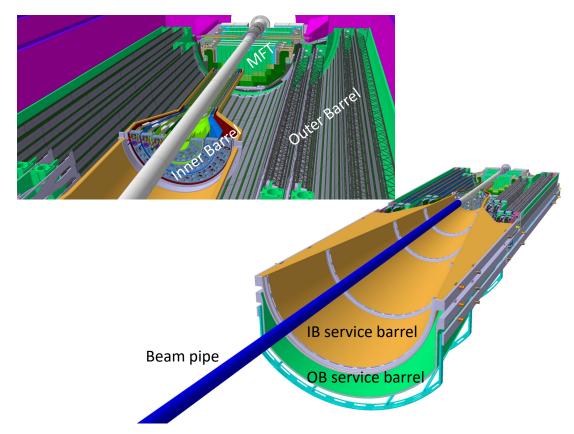

| 27 | ITS2 support structures                                      | 40 |

| 28 | Readout unit design                                          | 41 |

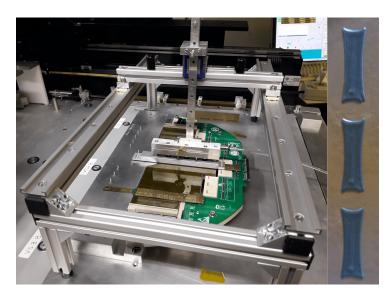

| 29 | Schematic description of the stave production workflow.      | 43 |

| 30 | ITS2 in the clean room during on-surface commissioning       | 43 |

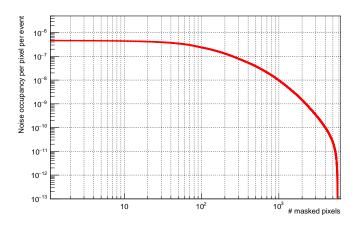

| 31 | The fake-hit rate of an inner half-barrel                    | 44 |

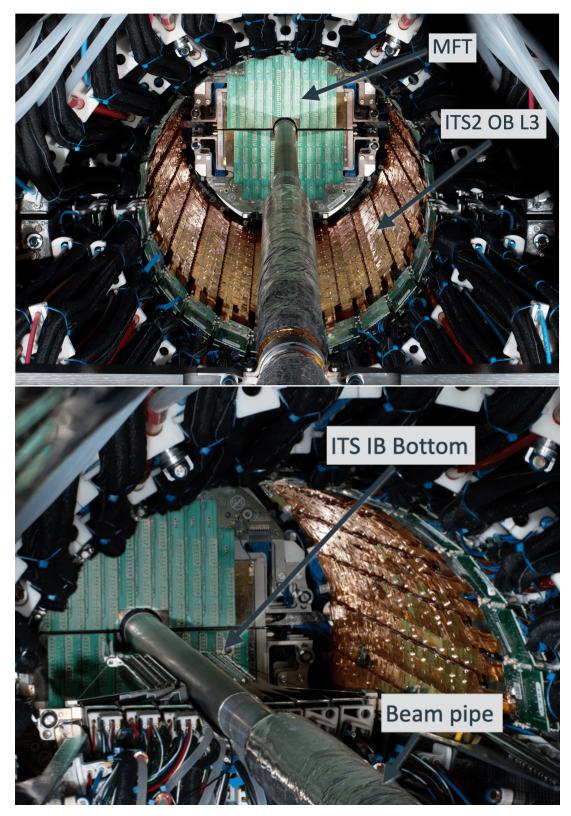

| 32 | ITS2 installation                                            | 46 |

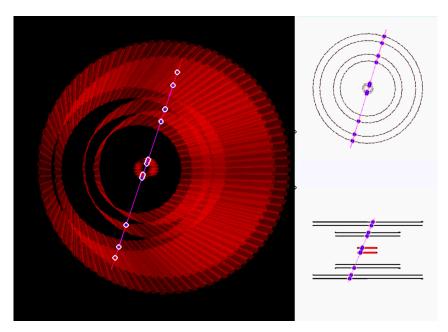

| 33 | Cosmic muons in ITS2                          | 47 |

|----|-----------------------------------------------|----|

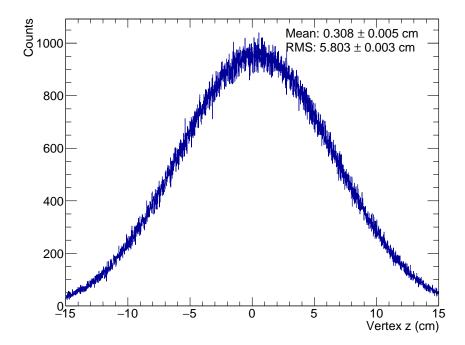

| 34 | Primary vertices reconstructed by ITS2        | 47 |

| 35 | Overview of Muon Forward Tracker              | 48 |

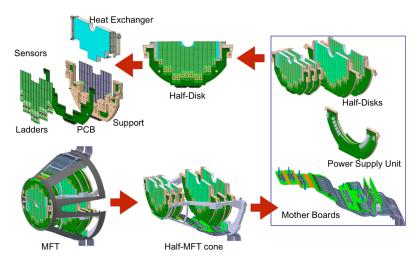

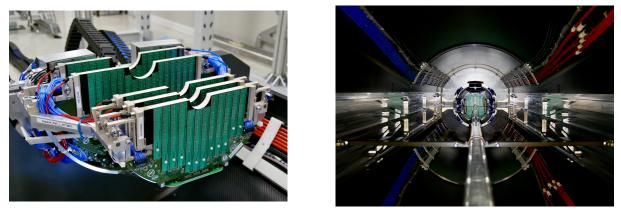

| 36 | MFT detector elements                         | 49 |

| 37 | FIT installation                              | 49 |

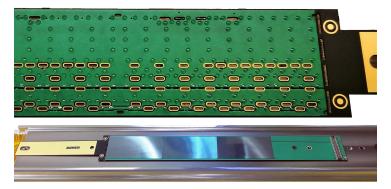

| 38 | MFT ladder                                    | 50 |

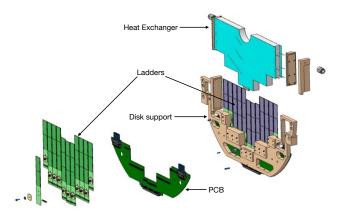

| 39 | Half-disk (exploded view)                     | 52 |

| 40 | MFT disk gluing                               | 52 |

| 41 | Half-cone structure                           | 53 |

| 42 | MFT PSU boards                                | 54 |

| 43 | MFT sensors noise rate                        | 55 |

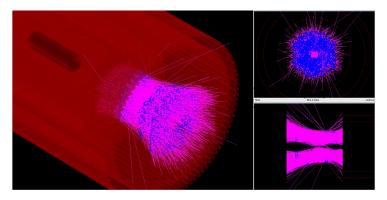

| 44 | Event display                                 | 55 |

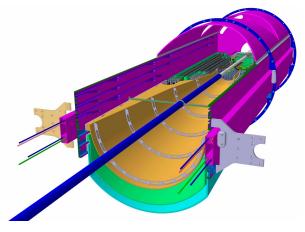

| 45 | Schematic view of the ALICE TPC.              | 56 |

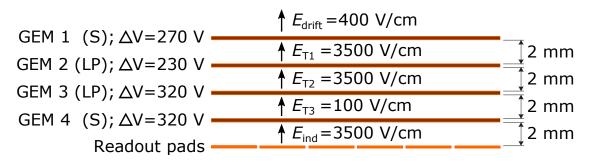

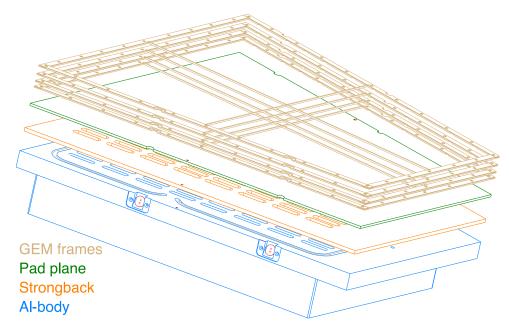

| 46 | GEM stack                                     | 57 |

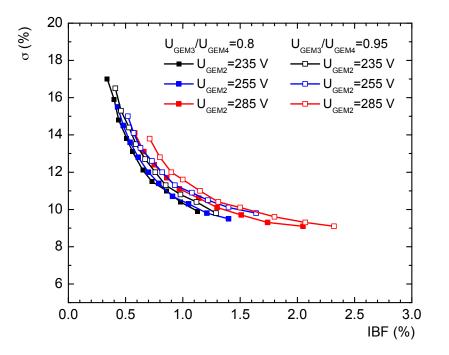

| 47 | Energy resolution as function of ion backflow | 58 |

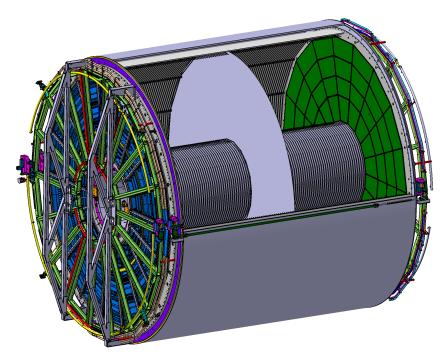

| 48 | Exploded view of IROC                         | 59 |

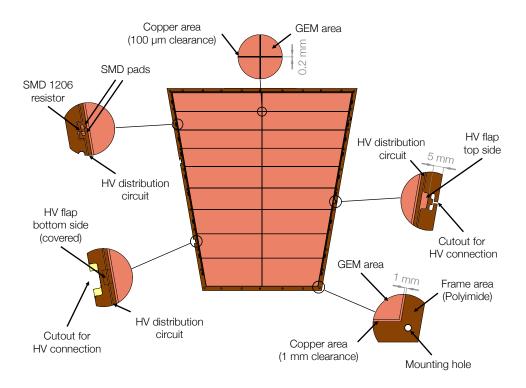

| 49 | GEM design details                            | 61 |

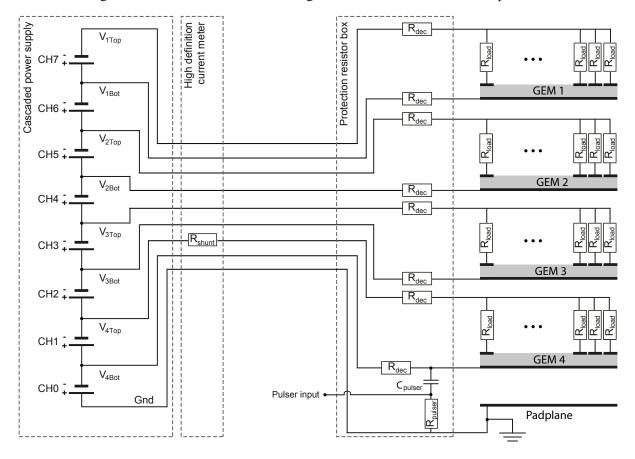

| 50 | GEM stack powering                            | 62 |

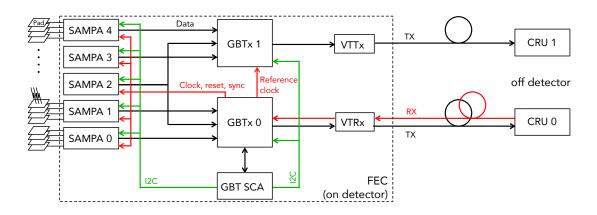

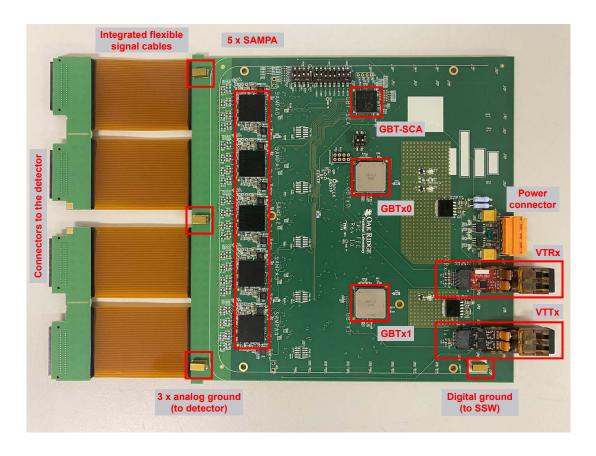

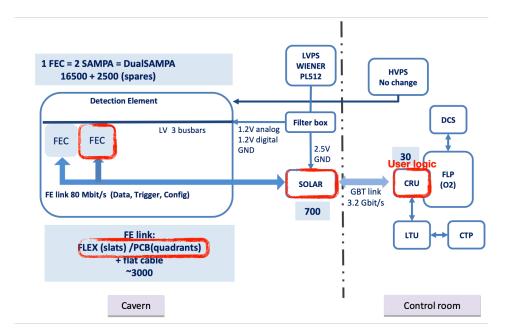

| 51 | TPC readout system                            | 63 |

| 52 | TPC FEC layout                                | 64 |

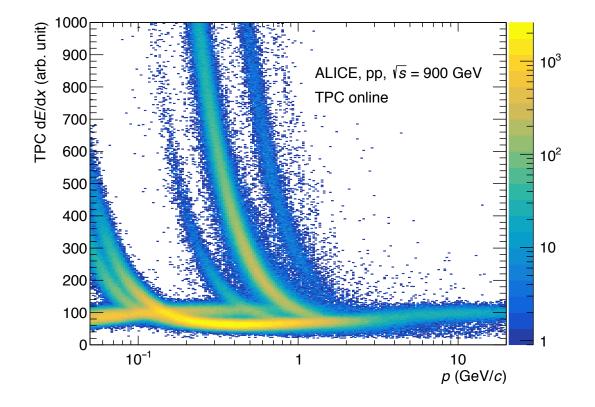

| 53 | TPC d $E$ /d $x$ performance in pilot beam    | 66 |

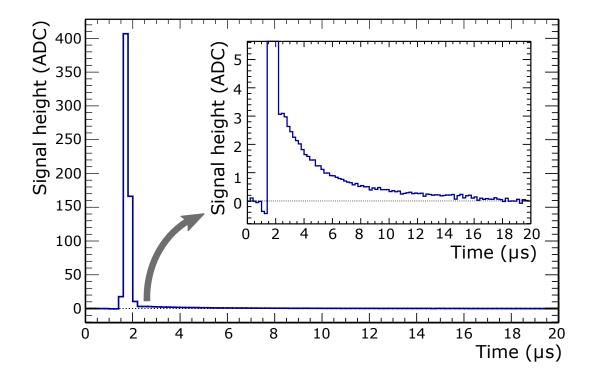

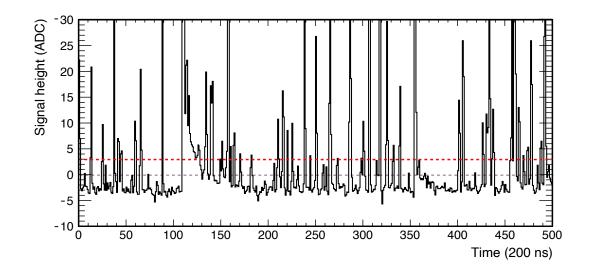

| 54 | Ion tail measured in TPC GEM                  | 67 |

| 55 | Ion tail and common-mode effect in TPC GEM    | 68 |

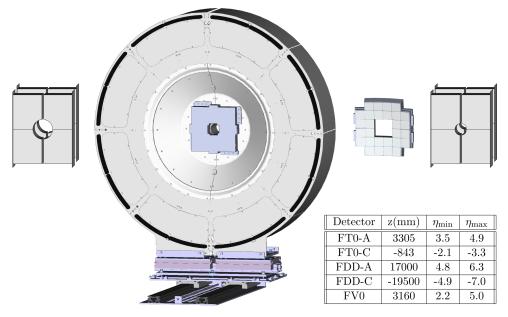

| 56 | Overview of FIT detectors                     | 69 |

| 57 | Picture of FV0                                | 70 |

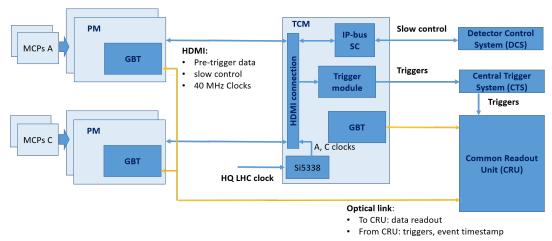

| 58 | Block diagram FIT readout                     | 71 |

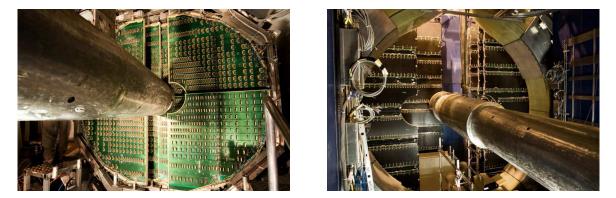

| 59 | Tracking system                               | 72 |

| 60 | Tracking readout scheme                       | 73 |

| 61 | DualSAMPA                                     | 73 |

| 62 | Electronic links                              | 74 |

| 63 | FLEX scheme                                   | 74 |

| 64 | SOLAR scheme                                  | 75 |

| 65 | Data flow                                     | 75 |

| 66 | CRU Scheme                                           | 76 |

|----|------------------------------------------------------|----|

| 67 | Overview of one MID half-plane in open position      | 77 |

| 68 | FEERIC architecture and picture                      | 79 |

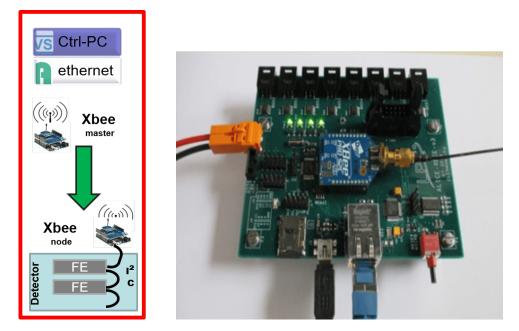

| 69 | Wireless threshold distribution                      | 79 |

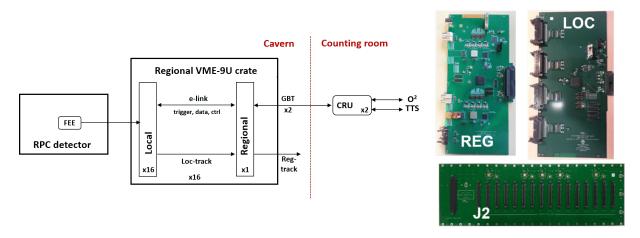

| 70 | MID readout architecture                             | 80 |

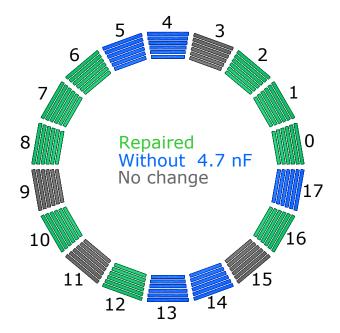

| 71 | High-voltage status TRD supermodules                 | 82 |

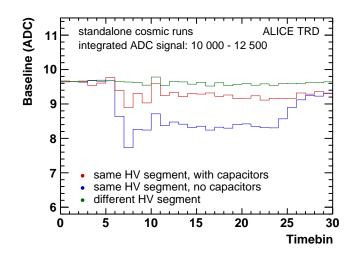

| 72 | TRD common-mode signal                               | 82 |

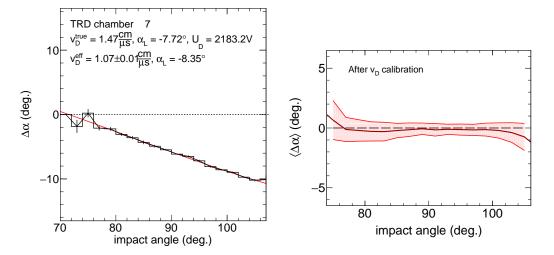

| 73 | TRD calibration                                      | 85 |

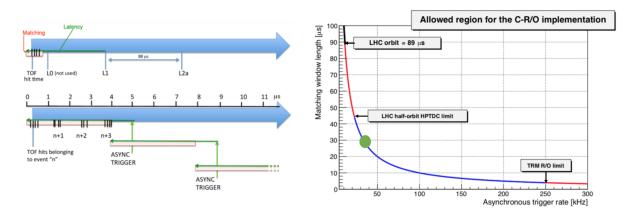

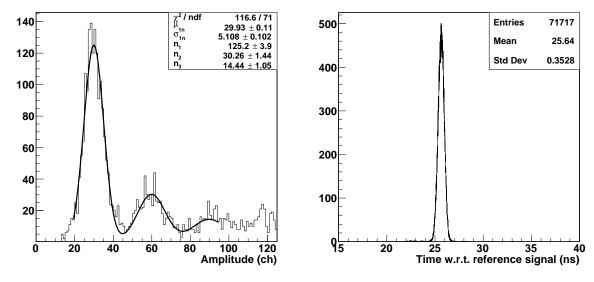

| 74 | TOF continuous readout implementation                | 87 |

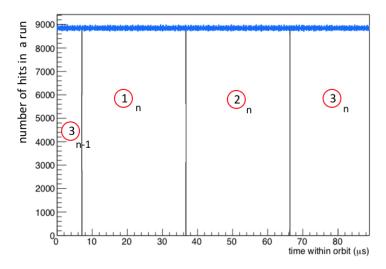

| 75 | TOF hit time distribution readout in continuous mode | 88 |

| 76 | TOF DRM2 card components                             | 89 |

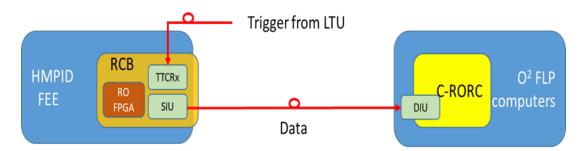

| 77 | HMPID front-end electronics                          | 92 |

| 78 | HMPID data acquisition                               | 93 |

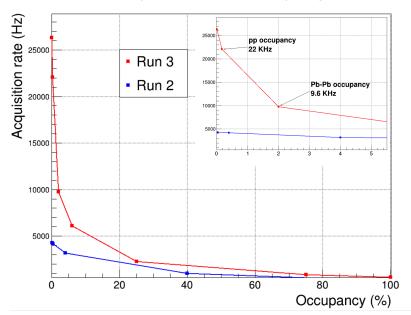

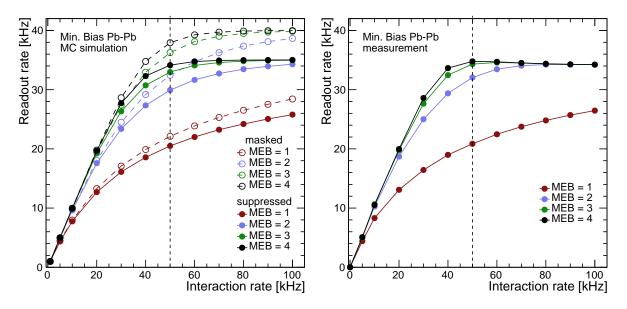

| 79 | HMPID event rate as a function of occupancy          | 94 |

| 80 | HMPID event rate as a function of occupancy          | 95 |

| 81 | Schematic view of EMCal                              | 97 |

| 82 | SRU readout rate                                     | 99 |

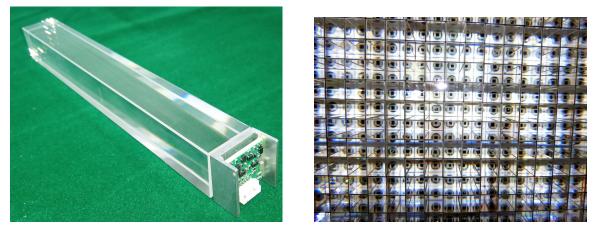

| 83 | PHOS module                                          | 01 |

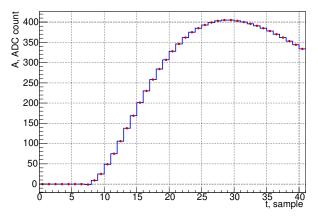

| 84 | Signal waveform of PHOS FEE channel                  | 02 |

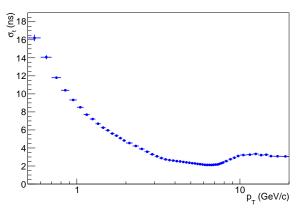

| 85 | PHOS time resolution                                 | 04 |

| 86 | Performance of ZDC digitizer                         | 07 |

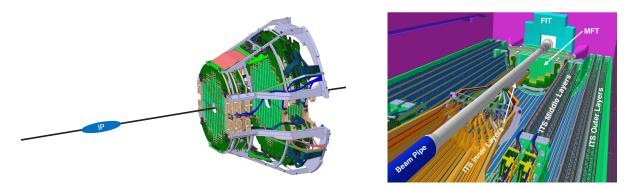

| 87 | Support of beampipe, ITS2, and MFT 1                 | 08 |

| 88 | ALICE 2 beampipe                                     | 09 |

| 89 | Readout and processing overview                      | 11 |

| 90 | Synchronous reconstruction workflow                  | 12 |

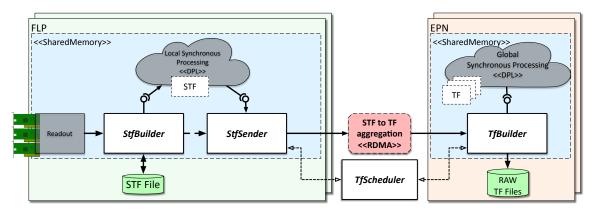

| 91 | FLP dataflow                                         | 15 |

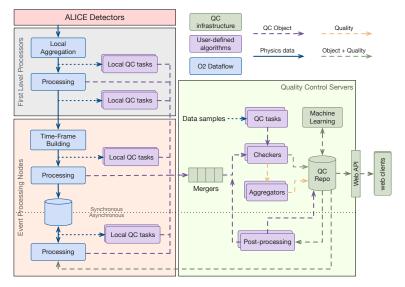

| 92 | $O^2$ Quality Control design                         | 16 |

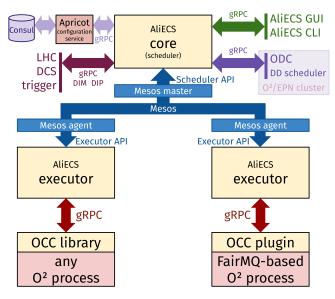

| 93 | AliECS design                                        | 17 |

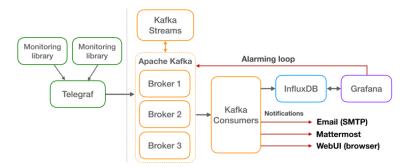

| 94 | The $O^2$ computing system monitoring design         | 18 |

| 95 | The ALICE CR0 data centre which houses the EPN farm  | 19 |

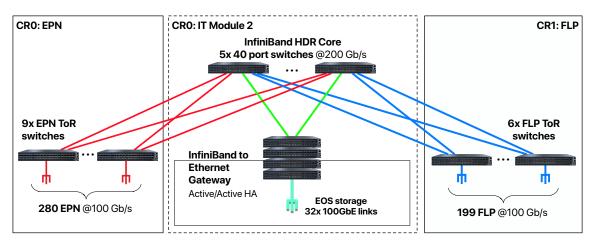

| 96 | Network diagram of the Run 3 $O^2$ facility          | 20 |

| 97 | Data distribution software framework                 | 21 |

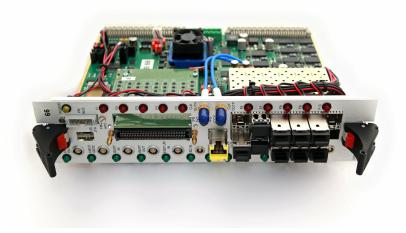

| 98 | Photograph of a CTP module                           | 26 |

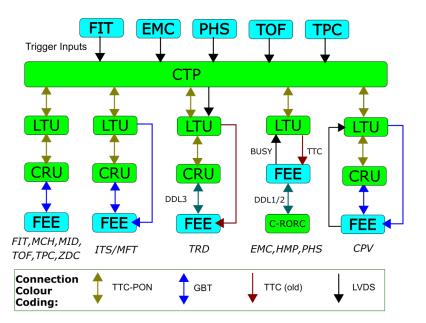

| 99  | Trigger system overview                                  | 127 |

|-----|----------------------------------------------------------|-----|

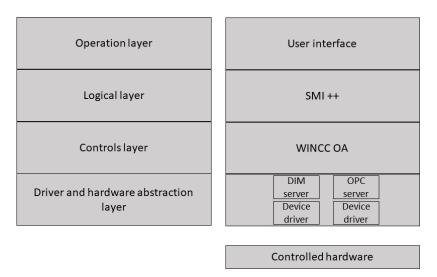

| 100 | DCS software architecture.                               | 129 |

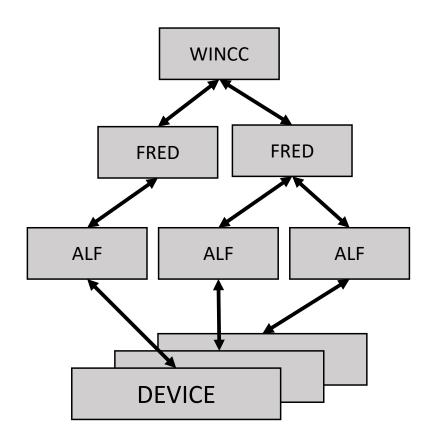

| 101 | Access to the hardware implemented in ALF-FRED mechanism | 130 |

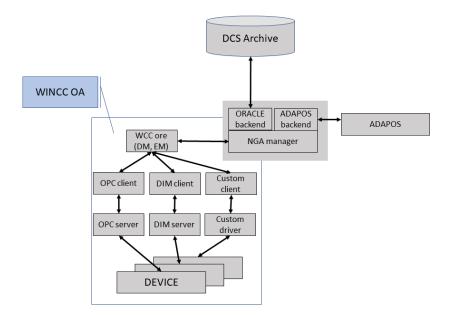

| 102 | DCS conditions data flow to ORACLE and ADAPOS            | 132 |

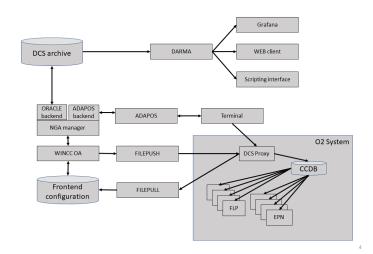

| 103 | DCS data exchange with $O^2$ and external consumers      | 133 |

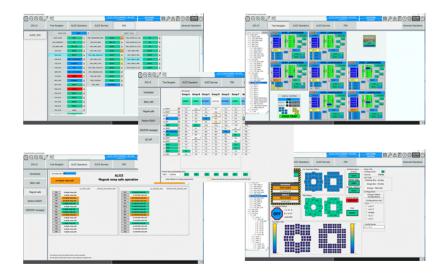

| 104 | ALICE DCS UI with various panels used by the operators.  | 133 |

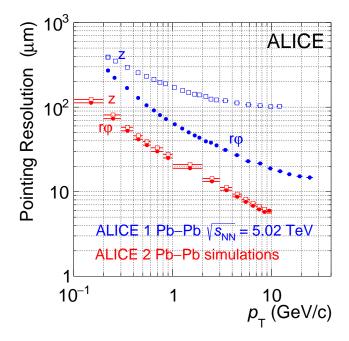

| 105 | Impact parameter resolution                              | 135 |

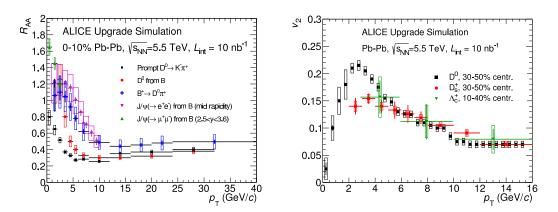

| 106 | Projections for charm/beauty $R_{AA}$ and $v_2$          | 135 |

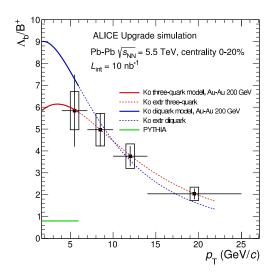

| 107 | Beauty baryon-to-meson ratio projections                 | 137 |

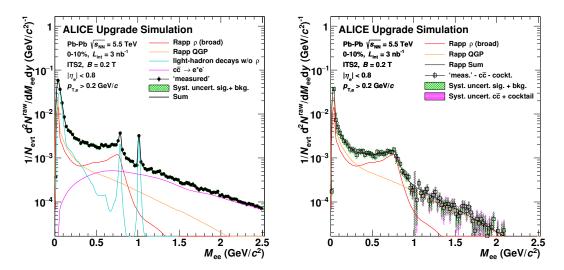

| 108 | Di-electron performance                                  | 137 |

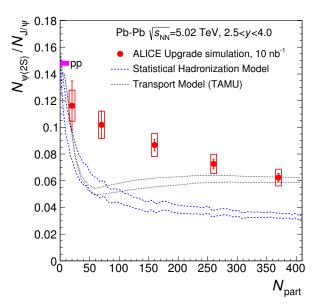

| 109 | Performance projection for $\psi(2S)$ and $J/\psi$       | 138 |

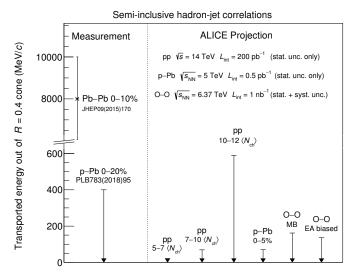

| 110 | Energy loss from recoil jet yield suppression            | 138 |

# List of Tables

| 1  | Requirements for pixel sensor                                                     | 19  |

|----|-----------------------------------------------------------------------------------|-----|

| 2  | SAMPA key parameters                                                              | 27  |

| 3  | Comparison of main detector parameters of the previous ITS1 and the new ITS2      | 33  |

| 4  | Main layout parameters of the new ITS2                                            | 33  |

| 5  | Summary of the ITS2 readout connections and payload capacity                      | 41  |

| 6  | TPC parameters                                                                    | 57  |

| 7  | Geometrical parameters of the new readout chambers                                | 60  |

| 8  | TPC front-end electronics parameters                                              | 63  |

| 9  | TRD tracklet data format                                                          | 83  |

| 10 | FLP readout farm used to transfer the data from the detectors to the $O^2$ system | 114 |

### 1 Introduction

A Large Ion Collider Experiment (ALICE) was proposed, conceived, and built to study the properties of the quark–gluon plasma (QGP) in heavy-ion collisions at the Large Hadron Collider (LHC) at CERN [1]. The design was driven by the requirement to reconstruct tracks at high multiplicity in central Pb–Pb collisions and to provide particle identification over a wide range in transverse momentum ( $p_T$ ). In LHC Runs 1 and 2, the ALICE 1 apparatus was used to record and analyse hadronic collisions ranging from pp to Pb–Pb [2]. The measurements have provided new insights in the properties of the quark–gluon plasma as well as several other aspects of the strong interaction. A comprehensive review of this scientific output was reported in Ref. [3]. During the Long Shutdown 2 (2019 – 2021), major upgrades have led to the new experimental setup, ALICE 2, extending the physics capabilities of the experiment for Runs 3 and 4.

#### 1.1 Motivation

The main objectives of the upgrades in Long Shutdown 2 (LS2) are to significantly improve the capabilities of ALICE to probe the QGP with heavy-flavour quarks, and to enable completely new measurements of the thermal emission of dielectron pairs. In addition, the upgrades significantly improve the precision of measurements in several other areas, such as jet quenching phenomena probing the interactions of high-energy partons, the production of light nuclei, momentum correlations of hadrons to determine the interaction potentials of unstable particles, and the study of collective effects in collisions of protons with high multiplicity. To gain access to these areas of physics a two-fold approach was taken by improving the pointing resolution and increasing the readout rate capabilities of the entire system to collect larger data samples. A thinner and lighter inner tracker with the first layer closer to the interaction point improves the pointing resolution by a factor of 3 in the transverse direction and a factor 6 in the longitudinal direction. This provides more effective suppression of backgrounds in the reconstruction of decays of heavy-flavour mesons and baryons as well as in the dielectron emission measurements. The increase of the readout rate from below 1 kHz to 50 kHz for Pb-Pb collisions leads to improved statistical precision for all measurements, even in the presence of large backgrounds. The improvements in pointing resolution and readout rate will also enable the measurement of thermal dilepton production in Pb-Pb collisions, as well as a number of new measurements of heavy-flavour production, which were out of reach of the ALICE detector in Runs 1 and 2.

#### 1.2 Experimental setup

The experimental setup consists of a central barrel contained in a solenoidal magnet (B = 0.5 T) and a forward muon system with a dipole magnet providing a total bending power of 3 T m, see Fig. 1. The central barrel detector system is designed for efficient tracking in the high track-density environment of heavy-ion collisions, covering transverse momenta from  $\sim 100 \text{ MeV}/c$  to  $\sim 100 \text{ GeV}/c$  with excellent hadron and electron identification capabilities.

Until the end of Run 2, the Inner Tracking System (ITS) which is crucial for the extrapolation of tracks to the primary vertex, consisted of two layers of Silicon Pixel Detectors (SPD), two layers of Silicon Drift Detectors (SDD), and two layers of Silicon Strip Detectors (SSD) [1]. The readout rate of the full ITS was limited to 1 kHz. The ITS was replaced with a new detector (ITS2), based on seven layers of ALPIDE monolithic active pixel sensors (MAPS), which provides better pointing resolution thanks to its reduced distance to the interaction point and better position resolution. It is also able to handle the hit densities resulting from Pb–Pb collisions at 50 kHz interaction rate.

In the radial direction, the ITS is followed by the Time Projection Chamber (TPC) extending from 0.85 m to 2.5 m in radius over a length of 5 m. With the multiwire proportional chambers used in ALICE 1, the ion backflow into the drift region had to be suppressed by active gating, which in turn limited the readout rate to about 700 Hz for Pb–Pb collisions. This limitation is removed in the upgraded TPC by

Figure 1: ALICE 2 detector systems (see legend and text for details).

employing readout chambers based on Gas Electron Multiplier (GEM) foils that reduce the ion backflow and resulting space charge in the TPC to a level that can be corrected for while operating the detector with Pb–Pb interaction rates up to 50 kHz.

The Transition Radiation Detector (TRD) (extending from 2.8 m to 3.5 m in radius) provides additional space points for tracking, which are also used to determine the size of the distortions due to space charge effects in the TPC, as well as dE/dx measurements for particle identification, and the detection of transition radiation for electron identification. The readout electronics were upgraded to minimise the data volume and to reduce the dead time to allow data taking at high interaction rates.

The subsequent Time-of-Flight detector (TOF) allows the identification of hadrons over a wide momentum range and electrons at low momentum. Besides consolidation work on the front-end electronics, the readout was upgraded to handle the increased interaction rates.

A large part of the acceptance in the central barrel is covered by electromagnetic calorimeters. The ElectroMagnetic Calorimeter (EMCal) is realised as Pb-scintillator sampling calorimeters with avalanche photon detector (APD) readout, whereas the PHOton Spectrometer (PHOS) uses PbWO<sub>4</sub> crystals with APD readout. All calorimeters have undergone maintenance and improvements of the readout electronics.

The High Momentum Particle Identification Detector (HMPID) is a ring-imaging Cherenkov detector that adds hadron identification capabilities at large transverse momenta over a limited acceptance. A part of the system was equipped with additional absorbers to facilitate a measurement of the interaction cross section of light antinuclei. Also here, the readout electronics were upgraded to improve the rate capability.

The muon detectors cover the forward pseudorapidity range  $-4.0 < \eta < -2.5$  and use a system of absorbers to remove hadrons and identify muons. The background of secondary muons from pion and

kaon decays in the muon system is small at high  $p_{\rm T}$ , thanks to the so-called 'muon plug' absorber, which is placed at z = 90 cm from the interaction point. The main muon detector stations use multiwire proportional chambers (muon tracking chambers, MCH), and resistive plate chambers (muon identifier, MID), both of which were equipped with new front-end electronics. Following Run 2, and as a new addition to the muon detectors in ALICE 2, the Muon Forward Tracker (MFT) consists of tracking stations with the ALPIDE silicon pixel sensors that are installed in front of the muon plug to improve mass resolution and pointing resolution for the detection of secondary charmonia and muons from B-meson decays.

A set of forward detectors form a Fast Interaction Trigger (FIT), which is used for triggering, event selection and determination of the collision time. The FIT system consists of two arrays of fast Cherenkov radiators placed on both sides of the interaction point (FT0), complemented with 3 sets of scintillator detectors. The interaction trigger is provided by the FT0 together with a large azimuthally segmented scintillator detector placed on the opposite side of the muon detectors, which is also used to determine the reaction-plane orientation in Pb–Pb collisions. Two additional scintillator detectors, FDD, are placed on opposite sides of the interaction point at large distances to cover  $4.7 < \eta < 6.3$  and  $-6.9 < \eta < -4.9$ to select diffractive and ultra-peripheral collisions with rapidity gaps. The FIT detector replaces the T0, V0 and AD detectors, which had similar functionalities in ALICE 1 [1].

The Zero-Degree Calorimeters (ZDC) are installed at  $\approx 100$  m on either side of the interaction point to help determine the centrality and event plane orientation. The readout electronics of the ZDC were upgraded to increase the readout rate to match the rest of the system.

In addition to the interventions outlined here, significant consolidation work has been performed on several subsystems which are described in the sections on individual detector systems below.

Furthermore, the readout infrastructure was completely renewed to support the continuous readout of the core detectors. The raw data from the detectors are mostly transmitted through optical links and received by First Level Processors (FLPs), where the data are assembled to time frames for further processing. A dedicated farm of Event Processing Nodes (EPN) was installed at the experiment site for the online reconstruction of all collisions. The output of this synchronous reconstruction is stored on mass storage systems and is used for an asynchronous reconstruction stage with improved calibration. The output of the latter is then used for physics analysis. A new common software framework, O<sup>2</sup>, was developed for online and offline reconstruction as well as the physics analysis.

#### 1.3 Data samples

During LHC Runs 1 and 2, data were recorded with pp, p–Pb, Xe–Xe, and Pb–Pb collisions at a variety of collision energies. The collision and readout rates were tuned to limit pile-up in pp collisions and to keep the total space charge generated in the gas amplification in the TPC readout chambers to manageable levels. Typical collision rates were up to 8 kHz for Pb–Pb collisions and around 200 kHz for pp collisions. To make optimal use of the different readout rate capabilities across the detector systems, clusters of detectors were read out at different rates. The central barrel detectors were read out at a rate of 500 Hz to 600 Hz, while the cluster with the forward muon detectors together with V0, T0 and the silicon pixel layers for event characterisation were read out at a slightly higher rate. For specific triggers, such as coincidence triggers between the forward muon detectors and the calorimeters in the central barrel, the full detector was read out. During pp and p–Pb data taking a 'fast cluster' containing all barrel detectors except the SDD was used in order to double the effective TPC readout rate. Figure 2 shows the luminosities accumulated during Run 2 with different trigger conditions.

For Runs 3 and 4, it is planned to record pp and Pb–Pb data at interaction rates of 0.5 MHz to 1 MHz and 50 kHz, respectively. This will allow us to inspect integrated luminosities of  $200 \text{ pb}^{-1}$  and  $13 \text{ nb}^{-1}$ , respectively.

**Figure 2:** Accumulation of integrated luminosity over time for different trigger types in pp (left) and Pb–Pb (right) collisions during LHC Run 2.

#### 1.4 Outline

In this article, the upgrades made to ALICE during the LHC Long Shutdown 2 are discussed. The next Chapter 2 presents the readout system design, the common readout unit and the integrated circuits (ASICs), that were conceived, designed and produced for the upgrades of multiple detector systems. Chapter 3 presents the upgrades of the inidividual detector systems in detail. Chapter 4 details the mechanical integration of the detector components within ALICE and the interfaces with the LHC. In Chapter 5 the trigger system, the readout chain, as well as the synchronous and asynchronous processing stages are discussed. The expected performance of the upgraded detector and reconstruction is reported in Chapter 6. Chapter 7 comproses of a conclusion with prospects for the LHC Run 3 and a brief outlook on the future ALICE upgrade plans.

#### 2 System design and common developments

A series of developments have been pursued commonly for multiple systems. Foremost, the readout chain was redesigned for all detectors (Sec. 2.1). A common readout unit was developed for the readout of the detectors (Sec. 2.2). The ALICE Pixel Detector (ALPIDE) chip is designed and used for both the inner tracking system and the muon forward tracker (Sec. 2.3). The SAMPA is used as front-end chip for the time projection chamber and the muon systems (Sec. 2.4).

#### 2.1 System design

In nominal operating conditions (50 kHz interaction rate for Pb–Pb) each TPC drift time period of  $\sim 100 \,\mu s$  will contain on average 5 Pb–Pb events. It was therefore decided to use a continuous, untriggered readout strategy, combined with online data compression for the upgraded readout and data acquisition system.

In order to synchronise the continuous data stream across all readout and processing branches, the data stream is divided in so-called time frames (TF) of a nominal length of 128 LHC orbits ( $\sim$ 11 ms). Each TF is subdivided in heartbeat frames (HBF) with a length corresponding to an orbit of  $\sim$ 89.4 µs. Figure 3 illustrates this structure. For commissioning and calibration runs, for which the data throughput exceeds nominal conditions, all detectors also support triggered mode, in which only data from selected interactions are retained by the readout electronics. In addition, a subset of legacy detectors has not been upgraded to continuous readout and will operate in triggered mode only. For these detectors, as well as for dedicated runs, minimum bias triggers based on the fast interaction trigger detector (FIT) and the PHOS, EMCAL and TOF are distributed. In both the continuous and triggered readout mode, the detector data are time stamped with a precision of an LHC bunch crossing of 25 ns; data belonging to a HBF are grouped together into HBF packets.

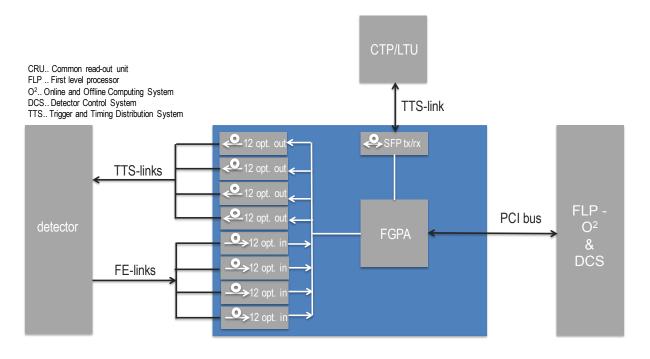

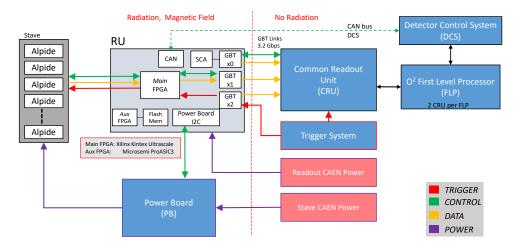

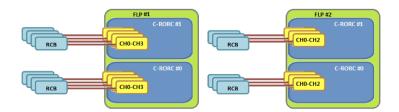

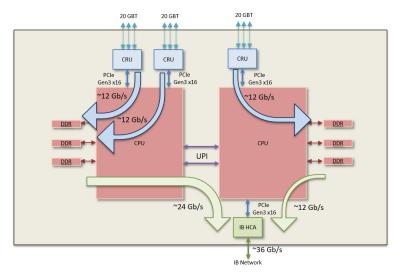

The upgraded ALICE system architecture is shown in Fig. 4. The Common Readout Units (CRU) are standardised PCIe FPGA-based optical I/O processor modules used by all upgraded detectors for data readout and configuration, see Sec. 2.2. Data taking is governed by the Central Trigger System (CTS) which distributes timing and trigger signals. The CTS features a two-staged distribution system consisting of one central trigger processor (CTP) and up to 18 active distribution units, the local trigger units (LTU), one for each subdetector. The CTP-LTU and LTU-CRU connections are implemented using bidirectional TTC-PON links [4, 5]. The standard timing and trigger signal distribution path goes from the CTS via the detector-specific CRUs to the detector front-ends via bidirectional radiation tolerant GBT links [6]. Trigger signals are distributed with three different latencies referred to as LM (level -1 at 425 ns), L0 (level 0 at 1200 ns), and L1 (level 1 at 6100 ns). Detectors that require latency-critical trigger signals receive them additionally on a direct path from the CTS, which is located in the cavern, to the detector front-ends on GBT links. A second group of detectors do not support continuous readout and require a trigger signal indicating the presence of an interaction with a latency of 1.6 µs. Some detectors continue to be read out via legacy readout cards (C-RORC [7]) following a hardware trigger signal to initiate the readout. They receive the clock and trigger signals via the legacy TTC system [4, 5]. For more details on the CTS, see Sec. 5.5.

The Online & Offline processing farm  $(O^2)$  contains the first level processors (FLP) and event processing nodes (EPN). The detector front-ends send the data via GBT-based links to the CRUs and C-RORCs located in the FLPs. Depending on the detector implementation, the readout data are reformatted or compressed either in the front-ends, the CRUs, or in the FLPs. The FLPs prepare Sub-Time Frames (STF) by merging all HBFs of one TF of the connected detector. Note that for most detectors the data is distributed over several FLPs. The FLPs ship the STFs of all subdetectors via a network to the EPN farm where they are merged into TFs. In order to compress the data to be stored, the O<sup>2</sup> system performs a first synchronous online reconstruction pass, converts the data into compressed time frames (CTF) and

**Figure 3:** Time frame and heartbeat frame structure in continuous and triggered mode. HeartBeat (HB) triggers are issued in continuous and triggered modes to all upgraded detectors. Physics triggers can be sent to upgraded detectors in triggered mode and are sent to non-upgraded detectors in all modes. HBF and TF rates are programmable with the following nominal values; HBF: 1 every orbit, ~89.4  $\mu$ s/~10 kHz, TF: 1 TF every 128 HBFs/~11 ms/~100 Hz.

sends them to the storage system from where it is accessed asynchronously for further processing. In total, a raw data throughput of 3.4 TB/s is processed in a continuous manner by the readout system. After zero suppression and data compression in the front-ends, the CRUs, and the FLPs, a data throughput of 635 GB/s is processed by the data network and the EPN farm.

The detectors are configured via the detector control system (DCS) which is connected to the detector front-ends via the CRU. The experiment control system (ECS) governs the entire data taking process via direct network connections to the central systems (DCS, CTS, FLP, EPN).

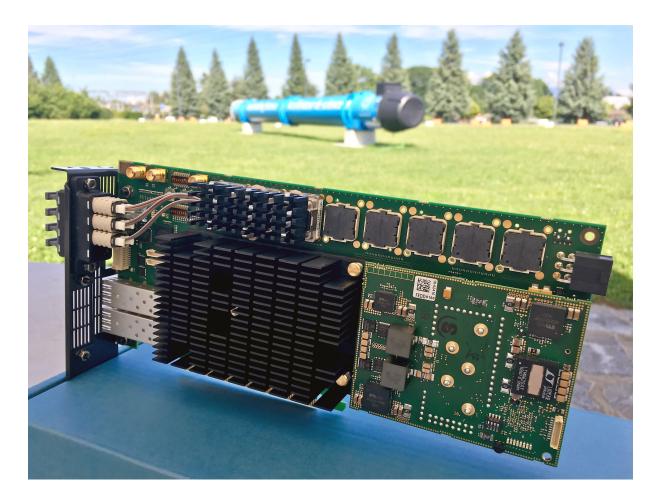

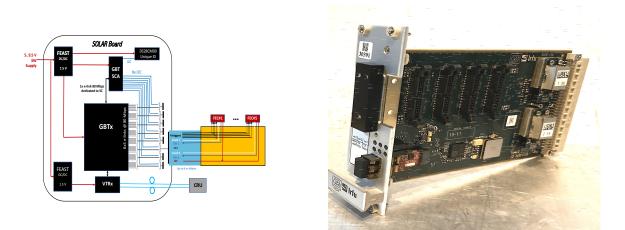

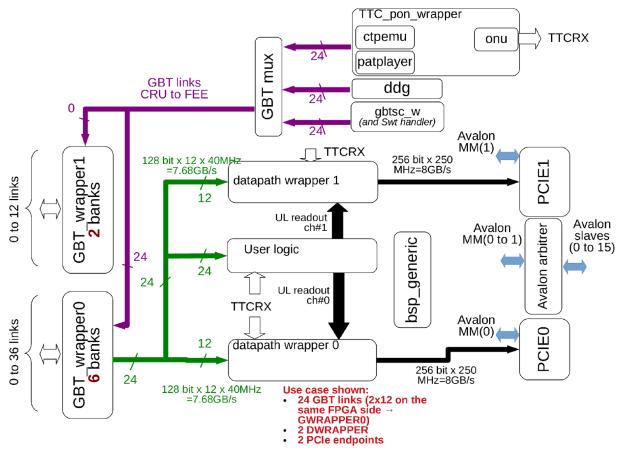

#### 2.2 Common readout unit

For all upgraded detectors the Common Readout Unit (CRU) serves as interface between detector frontend links, the O<sup>2</sup> FLP processors, the CTS and DCS. The CRUs are custom developed FPGA-based Gen 3 PCI Express plug-in cards installed in the FLPs. The card (named PCI40) was originally developed for LHCb [8] and has requirements fully compatible with ALICE. ALICE adopted the PCI40 for its CRU and joined the qualification and test effort and has developed firmware for use in the experiment.

The CRU hardware features up to 48 high-speed, bidirectional, 10 Gb/s optical links using 12-lane Minipod parallel optical transmitters (AFBR-812 and AFBR-822) and receivers from Avago/Broadcom. They are accessible from the CRU front-panel through MTP (Multi-Fiber Termination Push-on) optical ribbon cable connectors and establish the interface to the detector front-end electronics using the GBT protocol [6] implemented in the FPGA. GBT links are the result of a common development for all LHC experiments to provide a radiation tolerant transmission chip (GBTx, SCA) and optical transceiver set (VTTx, VTRx) to be used on the detector front-end cards communicating with the data aquisitioning and detector control systems via optical links. The GBTx provides a data bandwidth of 4.48 Gb/s in wide-bus mode, or 3.2 Gb/s in GBT mode depending on whether forward error correction with superior correction capability for radiation induced transmission errors is activated. The slow control adapter ASIC (SCA) is an auxiliary chip compatible with the GBTx. Connected to a GBTx it allows the control of ADCs and

Figure 4: ALICE readout and control system architecture.

digital IOs. VTTx and VTRx are radiation tolerant dual optical transmitter and transceiver components compatible with the GBTx ASIC.

The number of data links used for each CRU and the use of the forward error correction are adapted to the subdetector needs. In most detector implementations, 24 data links are connected to one CRU. Table 10 in Sec. 5.2 shows the number of CRUs, the number of readout links and the data throughput into and out of one CRU for each subdetector.

For the GBT downlink to the detector-front ends carrying the timing and trigger signals as well as the configuration data up to 320 Mb/s are available from the GBTx ASIC on a configurable number of pins. The single word transmission protocol (SWT) has been developed to provide the front-end designers with a common configuration data framework.

One of the two CRU SFP+ optical transceivers is used to connect the CRUs to the CTS system via bidirectional TTC-PON [5] links. The TTC-PON link allows the distribution of timing and trigger signals with constant latency from the CTS to the CRU over passive optical splitters with a bandwidth of up to 9.6 Gb/s. The links carry the LHC clock with a jitter below 20 ps (rms) and synchronise all 474 CRUs and the connected detectors to each other. The upstream link from all CRUs to the CTS carry detector buffer status information, see Sec. 5.5.2.

The 16-lane (x16) PCI Express card edge connector provides the interface between the CRU and the ALICE O<sup>2</sup> FLPs, in which up to 3 CRUs are installed. The interface achieves  $\sim$ 90 Gb/s sustainable data throughput from the CRU to the memory of the FLP computers [9]. Depending on subdetector implementation, the CRU FPGA forwards data that has already been formatted and compressed in the detector front-end, or performs detector-specific formatting, compression and base line reconstruction. In both cases, the data stream to the FLP consists of data packets compatible with the HBF structure (see Sec. 2.1). A central FPGA firmware framework provides the interfaces to CTS, FLP, CRU and the subdetectors. Subdetector-dependent functionality, such as link decoding, adding HBF structure, compression or data processing is added via a dedicated user logic (UL) firmware plug-in to the central FPGA firmware. A detailed description of the CRU firmware design can be found in [9].

Figure 5 shows the block diagram of the module functionality and Fig. 6 shows a photograph of the CRU card.

#### 2.3 The ALPIDE Chip

#### 2.3.1 Technology, Sensing, Pixels

The ALPIDE chip [10] is a Monolithic Active Pixel Sensor (MAPS) [11] implemented in a 180 nm CMOS technology for imaging sensors provided by TowerJazz (Tower Semiconductor since March 2022) [12]. It was designed for the upgrade of the Inner Tracking System (ITS2) to meet the requirements summarized in Table 1.

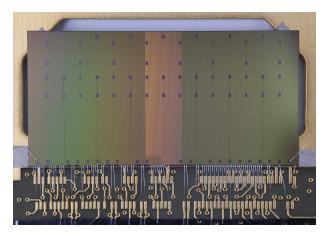

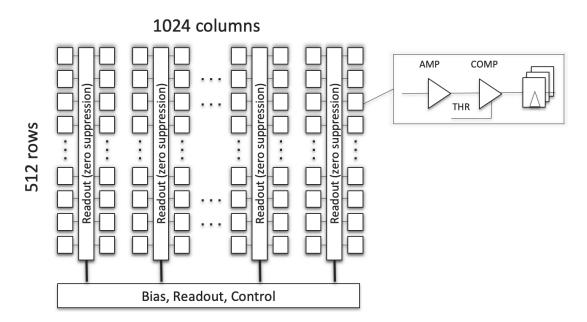

The ALPIDE chip (Fig. 7) measures 15 mm by 30 mm and includes a matrix of  $512 \times 1024$  sensing pixels, each one measuring  $29.24 \mu m \times 26.88 \mu m (z \times r\varphi)$ . Analog biasing, control, readout and interfacing functionalities are implemented in a peripheral region of  $1.2 \times 30 \text{ mm}^2$  (Fig. 9).

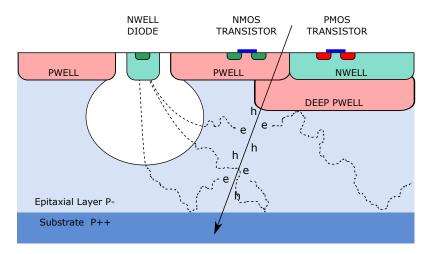

The ALPIDE chips are fabricated on substrates with a high-resistivity (> 1 k $\Omega \cdot cm$ ) epitaxial layer on p-type substrate. Typical values for the thickness of the epitaxial layer are in the range between 18 and 30 µm. Figure 8 illustrates that a charged particle crossing the sensor liberates charge carriers in the material. The electrons released in the epitaxial layer can diffuse laterally while they remain vertically confined by potential barriers at the interfaces with the overlying p-wells and the underlying p-type substrate. The signal sensing elements are n-well diodes (~2 µm diameter). Their area is typically 100 times smaller than the pixel cell area. The electrons that reach the depletion volume of a diode (or carriers that are released directly inside it) induce a current signal at the input of the pixel front-end.

**Figure 5:** Block diagram of the common readout unit (CRU): the CRU forms the interface between the first-level processors (via PCIe), the central trigger system (via TTS), and the detectors (via TTS and FE).

| Parameter                                                     | Inner Barrel             | Outer Barrel       |

|---------------------------------------------------------------|--------------------------|--------------------|

| Chip dimensions [mm × mm]                                     |                          | × 30               |

| Silicon thickness [µm]                                        | 50                       | 100                |

| Spatial resolution [µm]                                       | 5                        | 10(5)              |

| Detection efficiency                                          | > 99%                    |                    |

| Fake-hit probability [evt <sup>-1</sup> pixel <sup>-1</sup> ] | $< 10^{-6} (<< 10^{-6})$ |                    |

| Integration time [µs]                                         | < 30 (10)                |                    |

| Power density $[mW/cm^2]$                                     | $< 300 \ (\sim 35)$      | $< 100 (\sim 20)$  |

| TID radiation hardness <sup>*</sup> [krad]                    | 270                      | 10                 |

| NIEL radiation hardness <sup>*</sup> [1 MeV $n_{eq}/cm^2$ ]   | $1.7 	imes 10^{12}$      | $1 \times 10^{11}$ |

| Readout rate, Pb–Pb interactions [kHz]                        | 10                       | 00                 |

**Table 1:** General requirements for the pixel sensor chip for the upgrade of the ALICE inner tracking system. In cases where the actual ALPIDE performance is significantly better than the requirements, the actual performance is indicated in parenthesis and italics. (\*) Radiation load integrated over 6 years of operation.

The manufacturing process also provides a deep p-well layer that can be used to shield the epitaxial layer from the n-wells of the pmos transistors. These would otherwise compete with the sensing diodes in collecting the electrons, strongly impairing the charge collection. This feature permits the use of full CMOS circuits, including pmos transistors, in the active area.

A reverse bias voltage can be applied to the substrate. This increases the depletion volume around the n-well collection diodes and reduces the capacitance of the input junction. All these aspects contribute to increasing the S/N ratio.

#### 2.3.2 Analog Front-End and Discriminator

Each pixel cell contains a sensing diode, a front-end amplifier and a shaping stage, a discriminator and a digital section (see the insert in Fig. 9). The digital section includes a multi-event buffer with three hit storage registers and a pixel mask register.

**Figure 6:** Picture of a CRU; bottom left, FPGA cooling radiator, bottom right, power mezzanine; top row; 3 out of 8 Minipods installed; top left, fiber optics cable to MPO connector on front panel; bottom left, SFP transceivers.

Figure 7: Photograph of the ALPIDE chip on a test carrier.

Figure 8: Schematic cross-section of a pixel cell.

Figure 9: Architecture of the ALPIDE chip.

In every pixel, there is a pulse injection capacitor for injection of test charge into the input of the frontend. A digital-only pulsing mode is also available, directly forcing the setting of the in-pixel memory cells, substituting the latching of a discriminated pulse. The analog and digital pulsing patterns are fully programmable. These features are used routinely for testing and calibration.

The front-end and the discriminator are continuously active. They feature a non-linear response and their transistors are biased in weak inversion. The total power consumption of the pixel cell is 40 nW. The small signal gain of the front-end is 4 mV/e, the equivalent noise charge is 3.9 e, while the minimum threshold is below 100 e. The typical value of the capacitance of the sensing diode is 2.5 fF. The input capacitance of the front-end is below 2 fF. The output of the front-end has a peaking time of the order of  $2 \mu s$ , while the discriminated pulse has a typical duration of  $5 \mu s$  to  $6 \mu s$ . The front-end and the discriminator act as an analogue delay line. This allows operating the chip in triggered mode when, as it happens in ALICE, the latency of the incoming trigger is comparable with the peaking time of the front-end. A common threshold level is applied to all the pixels.

The latching of the discriminated hits in the storage registers is controlled by global STROBE signals. A pixel hit is stored into one of three in-pixel latch cells if a STROBE pulse is applied to the pixel while the output of the front-end is above threshold. The generation of the internal STROBE signals can be either triggered by an external command or optionally initiated by an internal sequencer. The duration of the STROBE pulses is programmable. Two major operating modes are supported. In triggered mode the STROBE and the frame readout are triggered externally from an event synchronous command. In continuous mode the strobe is asserted periodically and for a duration almost equal to the period. The event frames are continuously integrated and read out.

#### 2.3.3 Matrix and Readout

The readout of the frame data from the matrix is zero-suppressed and is executed by an array of circuits named *priority encoders* (Fig. 9). The priority encoder provides to the periphery the address of the first pixel with a hit in its double column, selecting it according to a hardwired topological priority.

During one hit transfer cycle a pixel with a hit is selected, its address is encoded and transferred to the periphery and finally the in-pixel memory element is reset. The address of the next pixel with a hit in the double column is then calculated. This cycle is repeated until the addresses of all pixels initially presenting a valid hit at the inputs of a priority encoder have been transferred to the periphery and all the hit storage registers in the double column have been reset.

Each priority encoder is a fully combinatorial circuit and it is steered by sequential logic in the periphery during the readout of a matrix frame. It is implemented in a very narrow region between the pixels, extending vertically over the full height of the columns. There is no free running clock distributed in the matrix and there is no signaling activity if there are no hits to read out. The average energy needed to encode the address of a hit pixel is of the order of 100 pJ. Power is consumed proportionally to the readout rate and to the average hit occupancy of the frames. The readout of the matrix consumes around 3 mW under normal conditions. The priority encoders also implement the buffering and distribution of readout and configuration signals to the pixels.

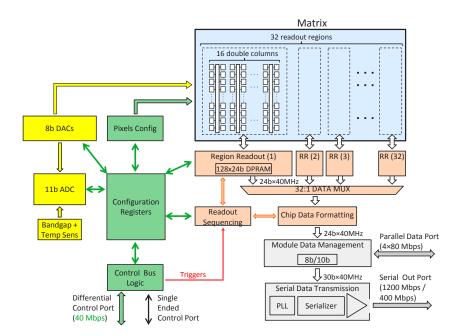

The 512 double columns and the corresponding priority encoders are functionally grouped in 32 regions  $(512 \times 32 \text{ pixels})$ , each of them with 16 double columns being read out by 16 priority encoder circuits (Fig. 10). There are 32 corresponding region readout units in the chip periphery, each one executing the readout of a region. They steer the priority encoders, latch the encoded pixel hit address, perform additional data reduction and formatting and buffer the hit data into memories. The 16 double columns inside each region are read out sequentially, while the 32 regions are read out in parallel. The data from the 32 region readout units are assembled and formatted by a top readout unit module.

Data can be transmitted on two different readout ports. The largest capacity data readout interface is a

Figure 10: Block diagram of the ALPIDE chip.

1.2 Gb/s serial data port with differential signaling. The serial transmission is 8b/10b encoded, therefore the maximum data throughput is 960 Mb/s. The serial port can optionally operate at reduced line rates (600 Mb/s or 400 Mb/s). A bidirectional parallel data port with single-ended signaling is also available, with a capacity of 320 Mb/s. This port enables the implementation of an inter-chip data transfer and relaying protocol designed to integrate multi-chip modules without additional external devices. This is used in the modules of the ITS2 outer barrel.

The ALPIDE chip has custom control interfaces. There are a differential control port supporting bidirectional (half duplex) serial signaling at 40 Mb/s on differential links and a second single ended control port. The two control interfaces and the dedicated internal logic allow interconnecting multiple chips on a module and control them via the differential interface of only one of the chips acting as hub of the control bus. The control bus is also used to distribute broadcast commands and synchronization messages to the chips, most notably the trigger commands.

The periphery of the chip contains fourteen 8-bit analog DACs for the biasing of the pixel front-ends. The analog section of the periphery also contains a band-gap reference and a temperature sensing circuit. An ADC with 11 bit resolution is available for monitoring and testing purposes, and can probe the outputs of the DACs, the analog as well as digital supply voltages, the band-gap voltage and the temperature sensor.

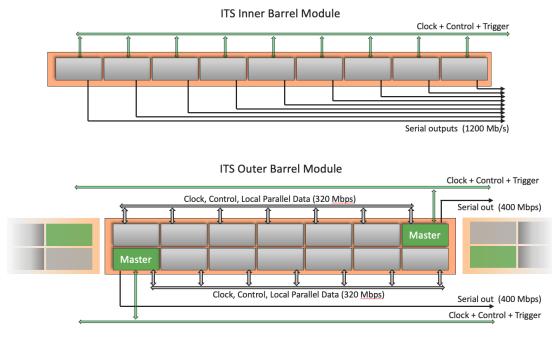

#### 2.3.4 Features for integration of ITS2 modules

The ALPIDE chip has specific design features to enable the integration of multi-chip detector modules, to minimise the electrical wiring between modules and off-detector electronics and to provide common interfaces across the ITS2 staves. Two different hybrid modules built with ALPIDE sensors are used in the upgraded ALICE ITS2 (Fig. 11): one in the three innermost layers constituting the inner barrel and the other in the staves of the remaining layers of the outer barrel (see also Sec. 3.2.1).

The ITS2 inner barrel module includes nine ALPIDE chips. They share a common differential control and clock distribution buses. Each chip transmits its own data off-detector at maximum line rate (1.2 Gb/s) on point-to-point high speed serial links.

The ITS2 outer barrel module contains fourteen chips, arranged in two subgroups of seven. One chip in each group, called *master*, acts as control hub and data relaying chip. Only the master chips communi-

Figure 11: Diagrams of the ITS2 inner barrel and outer barrel modules.

cate with the external electronics through differential clock and control busses shared between multiple modules and through point-to-point differential wire-line links for the transmission of data.

Each of the master chips connects to six neighbouring chips, forwards them to the main clock and bridges the control transactions on electrical interconnects that are local to the modules.

The chips neighbouring the master use a shared parallel local bus to transfer their data to the master. The master chip relays the data from the slave chips on the serial output port driving the point-to-point links. In this configuration the master chips transmit data on the serial data port using a lower bit rate (400 Mb/s).

Grouping of data from neighbouring chips and transmitting at lower rate are possible in the ITS2 outer barrel layers given the lower occupancy. In addition to reducing the total number of copper links, this scheme achieves a significant reduction of the power consumption given that only one out of seven line drivers is maintained active.

Differential copper wire lines directly connect the ALPIDE chips to the off-detector electronics. These links reach a length of 8 m. The electrical receivers and transmitters on the ALPIDE chips were designed and tailored to the electrical and protocol levels to operate with these long interconnects.

#### 2.3.5 Power consumption

The ALPIDE sensor chip has three power supplies: one analog domain, one digital domain and a power supply dedicated to the Phase-Locked Loop (PLL) of the high speed serial data transmitter. The power consumption of the analog section, dominated by the analog front-ends, is typically 24 mW. The digital power consumption includes the pixel digital sections, readout modules, peripheral circuits, and I/Os. It depends strongly on the configuration and operating conditions. In the nominal conditions of the ALICE ITS2, it is about 130 mW.

The output serial links are driven by a data transmission unit including a PLL, a fast serializer and a line driver stage with a typical power consumption of about 52 mW. The data transmission unit is enabled in all the chips of the ITS2 inner barrel. In the outer barrel modules it is active only in the master chips and

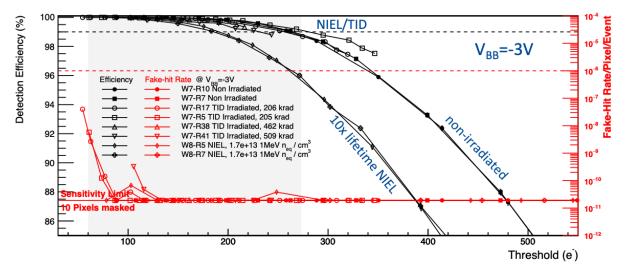

**Figure 12:** ALPIDE sensor chip detection efficiency and fake-hit rate vs global threshold setting. Beam test results (6 GeV/*c* pions, orthogonal incidence). ALPIDE substrate reverse bias: -3 V.

disabled in the remaining chips, that is only 1 out of 7 sensors consumes this extra power.

The power dissipation density is about  $47 \text{ mW/cm}^2$  in the ITS2 inner barrel modules and around  $35 \text{ mW/cm}^2$  in the outer barrel modules.

The readout of the matrix and the digital periphery consume power in proportion to the clocking frequency, the readout rate and the pixel occupancy. In less demanding applications not requiring the high speed links and the full rate capabilities, the power consumption can be reduced considerably with various techniques including slowing down or suspending the primary clock and using the single ended I/Os to read out data at low rates.

#### 2.3.6 Results from the experimental characterization in laboratory and beam tests

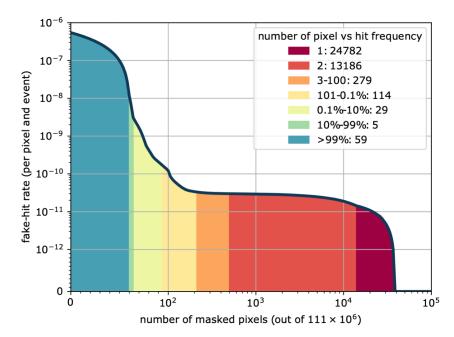

The ALPIDE chip and its prototype predecessors have been characterised with an extensive test program including laboratory tests and a series of beam tests. A summary of key results is given in this section. The full set of results and details on the methodologies will be presented in a separate paper.

The laboratory measurements were based on the sensible usage of the built-in test pulse charge injection circuitry and on the systematic analysis of threshold scans and noise measurements. These allowed thorough characterisation the distributions of pixel thresholds, the fractions of pixels requiring masking, and the residual fake-hit rate after masking. Their dependencies on operating conditions were accurately established.

A set of ALPIDE prototype sensors were characterised in beam tests to quantify detection performance and hit-position resolution. The samples under test were located at the center of beam telescopes acting as precision trackers. The telescopes were themselves constructed with ALPIDE sensors and had six detection planes: three upstream and three downstream of the Device Under Test (DUT). The measurements were based on reconstructing particle tracks in the telescope and projecting them onto the DUT plane. The presence of a matching cluster, its size in pixels and its centroid were the basis for measuring the detection efficiency and the hit-position resolution.

Figure 12 provides a summary of the beam test results on the detection efficiency and the fake-hit rate as a function of the global threshold setting. Data of eight different samples are shown, including two non-irradiated DUTs and pairs of devices exposed to increasing doses of ionising radiation before the tests. The samples exposed to the TID level of 200 krad (75% of the lifetime dose) received also a combined Non-Ionising Energy Loss (NIEL) fluence at a level corresponding to 1.3 times the fluence expected over

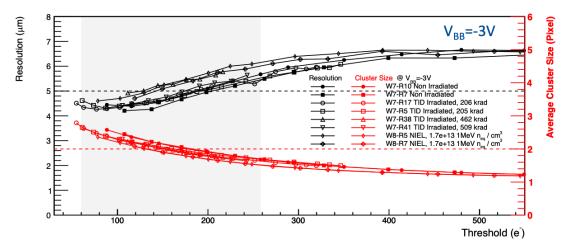

**Figure 13:** ALPIDE chip hit-position resolution and average cluster size as a function of global threshold setting. Beam test results with 6 GeV/c pions with perpendicular incidence. ALPIDE substrate reverse bias: -3 V.

the total lifetime. The Total Ionising Dose (TID) level of 500 krad (190% of the lifetime dose) includes a combined fluence that is 3.2 times the lifetime fluence. Two devices were also irradiated with neutrons for a cumulated non-ionizing energy loss of  $1.7 \times 10^{13}$  [1 MeV  $n_{eq}/cm^2$ ], corresponding to ten times the fluence expected over the full detector lifetime.

The results show a large operating margin for the threshold setting between 50 and 250 electrons, providing a detection efficiency above 99% and a fake-hit rate that is several orders of magnitude smaller than the required value of  $10^{-6}$  fake-hit probability per pixel per frame. The ALPIDE sensor proved to be extremely well performing in terms of noise. Masking the ten most noisy pixels out of the 524288 in the matrix (less than 0.002%) resulted in a residual fake-hit noise level below the sensitivity of these experiments ( $2 \times 10^{-11}$ ).

Figure 13 shows the beam test results on the hit-position resolution (black markers and lines, upper band) and the average cluster size (red markers and lines, lower band) as a function of the global threshold. The data sets refer to the same samples of Fig. 12. The hit-position resolution is better than  $6 \mu m$  for thresholds below 300 electrons and better than  $5 \mu m$  for a threshold below 140 electrons. As expected the average cluster size depends on the threshold setting, due to the cutting on shared charge diffusing into pixels adjacent to the seed pixel. It ranged between 1.5 and 2.5 pixel hits in the range of interest.

The tests also showed that the chip-to-chip performance variations were negligible, that the chips with combined TID and NIEL irradiation performed similarly to the non-irradiated chips and that sufficient operational margin was present also in the samples with a NIEL dose ten times larger than the one expected over the lifetime.

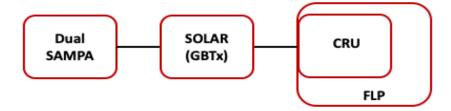

#### 2.4 SAMPA

The SAMPA [13] is a 32-channel custom front-end ASIC for the readout of gaseous detectors and specifically for the ALICE Muon Chambers (MCH, Sec. 3.6.1) and Time Projection Chamber (TPC, Sec. 3.4). Each of the 32 channels contains a Charge Sensitive Amplifier (CSA) and a 10-bit 20 MSample/s ADC. The digitised data of all 32 channels is made available on serial links as either a raw data stream or preprocessed by an internal Digital Signal Processor (DSP), supporting both the continuous and triggered readout of the upgraded ALICE system. The SLVS serial output links support 320 Mb/s and are compatible with the input links (e-links) on the serial transceiver ASIC (GBTx) of the GBT-links used in ALICE for data transmission between the detectors and the CRUs. Depending on the data transfer rate needed in the application, the SAMPA data can be routed via a programmable number of up to 11 serial links.

|                                   | J 1                       |                            |

|-----------------------------------|---------------------------|----------------------------|

| Parameter                         | МСН                       | TPC                        |

| Input polarity                    | pos                       | neg                        |

| Input charge linear range         | 500 fC                    | 100 fC and 67 fC           |

| Sensor capacitance                | 40-80 pF                  | 12-25 pF                   |

| Gain                              | 4 mV/fC                   | 20 mV/fC and 30 mV/fC      |

| Gain channel-to-channel variation | 1.5 %                     | 1.5 %                      |

| Gain linearity                    | 0.5 % up to 85 % of range | 0.5 % up to 85 % of range  |

| Channel-to-channel cross talk     | <0.3 %                    | ${<}0.2\%$                 |

| Noise                             | $2000 e^-$ @ 60 pF        | 600 e <sup>-</sup> @ 12 pF |

| Peaking time                      | 330 ns                    | 170 ns                     |

| Baseline return                   | <550 ms                   | <500 ns                    |

| ADC sampling rate max. 20 MSa/s   | 10 MSa/s                  | 5 MSa/s                    |

| ADC ENOB                          | >9.2                      | >9.2                       |

| ADC INL                           | < 1 LSB (abs.)            | < 1 LSB (abs.)             |

|                                   |                           |                            |

| Table 2: SAMPA key paramete | ble 2: SAMPA key parar | neters. |

|-----------------------------|------------------------|---------|

|-----------------------------|------------------------|---------|

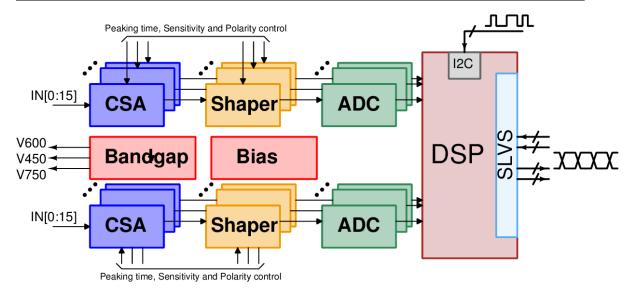

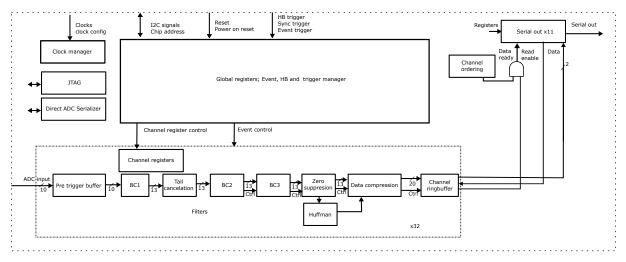

Figure 14: Block diagram of the SAMPA ASIC.

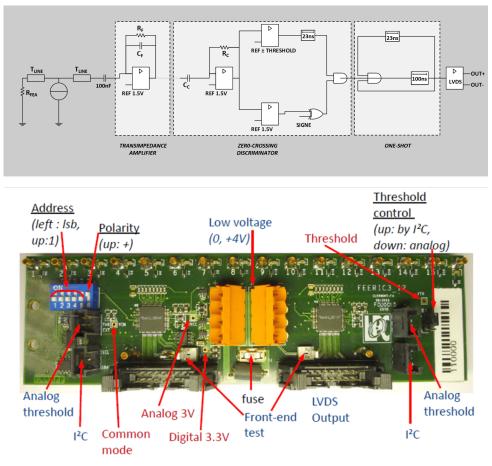

The block diagram of the SAMPA ASIC is shown in Fig. 14. The front-end is composed of a cascade connection of a CSA (Charge Sensitive Amplifier), a differential semi-Gaussian pulse shaper and an Analog-to-Digital Converter (ADC). The CSA and the pulse shaper convert signals into a semi-Gaussian pulse with an amplitude proportional to the total charge injected on the input. SAMPA was designed and fabricated in 130 nm CMOS technology and it operates at a nominal supply voltage of 1.25 V. In order to adapt the SAMPA to its two applications in the MCH and TPC, the sensitivity, polarity and peaking time of the front-end can be adjusted via external pins. SAMPA supports positive and negative polarity of the input charge and has three different gain modes with different sensitivity and peaking time: 20 mV/fC@160 ns, 30 mV/fC@160 ns for the TPC and 4 mV/fC@300 ns for the MCH. Table 2 summarizes the main characteristics and performance of the SAMPA.

Analog front-end reference voltages (nominal values 450 mV, 600 mV, and 750 mV) are generated internally with temperature compensation and can be adjusted via configuration registers. The ADC requires an external voltage reference of 1.1 V. The DSP eliminates signal perturbations, distortion of the pulse shape, offsets, and signal variations due to changes in the environment. An I2C interface allows setting control registers.

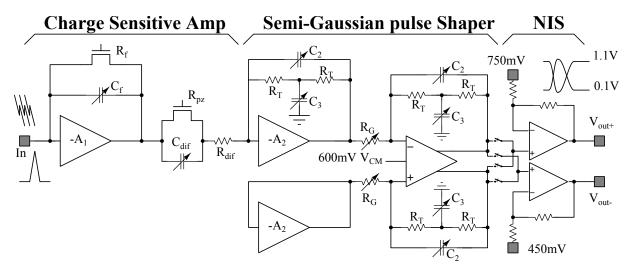

Figure 15: Block diagram of the front-end implemented in the SAMPA ASIC.

#### 2.4.1 CSA and shaper

The SAMPA front-end is composed of a positive/negative polarity CSA with a capacitive feedback  $C_f$  and a resistive feedback  $R_f$  connected in parallel, converting the input charge signal (*Q*) into a voltage step signal proportional to  $Q/C_f$ . The discharge resistor ( $R_f$ ) provides baseline restoration and reduces pile-up effects in the CSA (Fig. 15). A pole-zero cancellation resistor ( $R_{pz}$ ) eliminates the undershoot generated by the long time constant of the output step signal of the CSA. The step signal is fed to a bandpass filter constituted by a first order high-pass filter  $C_{dif}R_{dif}$  (differentiator) and a two bridged-T second order low-pass filters (integrator). After that, a non-inverting stage (NIS) generates a semi-Gaussian output pulse with an amplitude proportional to the input charge. The amplifier of the first shaper is a scaled-down version of the CSA amplifier. In order to provide the second shaper with a differential mode input, a copy of the first shaper is included. This copy is connected in unity gain configuration to minimize its noise contribution. The second shaper consists of a fully differential amplifier with a Miller configuration and a common-mode feedback network. It has the same functionality as the first shaper and implements two other poles and a zero creating a CR-(RC)<sup>4</sup> semi-Gaussian shaper together with the differentiator and the first shaper stage.

The gain of the front-end is controlled by  $R_G$ , which is an array of parallel resistances that are switched by configuration registers. The peaking time of the semi-Gaussian shaper is adjusted for each operation mode (160 ns and 300 ns) by external configuration control of an array of parallel capacitors. These front-end configurations are performed with transmission gates used as low resistance switches.

#### 2.4.2 ADC

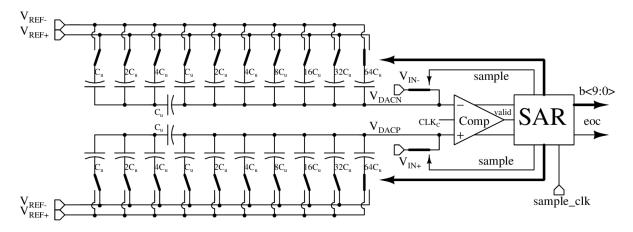

The 32-channel 10-bit SAMPA ADC features a sampling frequency of up to 20 MSa/s defined by an external clock. The MCH and the TPC use the SAMPA with 10 MHz and 5 MHz sampling clock, respectively.

The SAMPA ADC is based on the successive-approximation register (SAR) architecture [14]. It is shown in Fig. 16. A differential capacitive DAC is implemented with the split capacitor topology. Top-plate sampling with MSB (Most Significant Bit) preset to achieve full-range sampling is used. A switching strategy with low energy dissipation per cycle is used.

#### 2.4.3 DSP and readout

**Direct ADC Serialization** In the Direct ADC Serialization (DAS) mode, the SAMPA sends out the unmodified raw data stream from all 32 ADC channels via 11 serial links, bypassing the readout processor

Figure 16: Block diagram of the SAMPA SAR ADC.

and DSP. In this mode, most of the digital circuitry is powered down via clock gating, keeping active only the communication links. 10 SLVS links are used to send the 10-bit data samples of each ADC channel. The 11<sup>th</sup> link is used to provide a synchronisation clock. Optionally, a split mode can be activated, such that data from ADC channels zero to 15 (16 to 31) are transmitted on serial links zero to four (five to nine). This allows connection of an odd number of SAMPAs to an even number of serial transmitters, as in the case of the TPC readout, where five SAMPAs are connected to two GBTx transmitter chips.

**DSP** The SAMPA DSP (Fig.17) implements fully parallel data processing on the 32 channels and supports both continuous and triggered readout operation. When in DSP mode, the data coming from the ADC are received via the pre-trigger buffer with programmable depth of up to 192 10-bit words per channel. In triggered operation, the pre-trigger buffer delays the data and allows the collection of the detector signal samples before the arrival of the trigger signal.

Figure 17: Diagram of digital signal processing chain in the SAMPA.

The pre-trigger buffer is followed by a section of several configurable pipelined digital filters for signal conditioning. The filter blocks are:

- The **baseline correction 1** subtracts a given pedestal value for a fixed time after a trigger and applies a configurable Infinite Impulse Response (IIR) filter to correct slow fluctuations of the baseline.

- The **tail cancellation** corrects long tails via a Digital Shaper, using a cascade of four fully configurable first order IIR filters which also can be used as general low-pass or band-pass filter.

- The **baseline correction 2 and 3** offer a moving average Finite Impulse Response (FIR) filter and a non-linear slope-based filter.

The SAMPA is equipped with 3.2 Gb/s output data bandwidth to extract the full raw data stream for up to 10 MSa/s. This feature is used in the TPC application. For the MCH application, data preprocessing in the SAMPA is used by applying a zero-suppression algorithm, removing all data below a threshold configurable for each channel. In addition, a cluster sum algorithm is available, where instead of delivering time and amplitude of each sample above threshold, consecutive active samples are added up to clusters in time and only the sum of the values and the time of arrival are delivered. The data are formatted for transmission in either continuous or triggered mode. A hamming code protected output buffer handles data size fluctuations and distributes the data to the activated serial links.

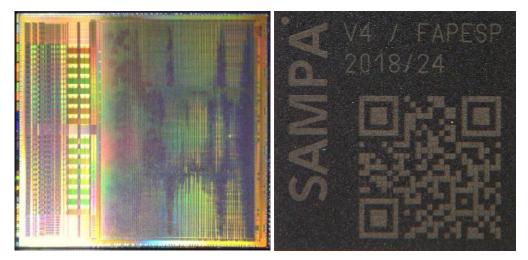

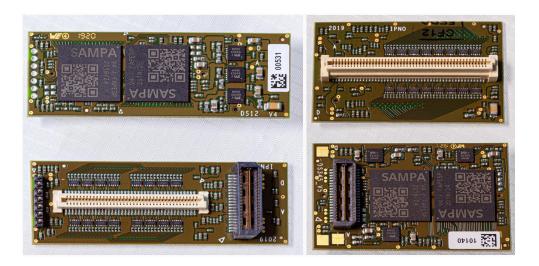

#### 2.4.4 Physical implementation and packaging

The SAMPA ASIC die is 8.9 mm wide and 9.5 mm long with 350 flip chip bond pads. As visible in the left panel of Fig. 18, only a minor part of the die is devoted to the analog circuits (left on the picture), while the largest fraction contains the digital blocks, with part of the area being occupied by the buffer memories. During the implementation, special care was taken to isolate the power domains of the different circuits. There are five different power domains: CSA, Shaper and Output Buffer, ADC, core digital logic and SLVS IO drivers. The SAMPA features a 372 ball 15 mm  $\times$  15 mm, 1.2 mm thick, Thin Fine-pitch Ball Grid Array (TFBGA) package with 0.65 mm ball pitch in order to be compatible with the MCH integration requirements. The high number of available balls allowed multiple connections to VDD and GND pads, reducing the inductive and resistive loss. The package includes filtering capacitors for ADC power connections and for on-chip ADC reference voltages. A QR-code on the SAMPA package (right panel in Fig. 18) encodes the wafer lot-ID and a unique chip serial number, allowing the identification and tracking of each ASIC.

Figure 18: SAMPA bare die (left) and TFBGA packaged chip (right).

#### 2.4.5 SAMPA performance and tests

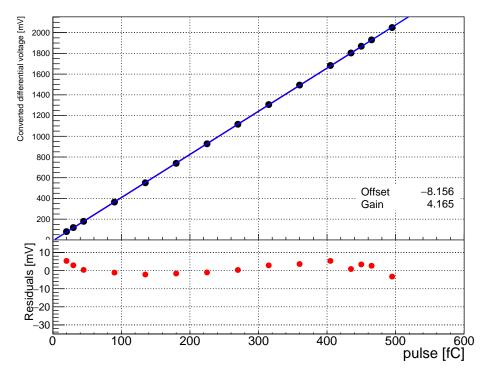

The main specifications and performance of the SAMPA are listed in Tab. 2 above. Figure 19 shows the response curve for the 4 mV/fC gain setting.

Figure 19: Example response curve for 4 mV/fC configuration.

Robustness measurements of the CSA against saturation in case of multiple consecutive signals were performed, showing that an average current of at least 30 nA can be sustained for 60  $\mu$ s without significant baseline shift, indicating that the SAMPA can stand this charge rate indefinitely.

The SAMPA functionality was verified successfully against the highest expected radiation load of 2.1 kRad. Robustness of the SAMPA against single event upsets and single event latchups for an expected maximum flux of high-energy hadrons of  $3.4 \text{ kHz/cm}^2$  has been verified. An upper limit for the SEL cross section of  $10^{-7} \text{cm}^2$  for ions with a linear energy transfer of 16 MeV cm<sup>2</sup> mg<sup>-1</sup> has been measured.

80000 SAMPAs have been tested using a robotic test system to verify the functionality of the digital blocks and that the output baseline, noise, gain and peaking time are in a narrow intervals around the nominal values. The SAMPA mass production yield was 79.6%. A breakdown of the rate of different kinds of failures can be found in Table 14 of [15].

#### **3** Detector systems

In the following subsections, each of the ALICE detector systems is presented, with emphasis on the upgrades that were installed during LHC Long Shutdown 2. Each system is presented in a separate subsection, starting from the inner tracking system, the muon forward tracker and the time projection chambers, which have undergone the most significant changes.

#### 3.1 Coordinate system

The gloabel reference coordinate system used in ALICE is a right handed system with the z axis point along the beam line, in the direction away from the muon arm, the y-axis pointing vertically up, and the x axis pointing horizontally towards the center of the LHC. The nominal interaction point is the origin of the coordinate system. The two sides of the detector along the beam axis are refferred to as the C side, where the muon arm is positioned, and the A side, where FV0 is positioned.

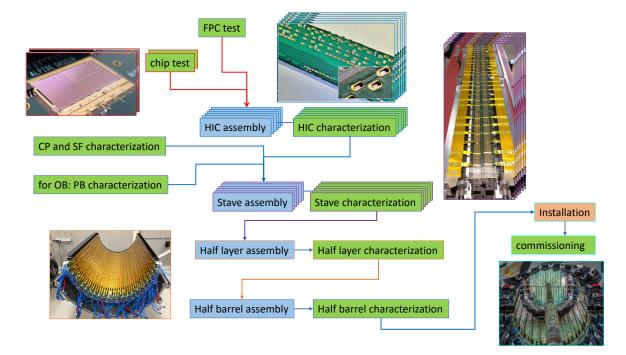

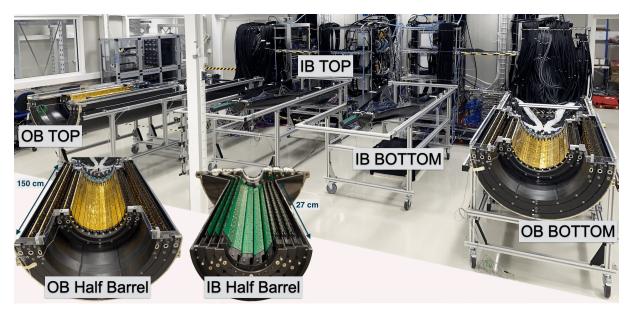

#### 3.2 Inner Tracking System

The new Inner Tracking System (ITS2) [16] uses the ALPIDE sensor (described in Sec. 2.3) and represents the largest-scale application of Monolithic Active Pixel Sensors (MAPS) in a high-energy physics experiment. The main goal of the ITS upgrade is to improve the precision of the reconstruction of the primary vertex as well as of decay vertices originating from heavy-flavour hadrons, and the performance in the detection of low- $p_T$  particles. Additionally, readout rates of 50 kHz in Pb–Pb and 400 kHz in pp collisions are required. In order to achieve this performance, the following key improvements were made in comparison with the previous ITS:

- Granularity increased for all layers with pixel sensors with a cell size of  $29.24 \,\mu m \times 26.88 \,\mu m$ . The number of layers for the inner barrel was increased from two to three, raising the total number of layers from six to seven.

- New beam pipe with a central beryllium section with an outer radius reduced from 28 mm to 18 mm (see Chapter 4).

- Innermost detector layer moved closer to the interaction point, from 39 mm to 22.4 mm.

- Material budget reduced to 0.36%  $X_0$  per layer for the innermost layers and limited to 1.10%  $X_0$  per layer for the outer layers.

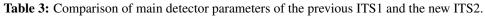

Table 3 reports a list of main parameters of the old ITS1, used in Runs 1 and 2, and of the new ITS2. The new design improves the tracking efficiency and momentum resolution at low  $p_T$  as well as the impact-parameter resolution by a factor of three and five in the  $r\varphi$ - and z-coordinate, respectively, at a  $p_T$  of 500 MeV/*c* [1].